Patents

Literature

32 results about "Logical consequence" patented technology

Efficacy Topic

Property

Owner

Technical Advancement

Application Domain

Technology Topic

Technology Field Word

Patent Country/Region

Patent Type

Patent Status

Application Year

Inventor

Logical consequence (also entailment) is a fundamental concept in logic, which describes the relationship between statements that hold true when one statement logically follows from one or more statements. A valid logical argument is one in which the conclusion is entailed by the premises, because the conclusion is the consequence of the premises. The philosophical analysis of logical consequence involves the questions: In what sense does a conclusion follow from its premises? and What does it mean for a conclusion to be a consequence of premises?

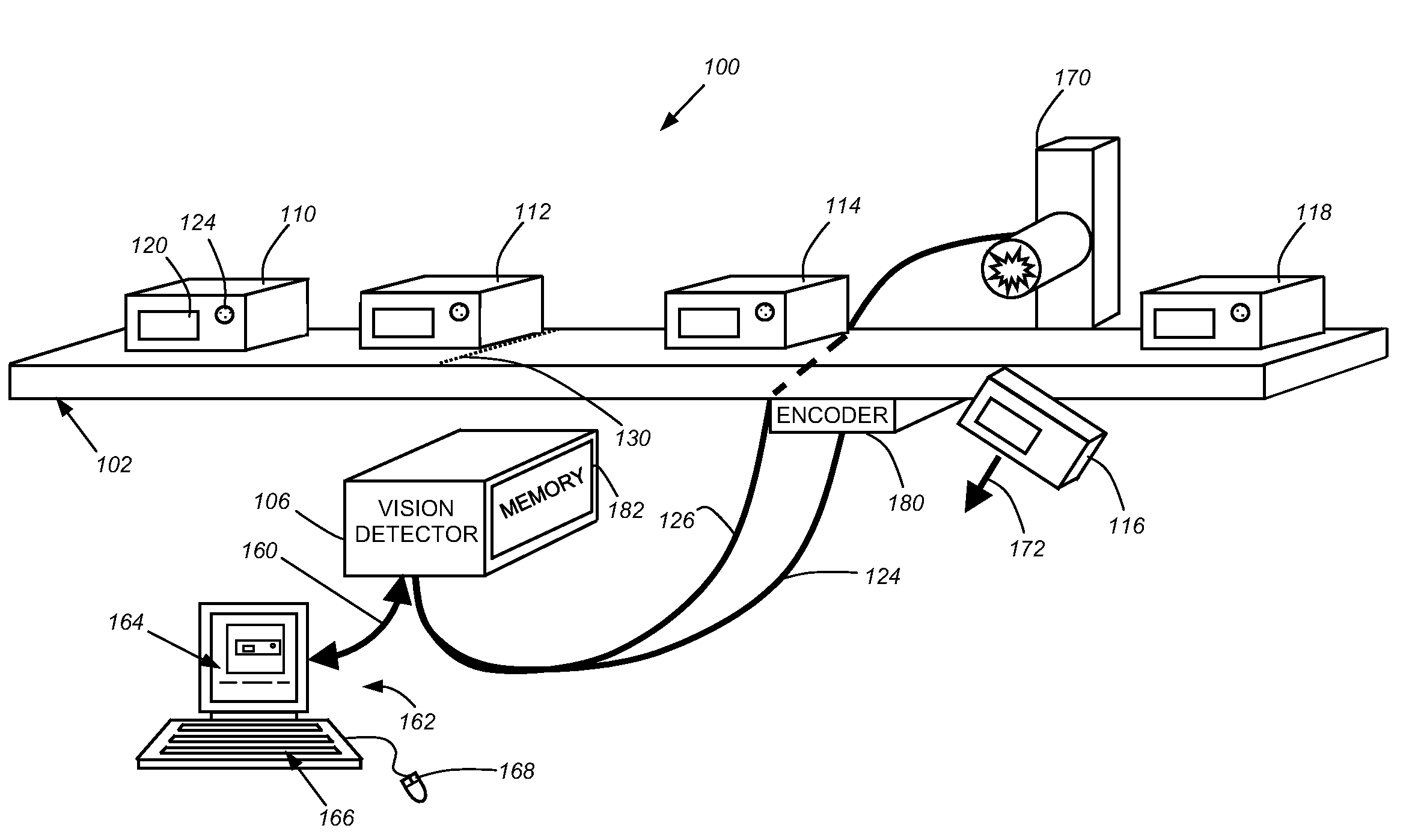

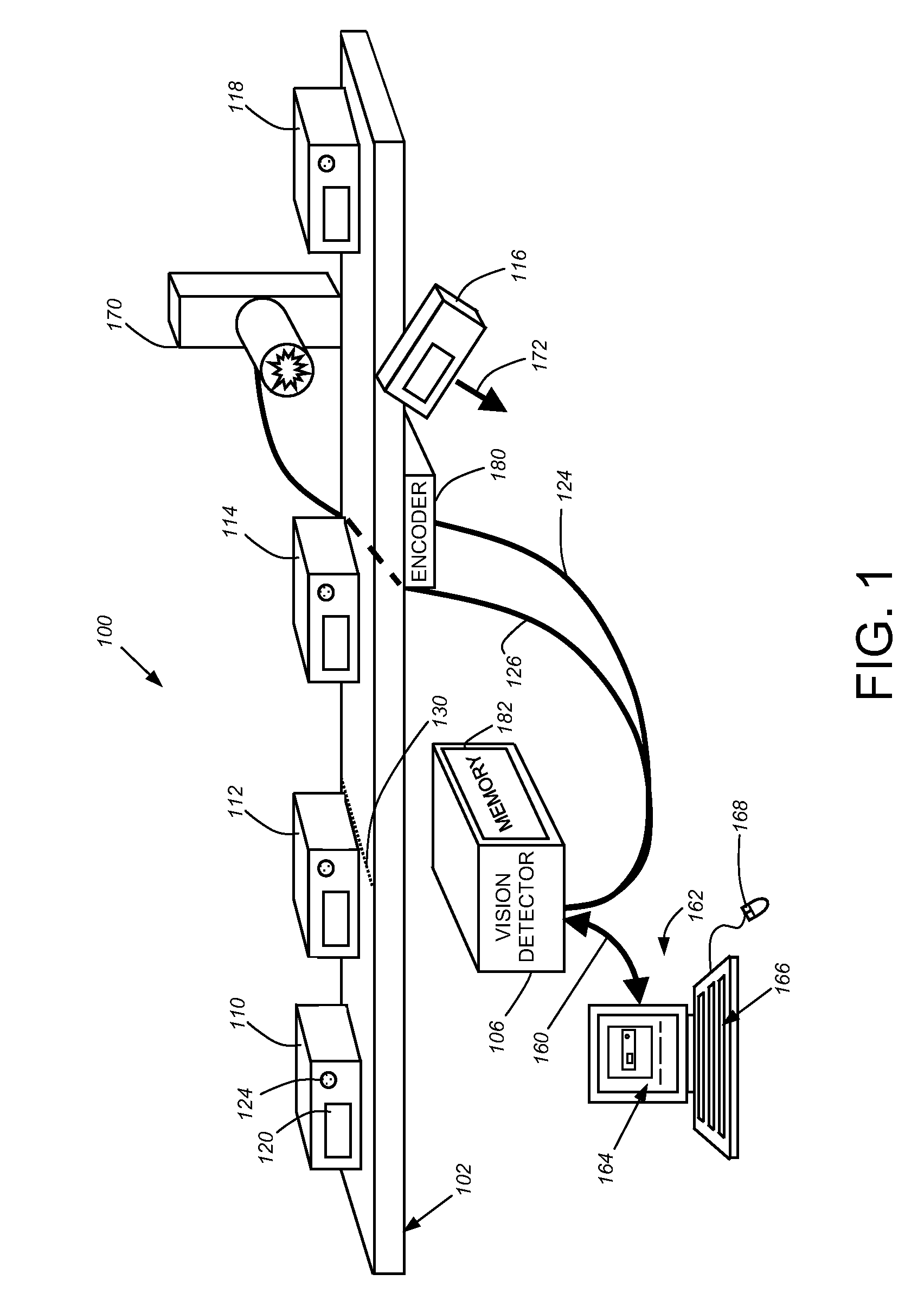

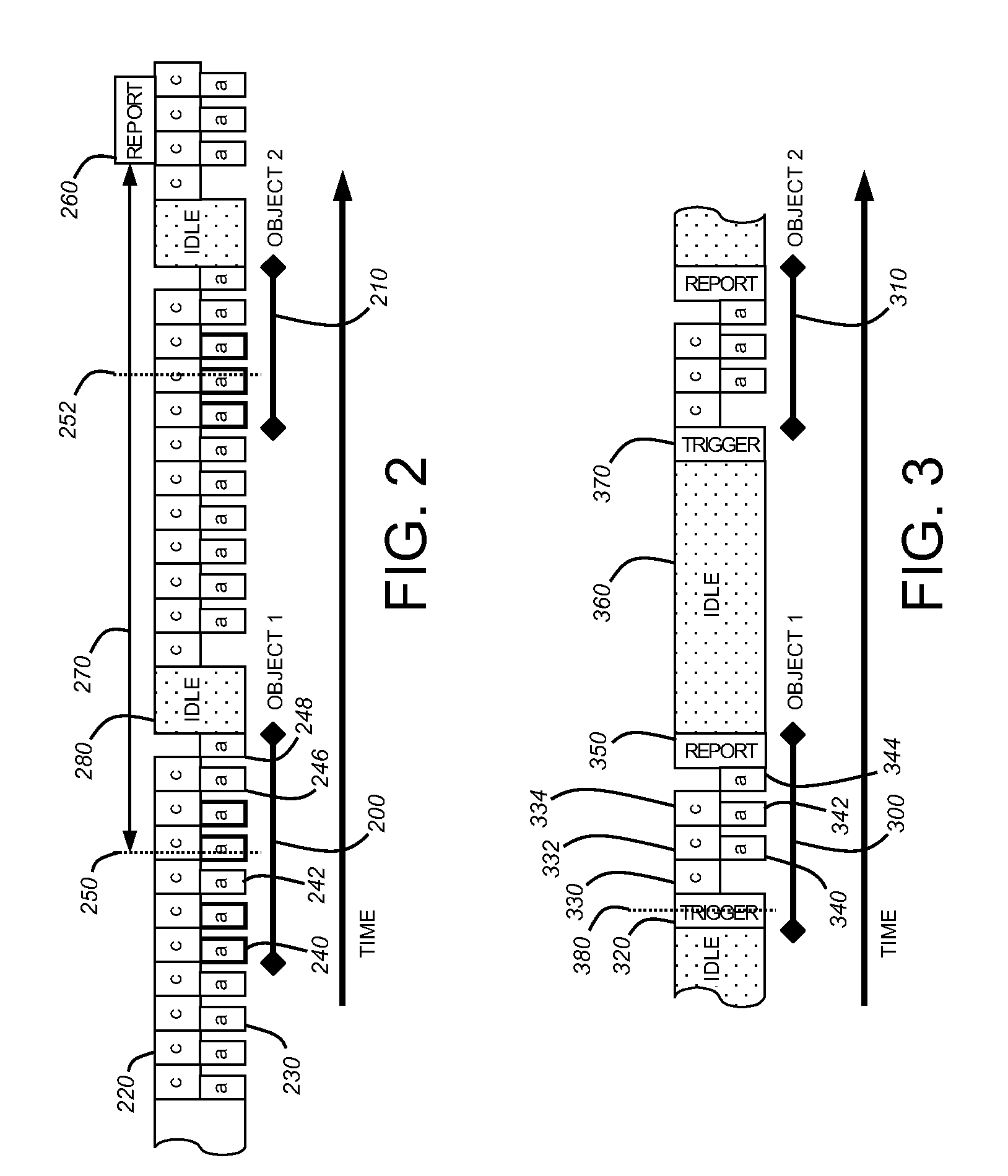

Human-machine-interface and method for manipulating data in a machine vision system

InactiveUS20070146491A1Easy to set upIncrease speedTelevision system detailsImage analysisHuman–machine interfaceThumbnail

This invention provides a Graphical User Interface (GUI) that operates in connection with a machine vision detector or other machine vision system, which provides a highly intuitive and industrial machine-like appearance and layout. The GUI includes a centralized image frame window surrounded by panes having buttons and specific interface components that the user employs in each step of a machine vision system set up and run procedure. One pane allows the user to view and manipulate a recorded filmstrip of image thumbnails taken in a sequence, and provides the filmstrip with specialized highlighting (colors or patterns) that indicate useful information about the underlying images. The system is set up and run are using a sequential series of buttons or switches that are activated by the user in turn to perform each of the steps needed to connect to a vision system, train the system to recognize or detect objects / parts, configure the logic that is used to handle recognition / detection signals, set up system outputs from the system based upon the logical results, and finally, run the programmed system in real time. The programming of logic is performed using a programming window that includes a ladder logic arrangement. A thumbnail window is provided on the programming window in which an image from a filmstrip is displayed, focusing upon the locations of the image (and underlying viewed object / part) in which the selected contact element is provided.

Owner:COGNEX CORP

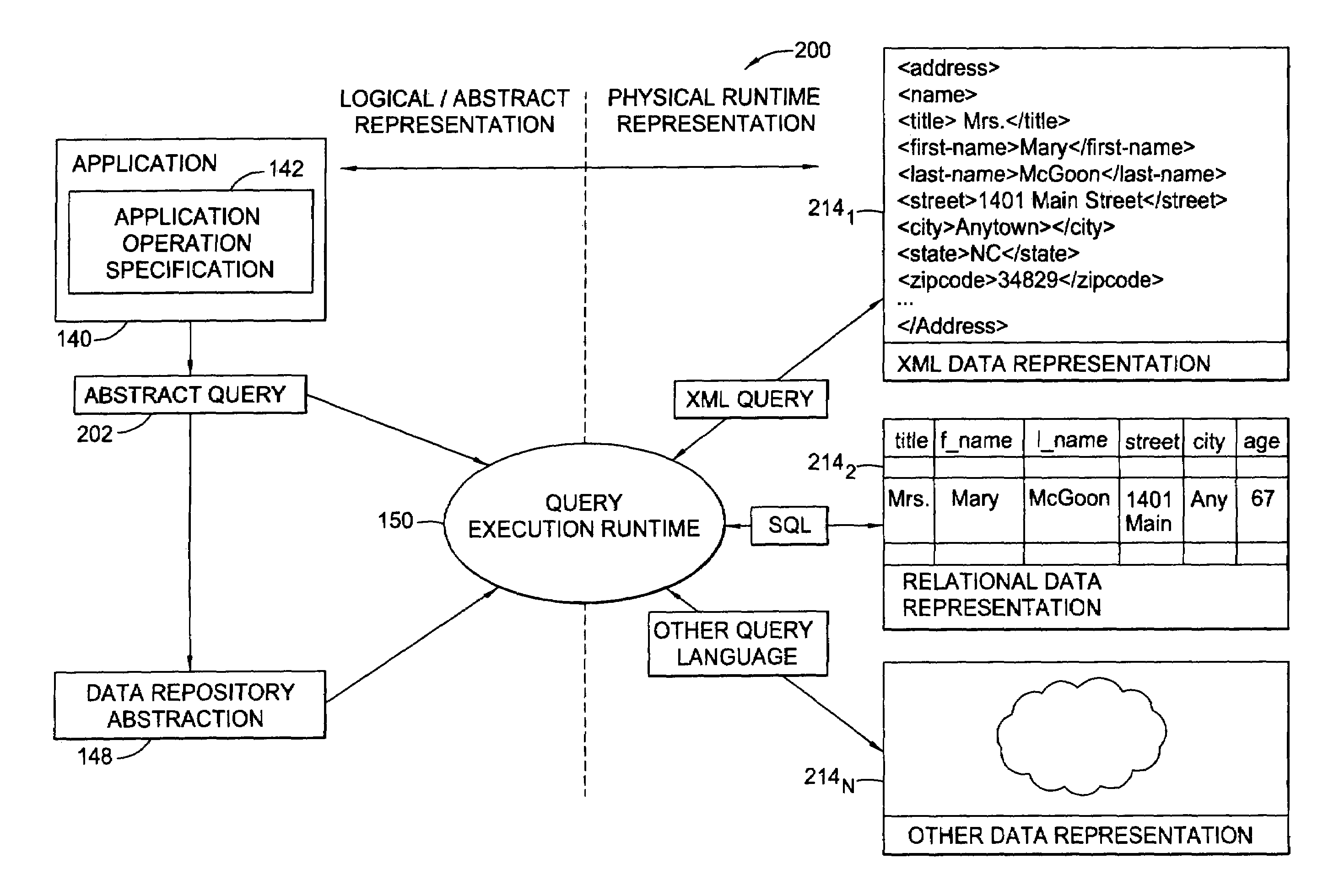

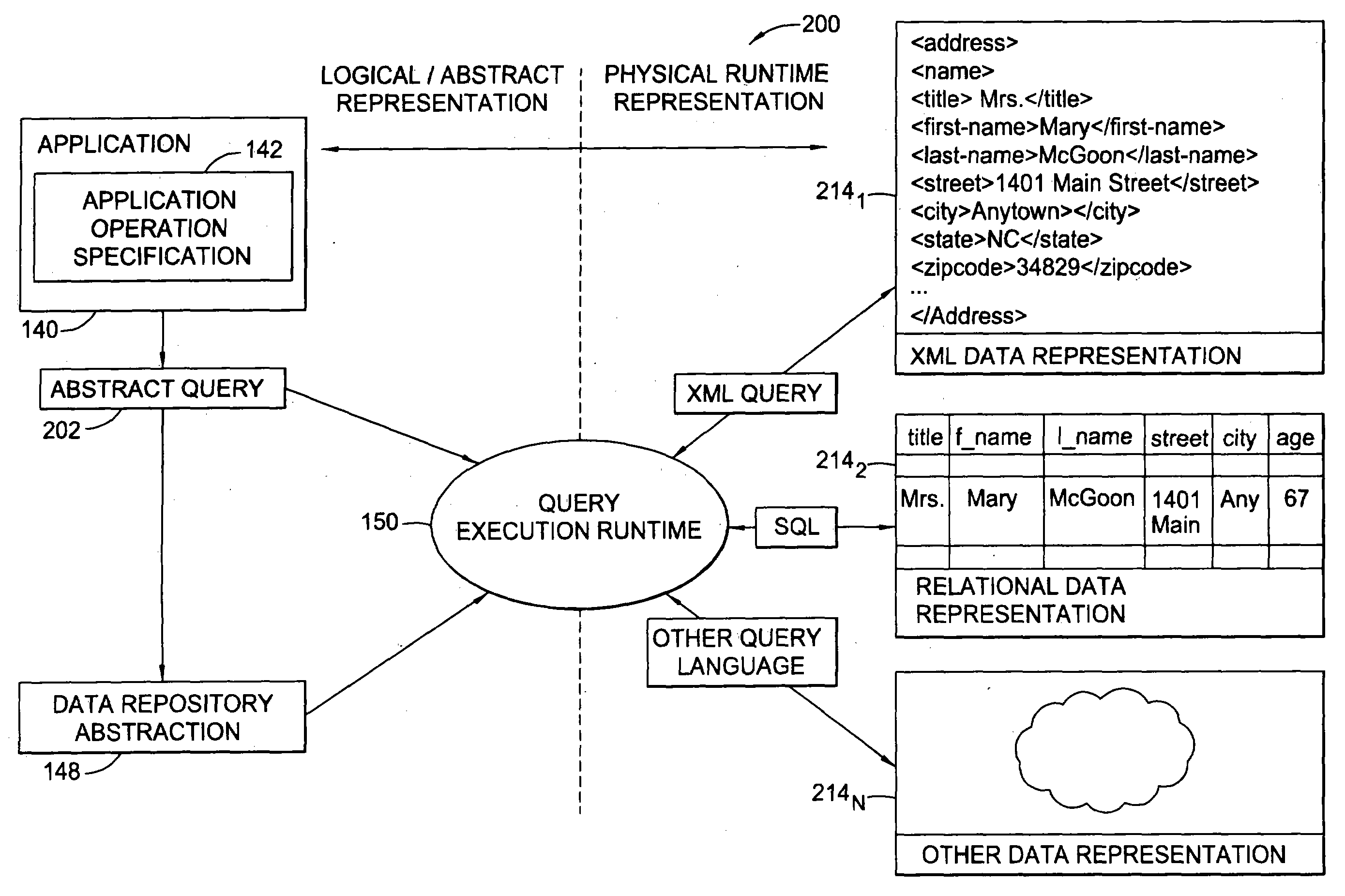

Abstract data linking and joining interface

InactiveUS7085757B2Data processing applicationsDigital data processing detailsGraphicsGraphical user interface

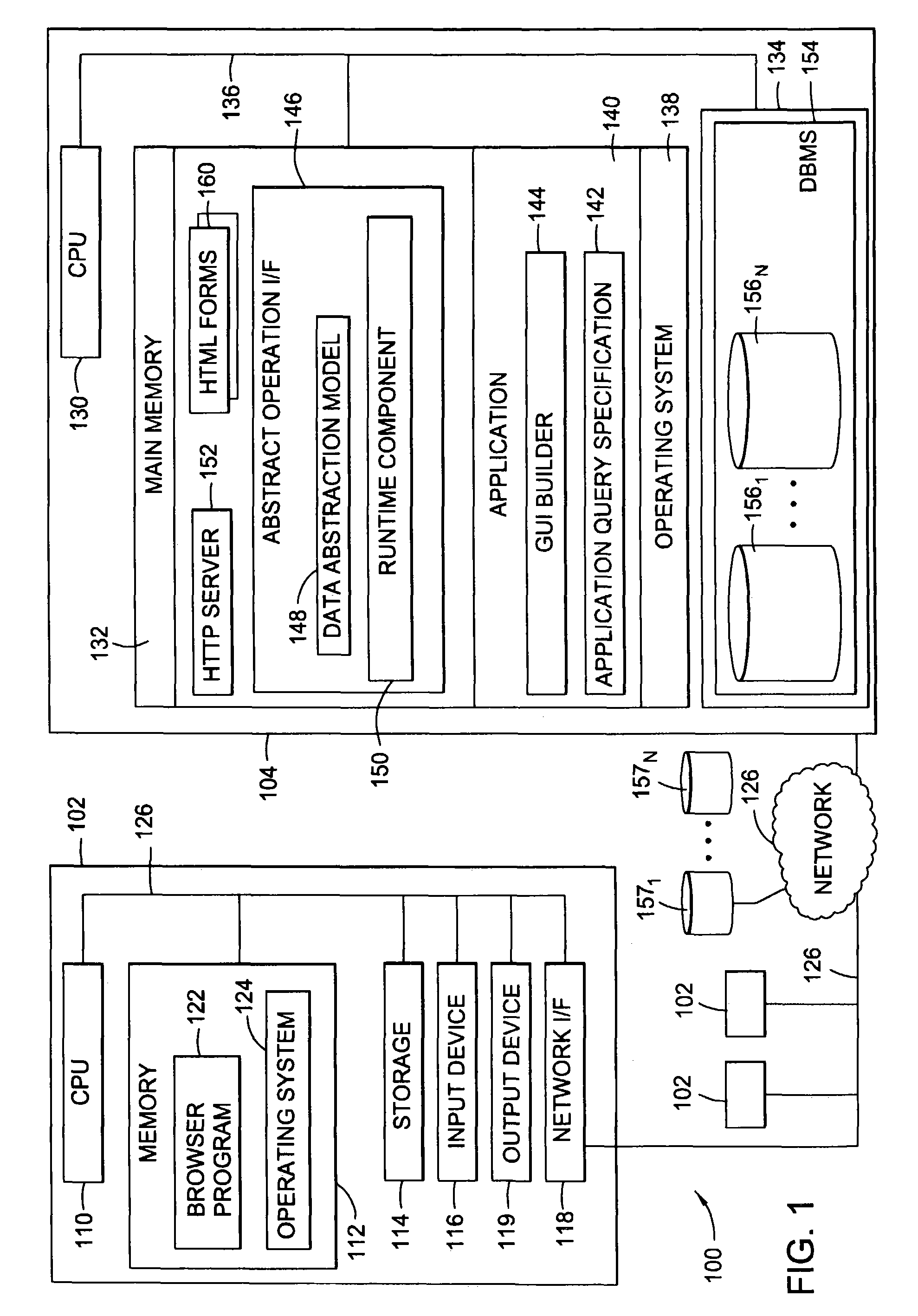

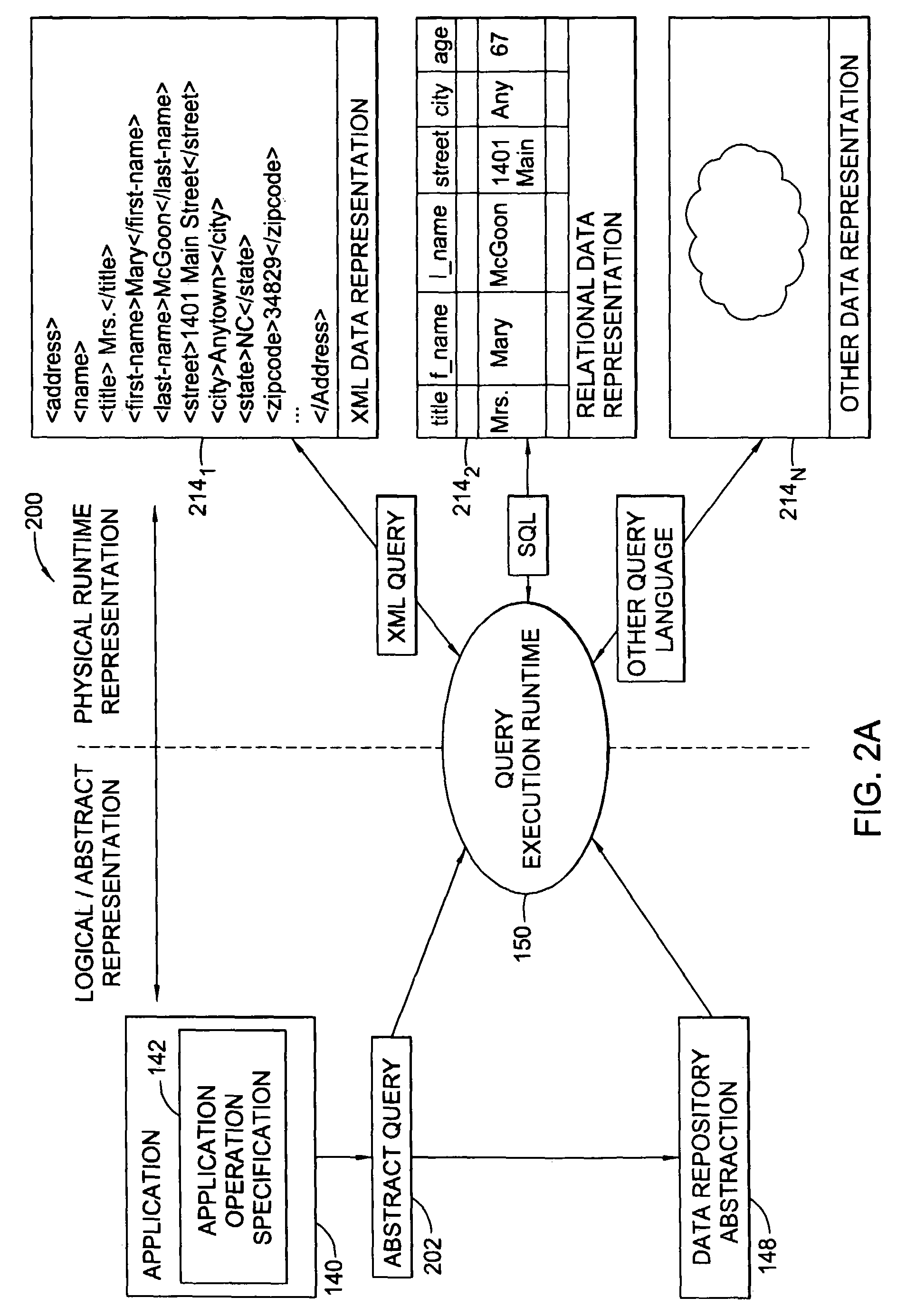

A method, apparatus and article of manufacture provide a user interface allowing user selection and arrangement of result fields selected, in one embodiment, from a logical model. In one embodiment, the user interface is a graphical user interface and comprises input cells for user-selected logical result fields. The cells are arranged to define a geometric relationship between logical result fields which dictates the combinatorial statement type by which the logical result fields in the cells are related in a query.

Owner:INT BUSINESS MASCH CORP

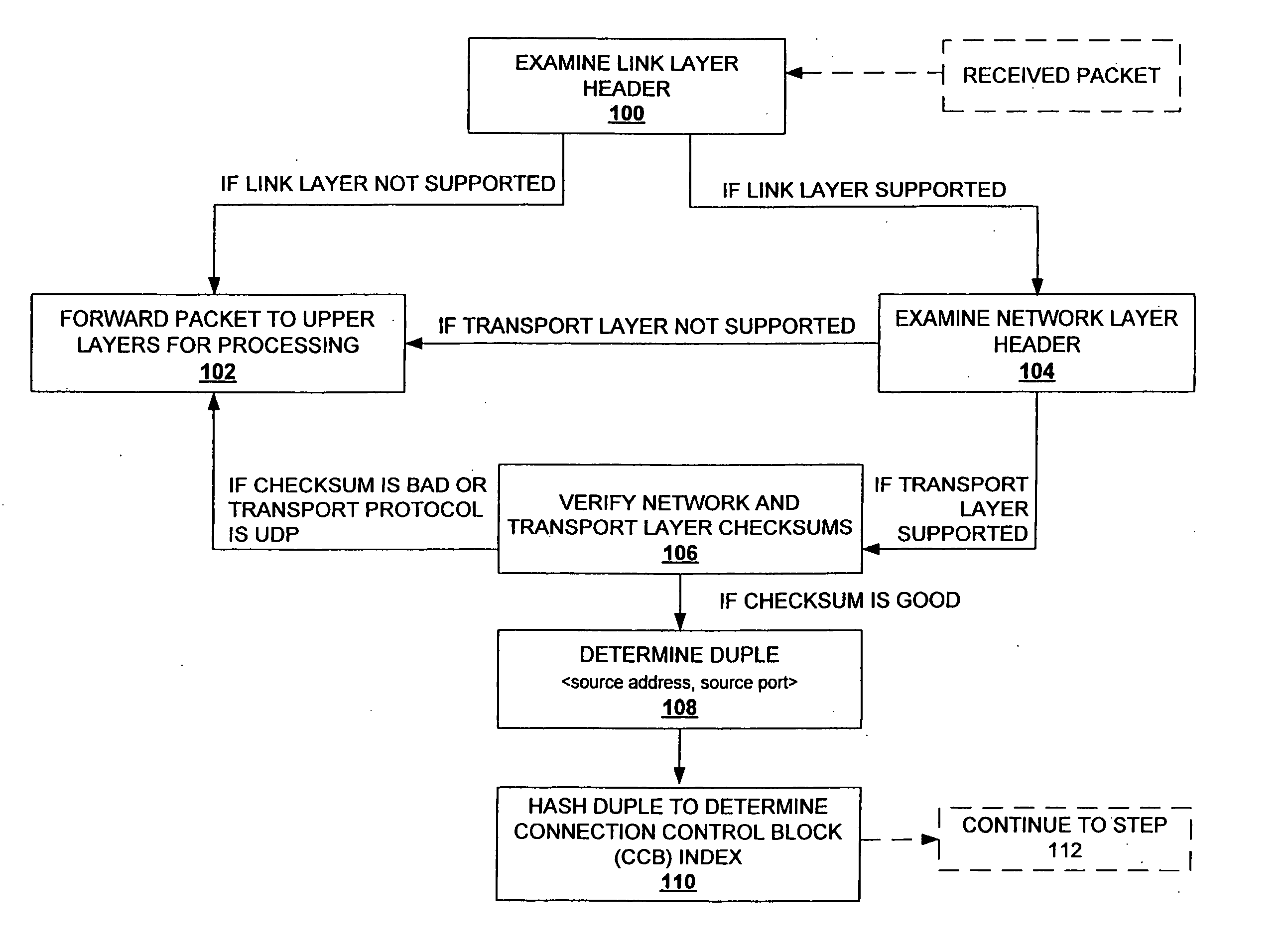

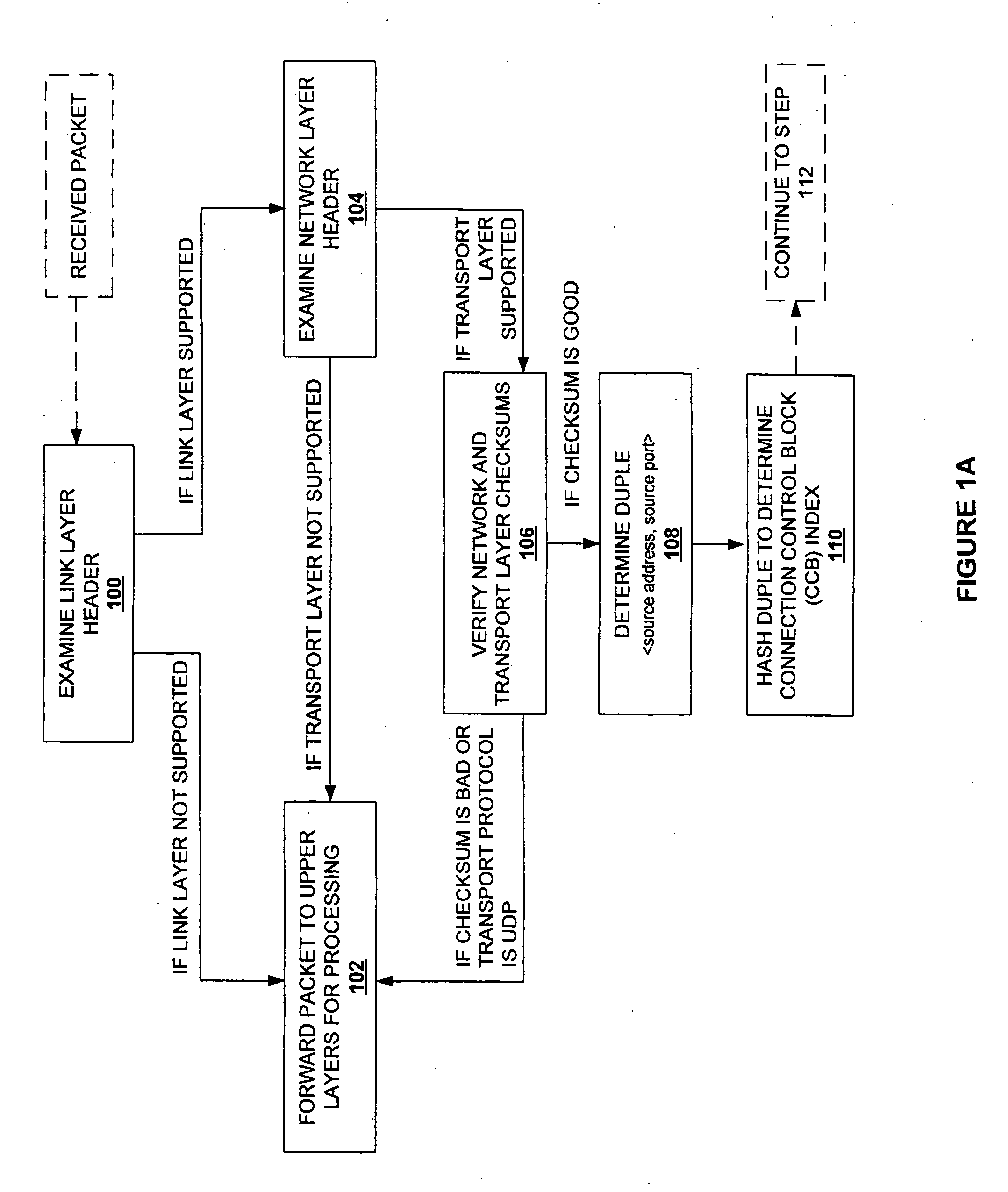

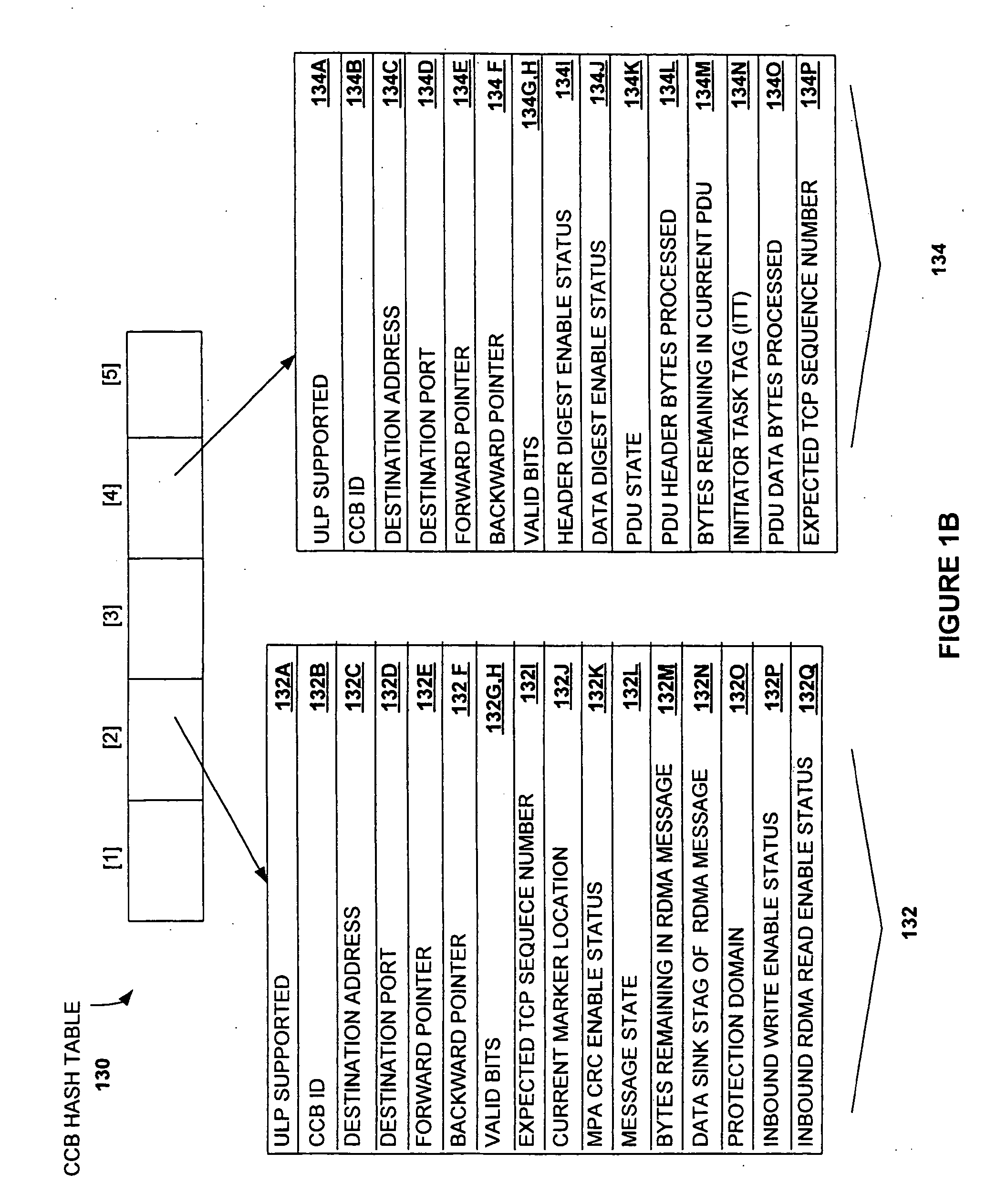

Method and system for providing direct data placement support

InactiveUS20060034283A1Reduction of CPU processing overheadReduced space requirementsTime-division multiplexData switching by path configurationWire speedZero-copy

A system and method for reducing the overhead associated with direct data placement is provided. Processing time overhead is reduced by implementing packet-processing logic in hardware. Storage space overhead is reduced by combining results of hardware-based packet-processing logic with ULP software support; parameters relevant to direct data placement are extracted during packet-processing and provided to a control structure instantiation. Subsequently, payload data received at a network adapter is directly placed in memory in accordance with parameters previously stored in a control structure. Additionally, packet-processing in hardware reduces interrupt overhead by issuing system interrupts in conjunction with packet boundaries. In this manner, wire-speed direct data placement is approached, zero copy is achieved, and per byte overhead is reduced with respect to the amount of data transferred over an individual network connection. Movement of ULP data between application-layer program memories is thereby accelerated without a fully offloaded TCP protocol stack implementation.

Owner:IBM CORP

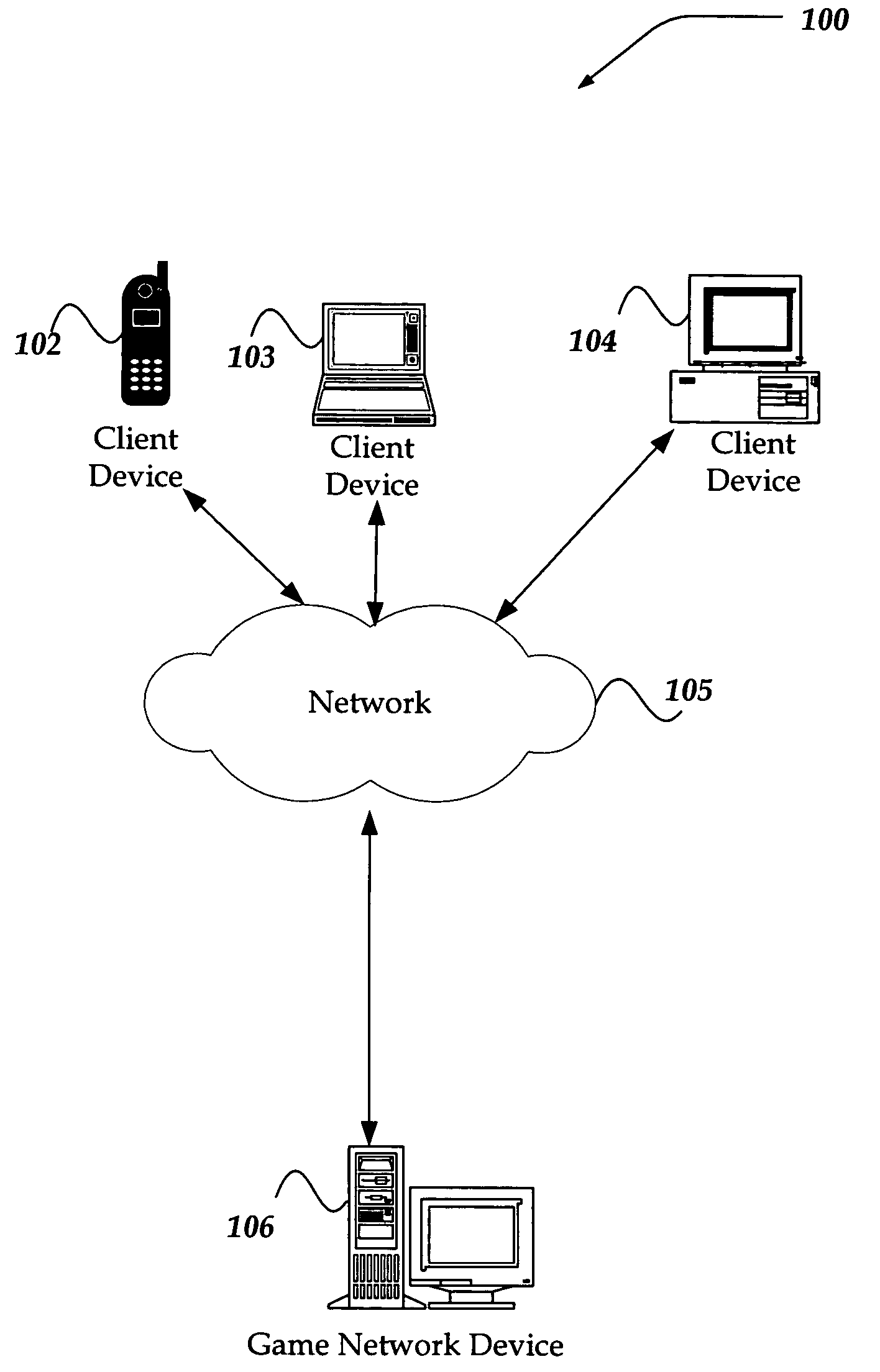

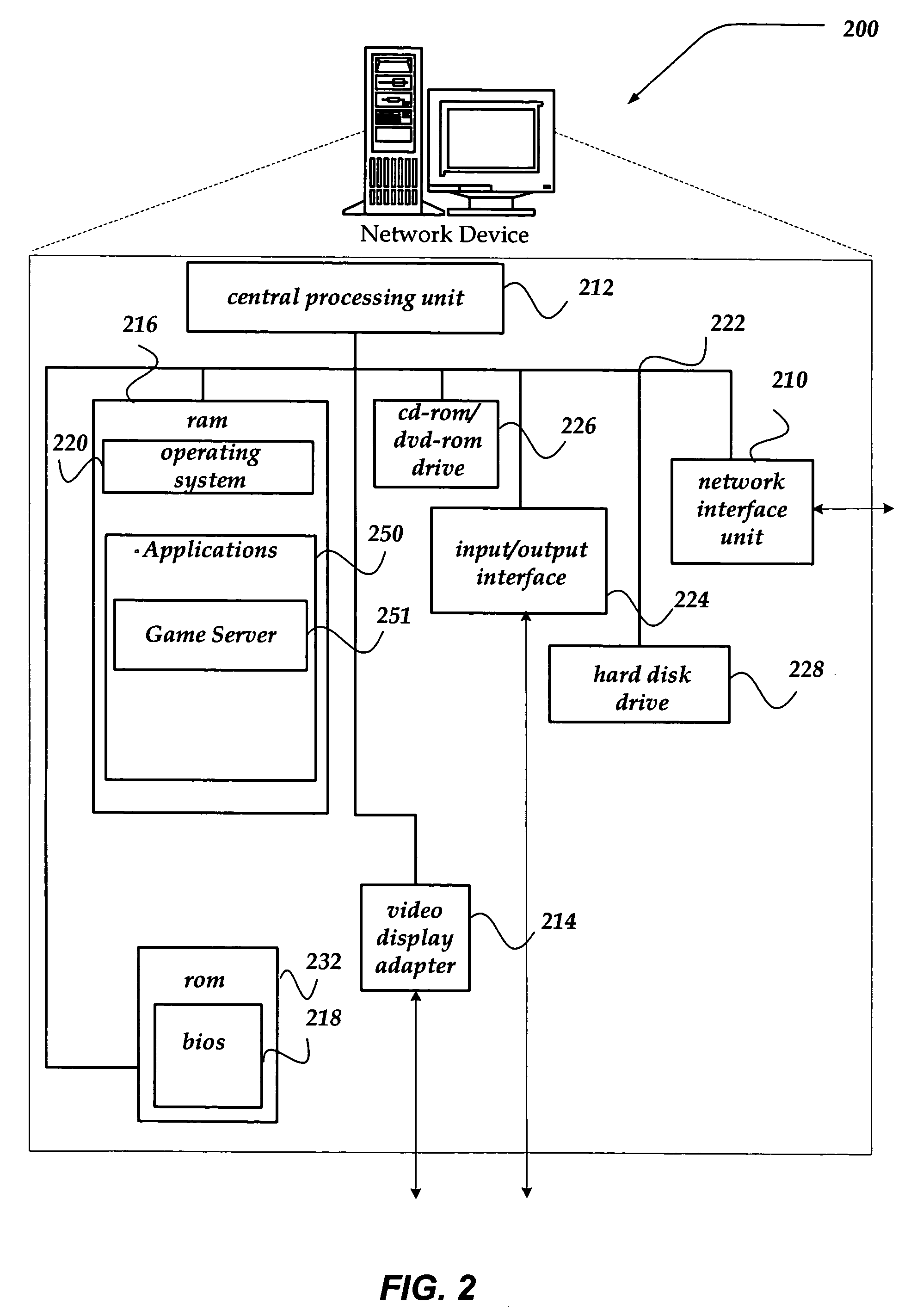

Method and system for synchronizing a game system with a physics system

A system, apparatus, and method are directed to synchronizing a result from a physics engine with a result from a game logic. Synchronization of results may be achieved by employing an arbitration rule to determine which result may dictate an overall game action. The game logic is enabled to determine a result for a game logic entity. The physics engine determines a result for an associated physics proxy. Upon determination of the result for the game logic entity, the physics engine determines the result for the associated physics proxy. If it is determined from the physics result that an interaction between objects occurred, the physics result is employed to synchronize the game logic result; otherwise, the result for the game logic entity is employed to drive the result for the physics proxy.

Owner:VALVE

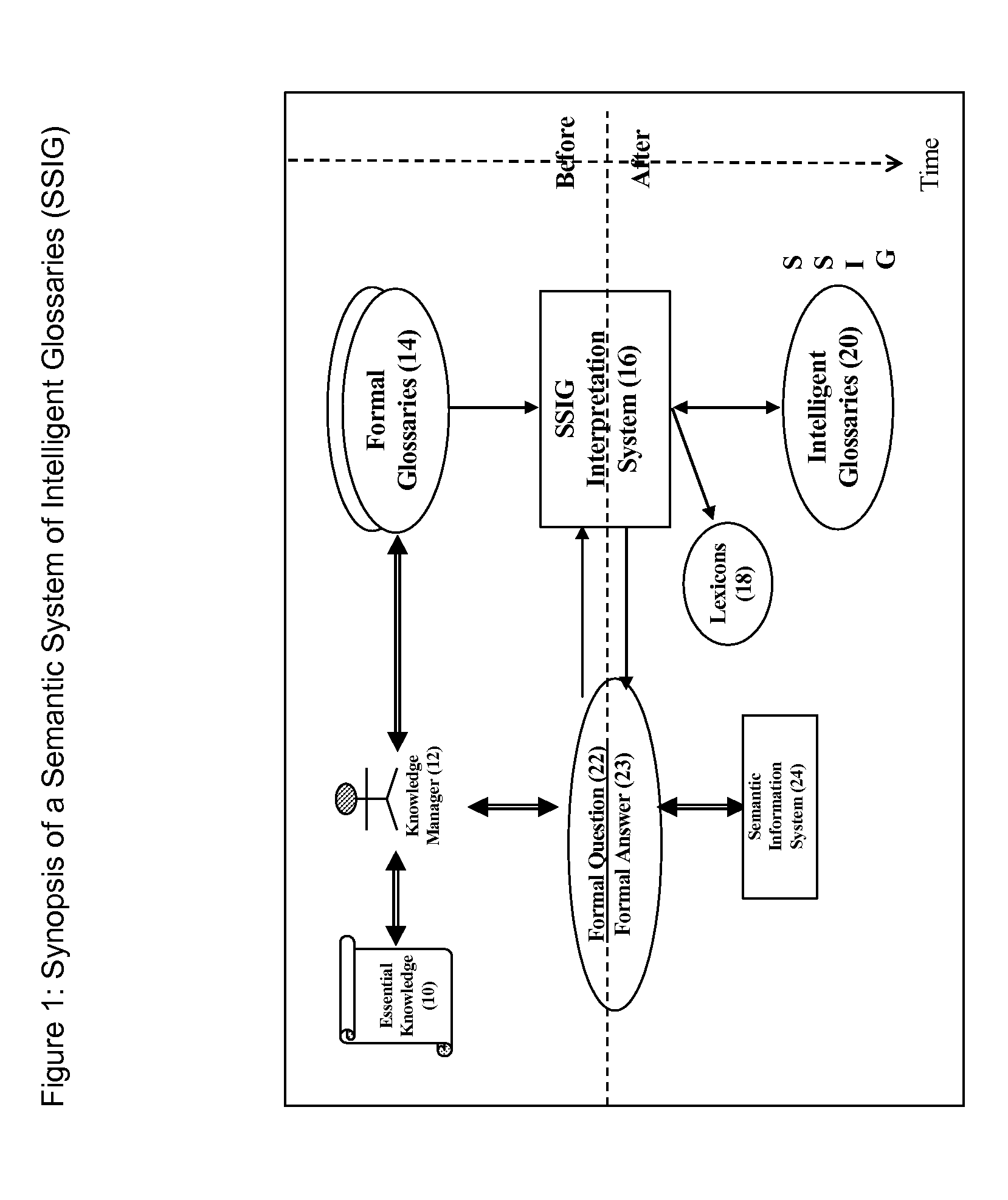

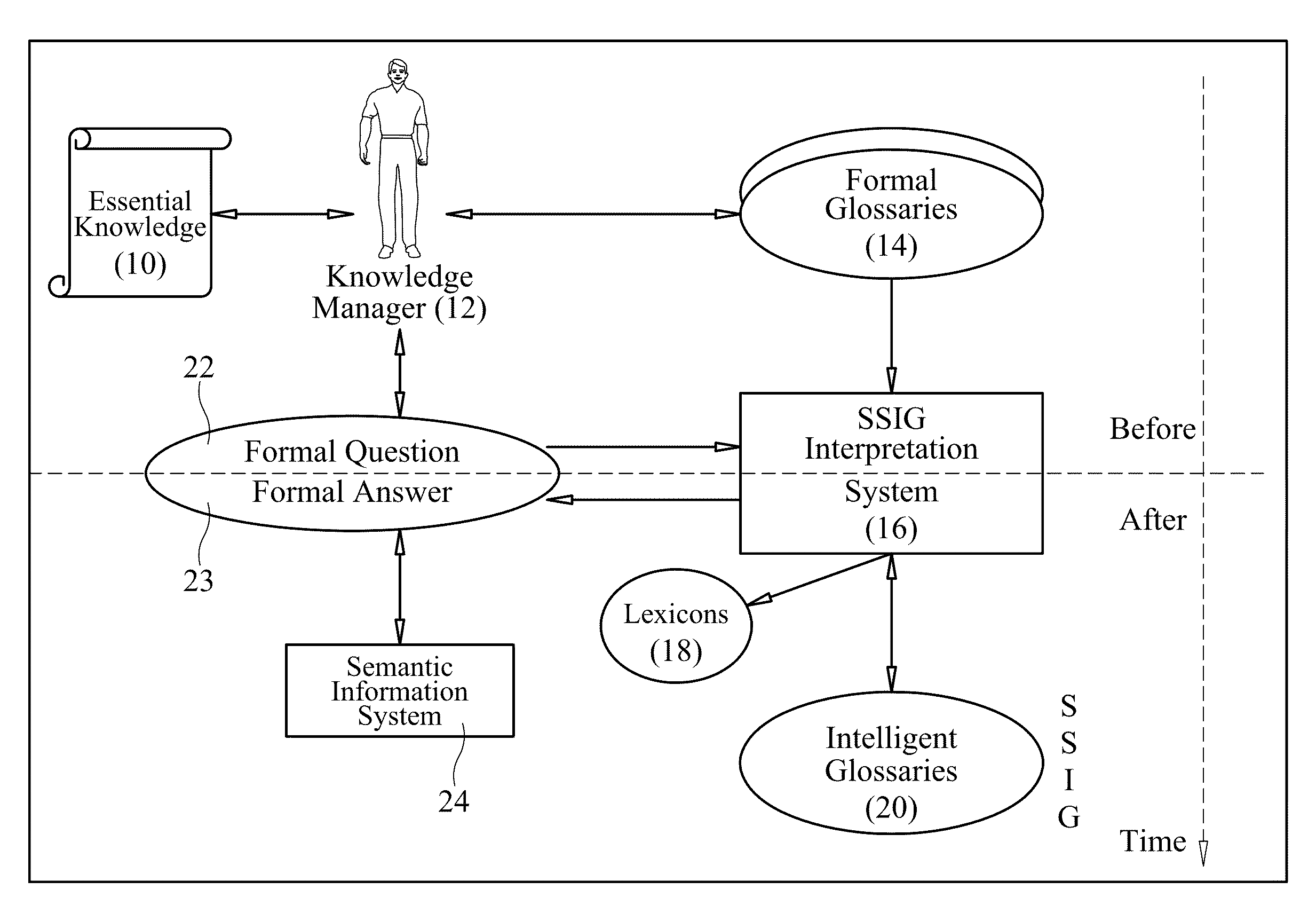

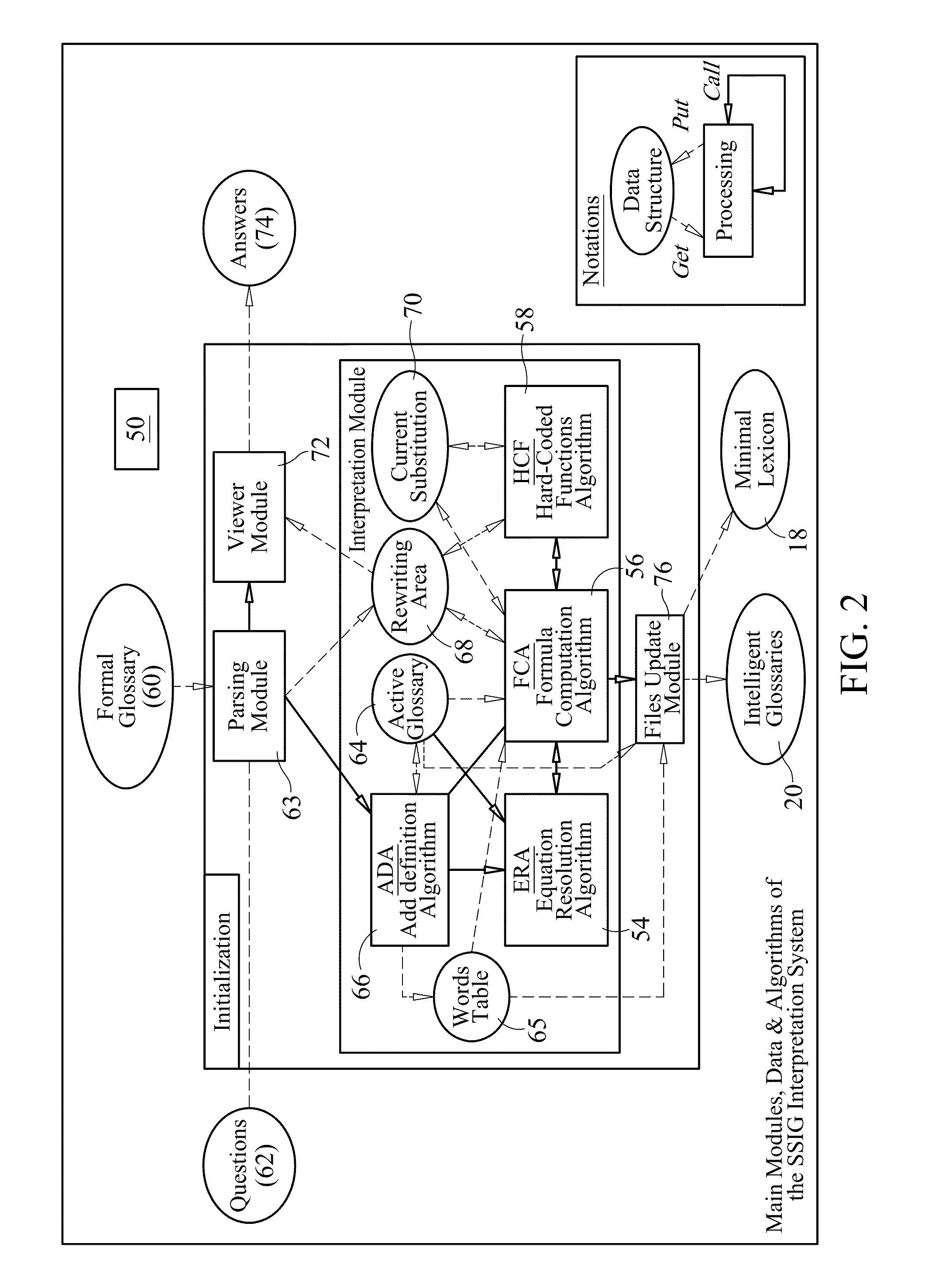

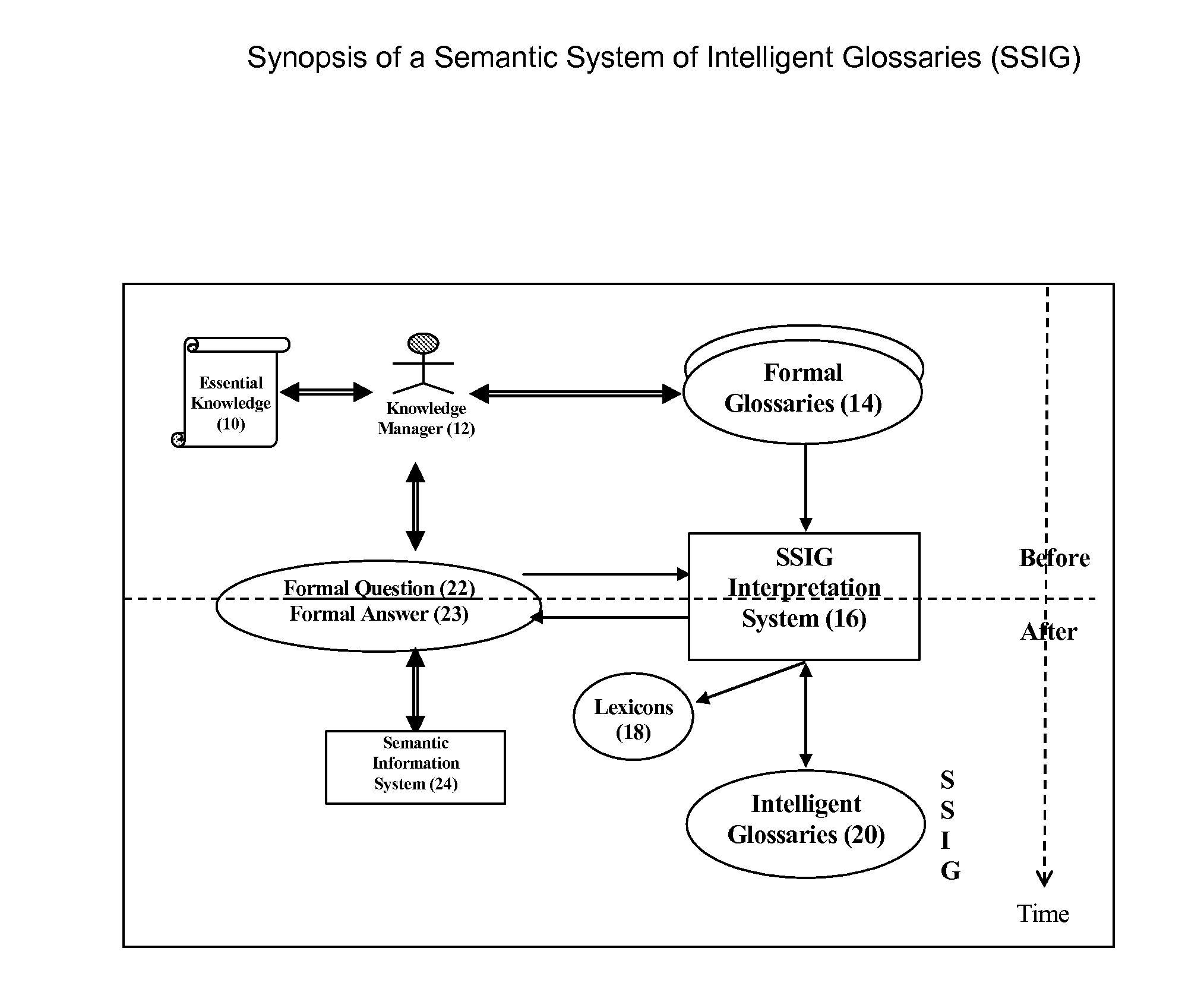

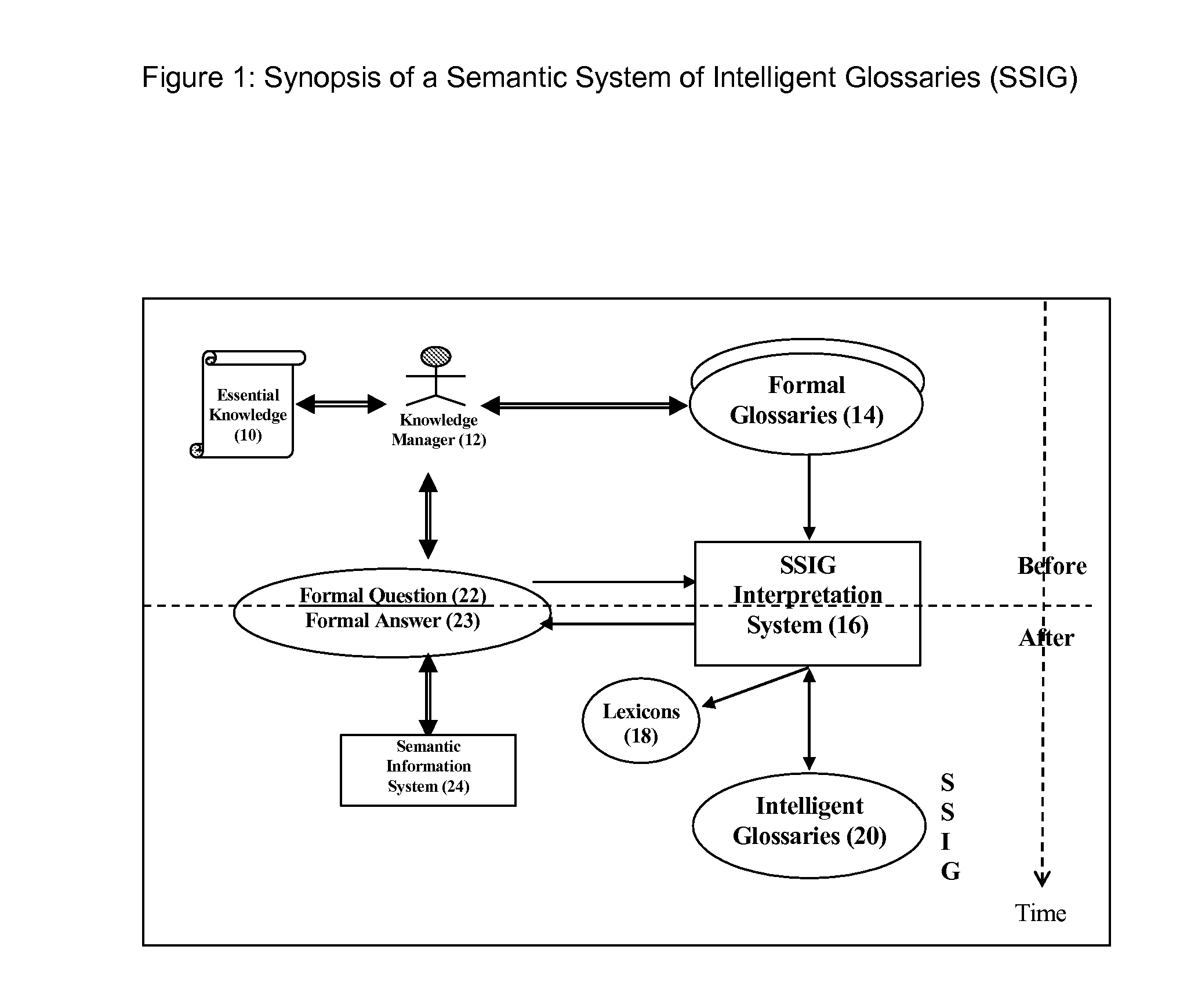

Methods and systems for interpreting text using intelligent glossaries

A computer implemented method and systems used to create and interpret a set of formal glossaries which refer one to the other and are intended to define precisely the terminology of a field of endeavor. Such glossaries are known as intelligent, in the sense that they allow machines to make deductions, with interaction of human actors. Once a word is defined in an intelligent glossary, all the logical consequences of the use of that word in a formal and well-formed sentence are computable. The process includes a question and answer mechanism, which applies the definitions contained in the intelligent glossaries to a given formal sentence. The methods may be applied in the development of knowledge management methods and tools that are based on semantics; for example: modeling of essential knowledge in the field based on the relevant semantics; and computer-aided human-reasoning.

Owner:AEBIS

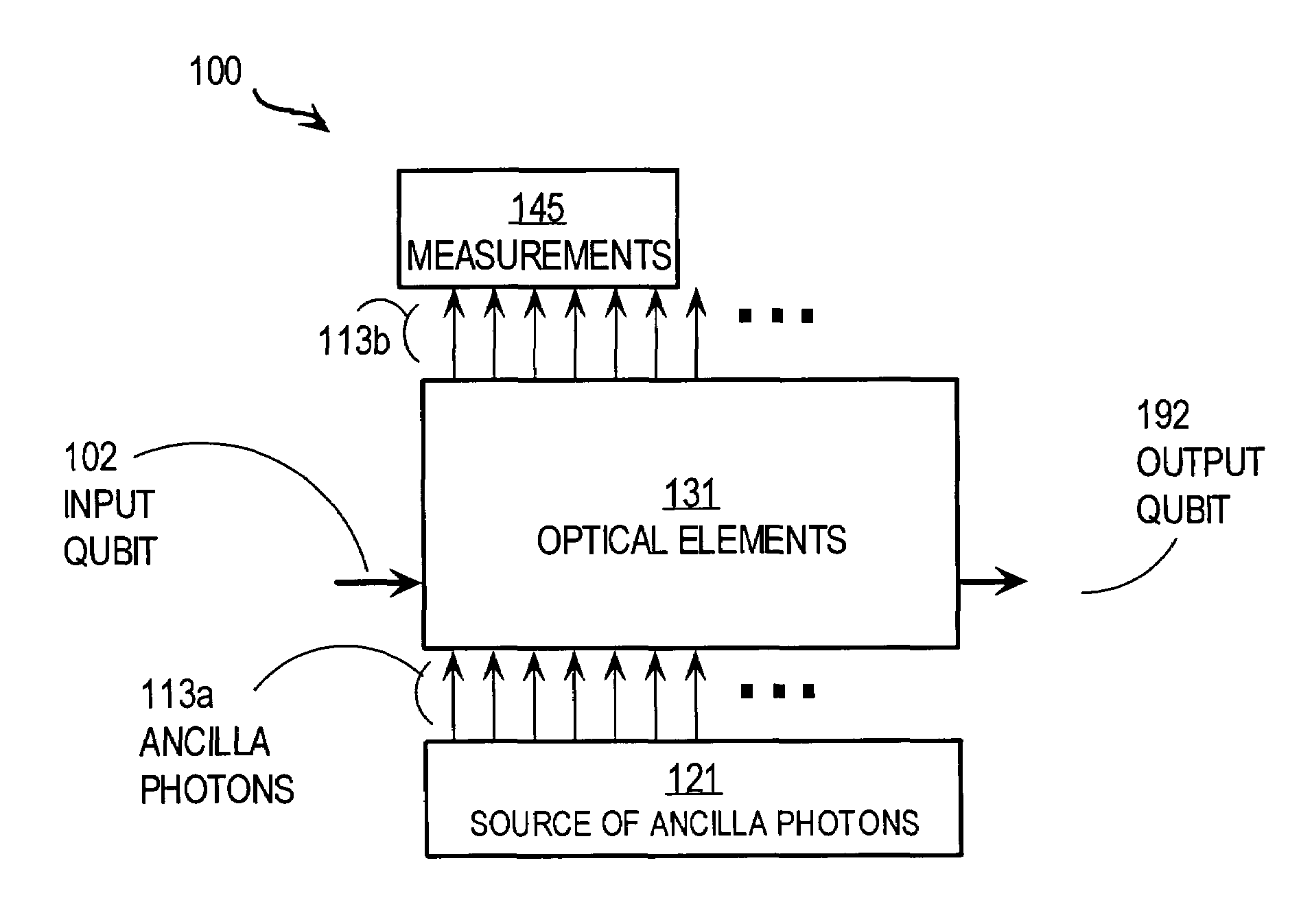

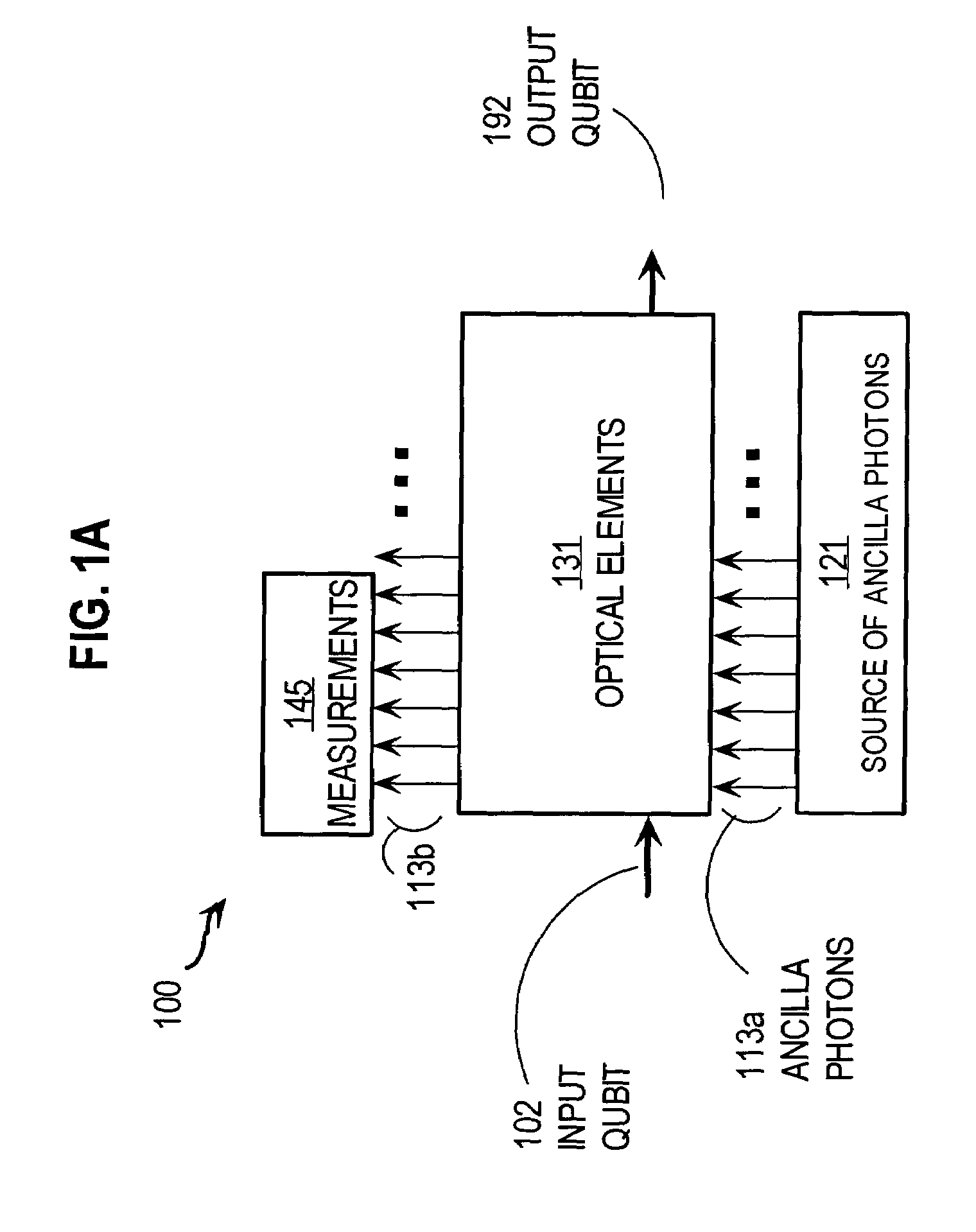

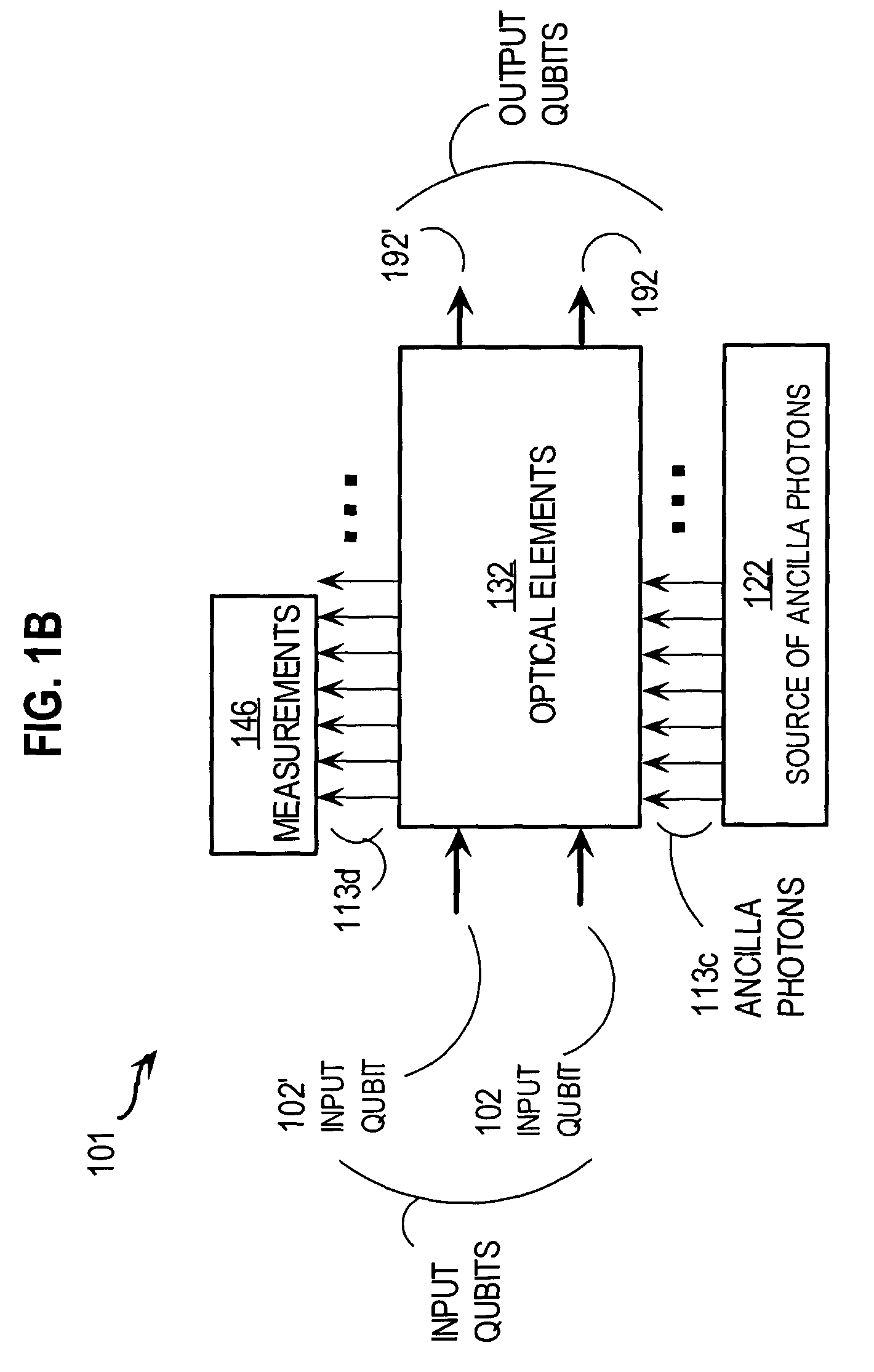

Techniques for high fidelity quantum teleportation and computing

ActiveUS7006267B2Sufficient error reductionIncrease opportunitiesQuantum computersKey distribution for secure communicationQuantum teleportationQuantum logic

Owner:THE JOHN HOPKINS UNIV SCHOOL OF MEDICINE

Abstract data linking and joining interface

InactiveUS20050010557A1Data processing applicationsOther databases queryingGraphicsGraphical user interface

A method, apparatus and article of manufacture provide a user interface allowing user selection and arrangement of result fields selected, in one embodiment, from a logical model. In one embodiment, the user interface is a graphical user interface and comprises input cells for user-selected logical result fields. The cells are arranged to define a geometric relationship between logical result fields which dictates the combinatorial statement type by which the logical result fields in the cells are related in a query.

Owner:IBM CORP

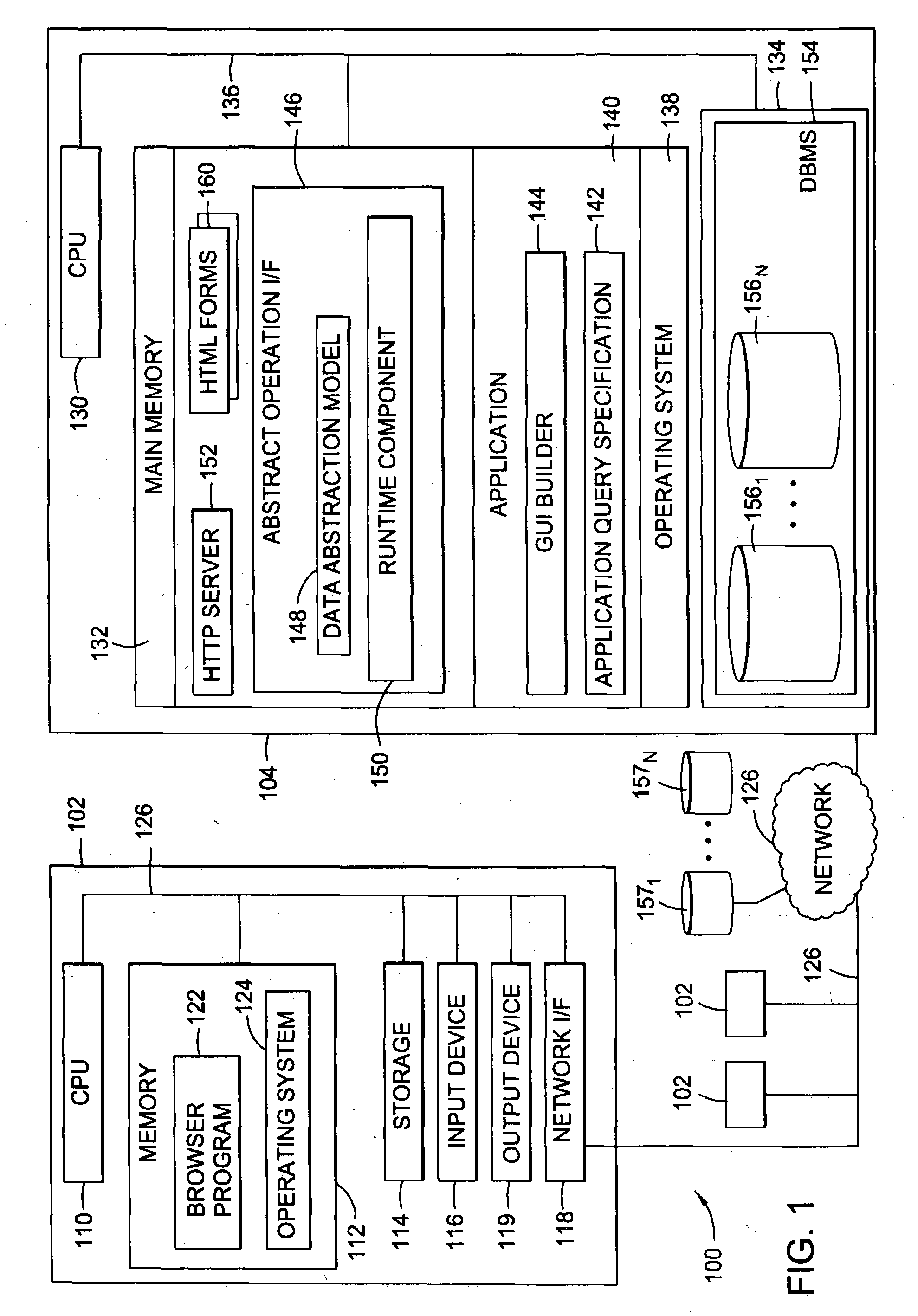

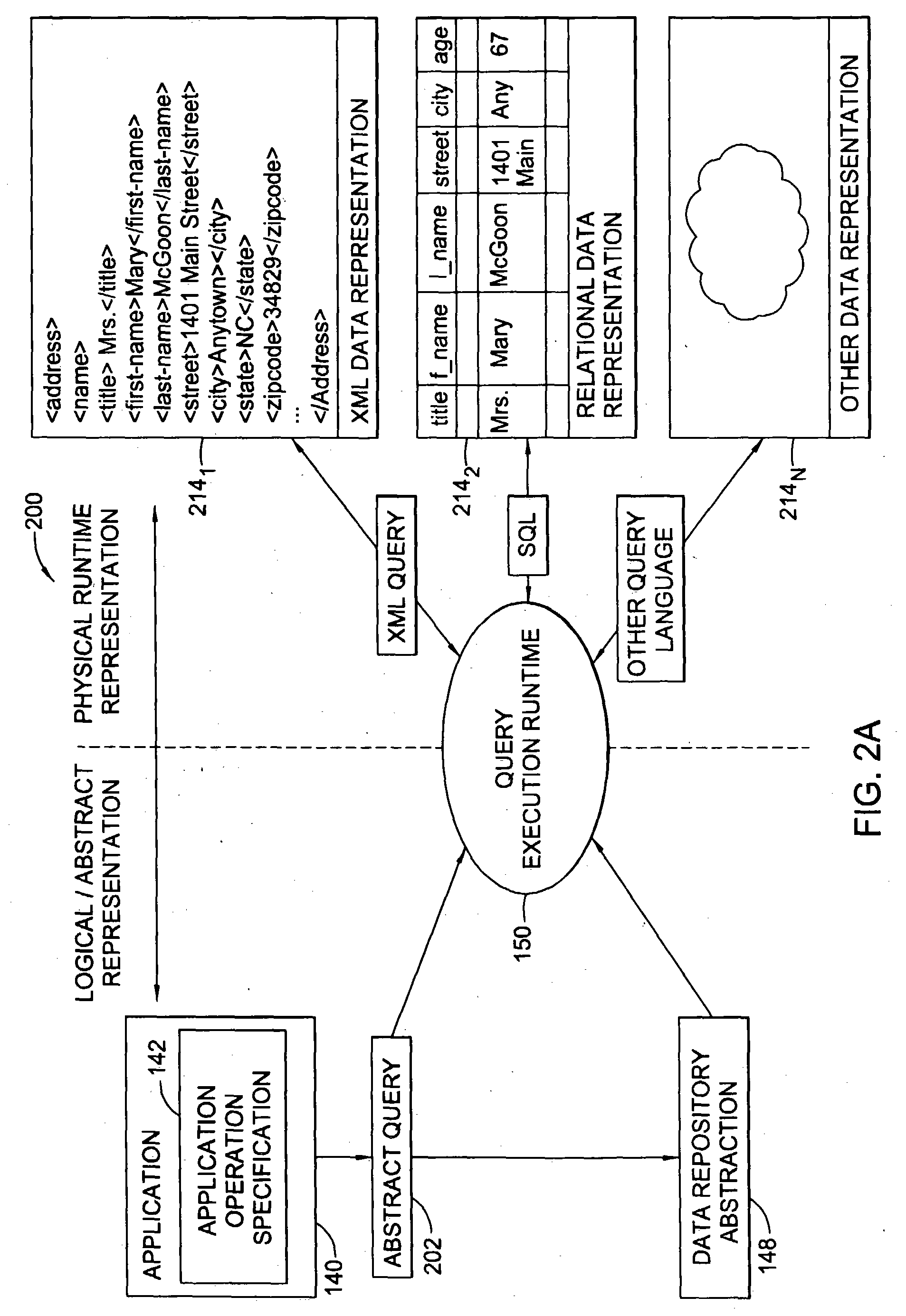

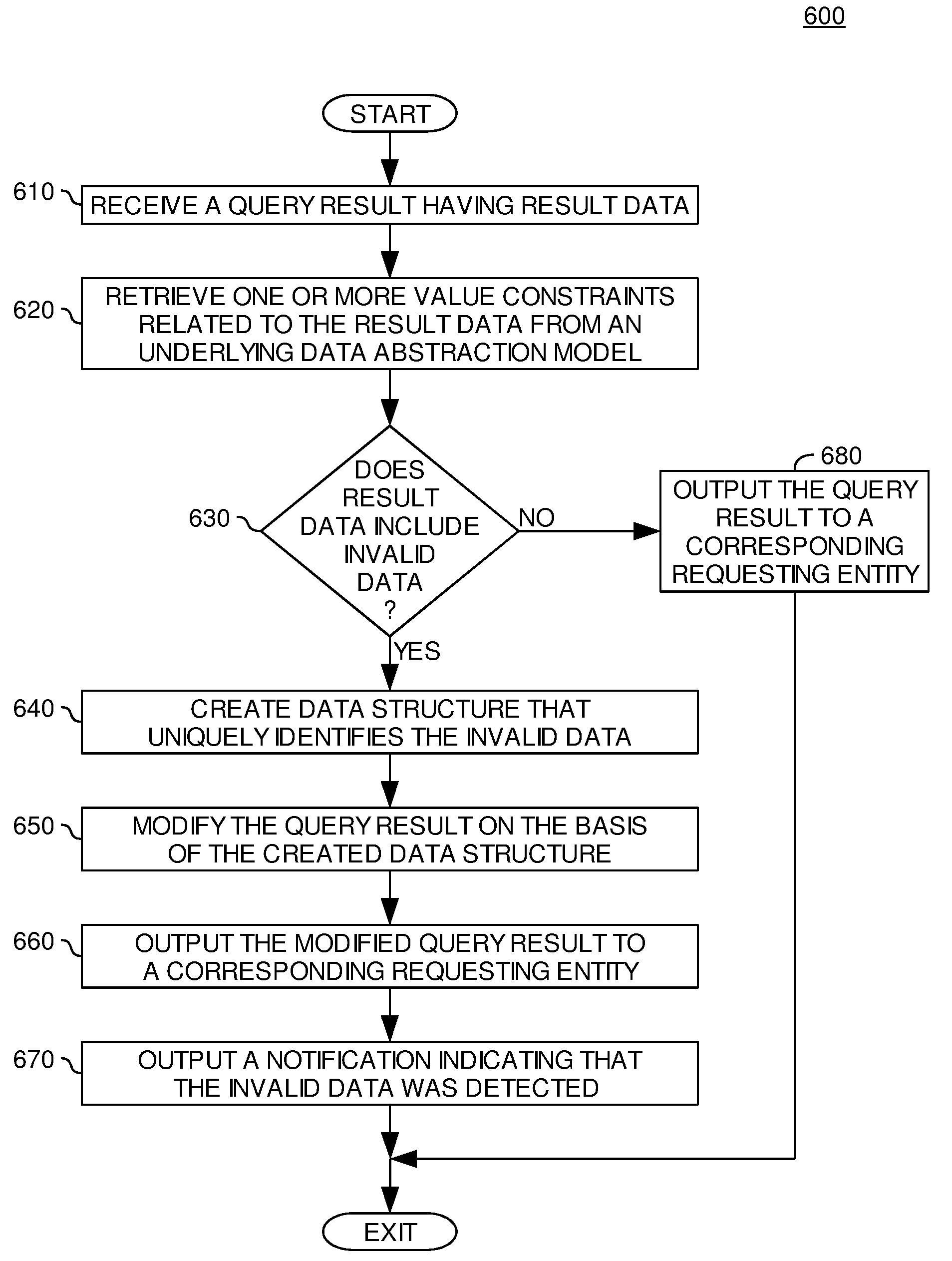

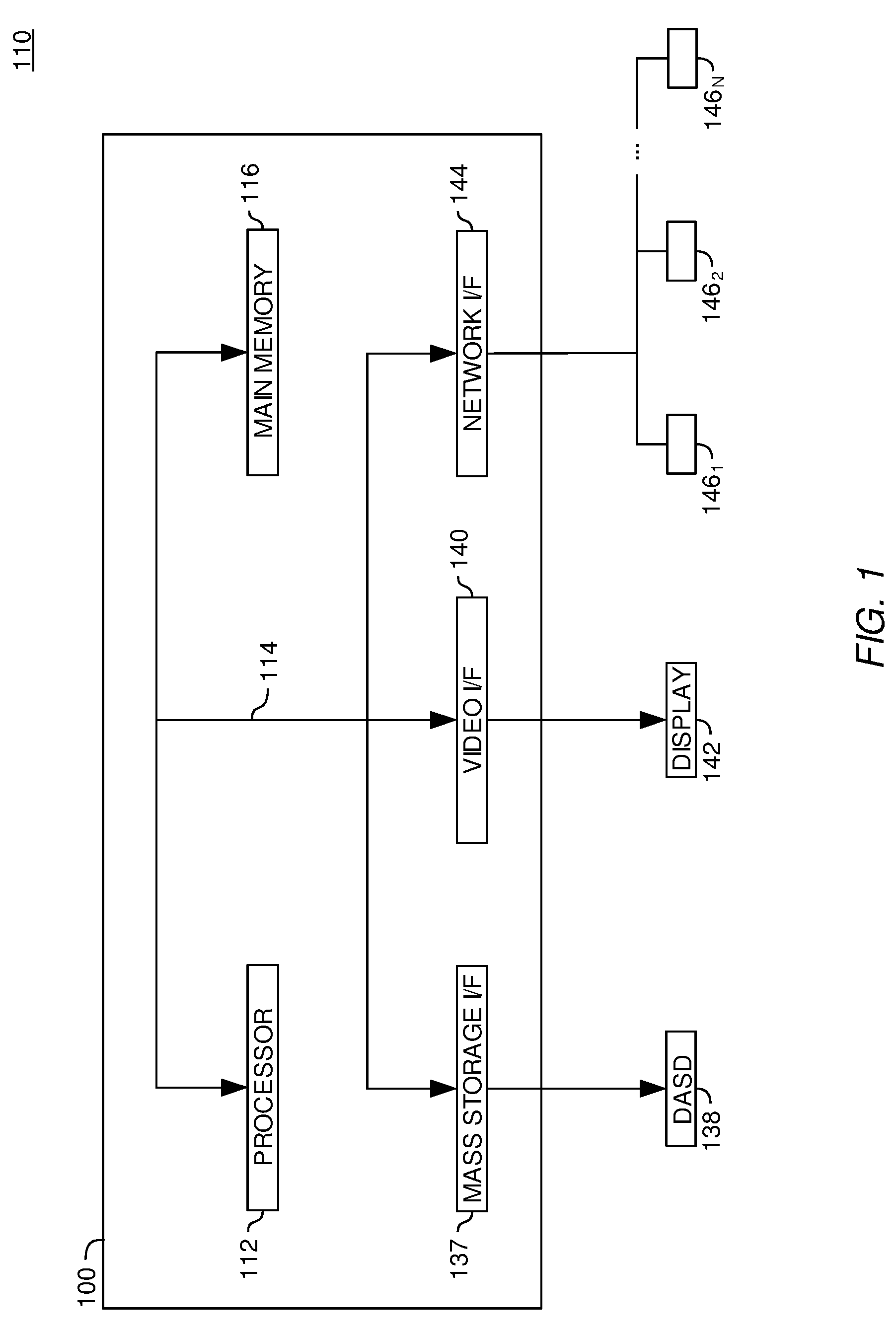

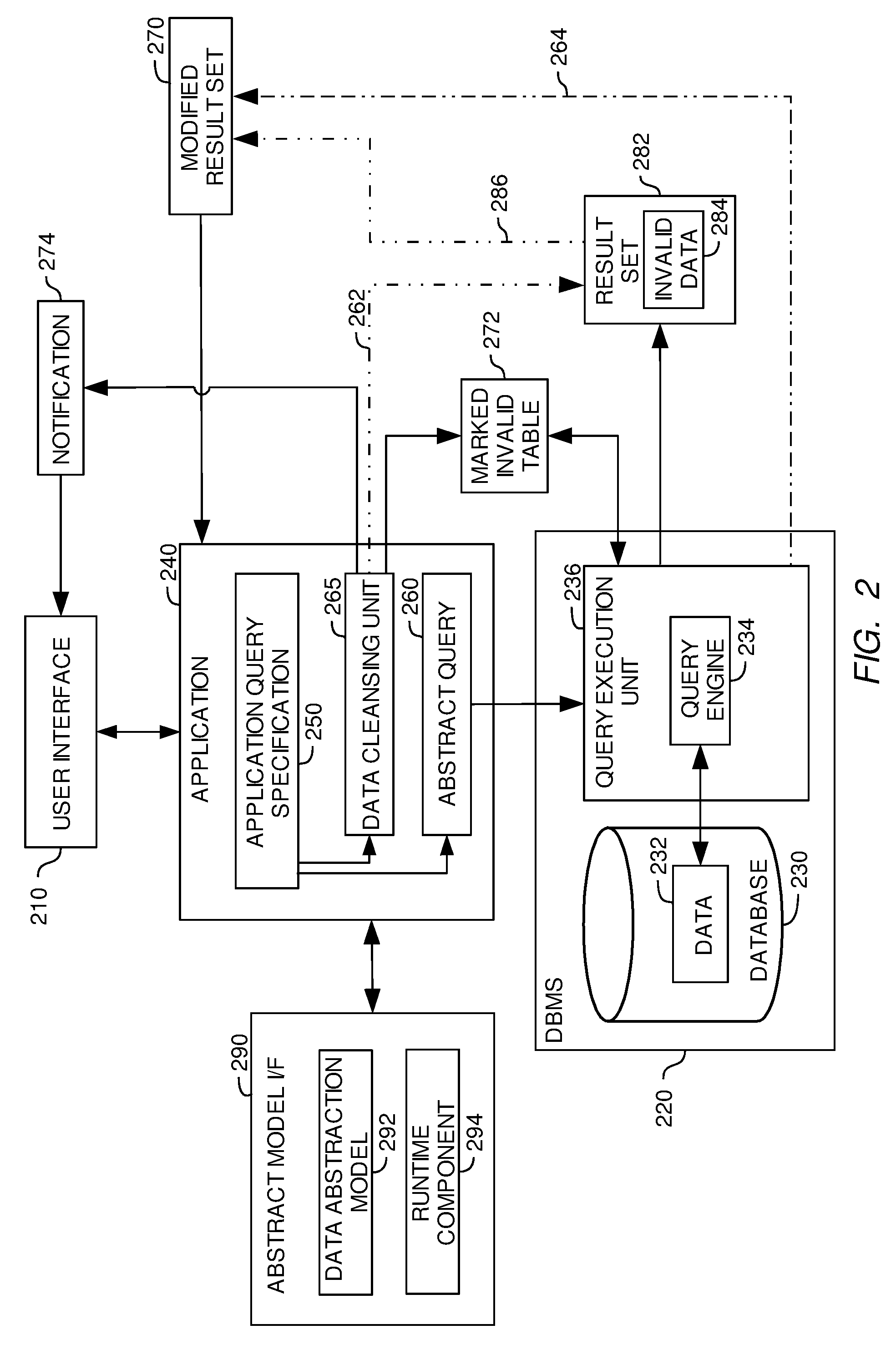

Method and system for performing a clean operation on a query result

InactiveUS20080120286A1Digital data information retrievalSpecial data processing applicationsData abstractionInvalid Data

A method, system and article of manufacture for performing a clean operation on a query result. One embodiment comprises receiving a query result for an abstract query composed on the basis of a data abstraction model that models physical data in one or more databases in a manner making a schema of the physical data transparent to a user of the abstraction model. The query result has result data that is based on the physical data for at least one logical result field included in the abstract query. The logical result field has a corresponding logical field definition in the abstraction model. One or more value constraints specified in the logical field definition are applied to determine whether the result data of the query result includes invalid data that does not satisfy the value constraints. If so, a data structure is created that uniquely identifies the invalid data.

Owner:IBM CORP

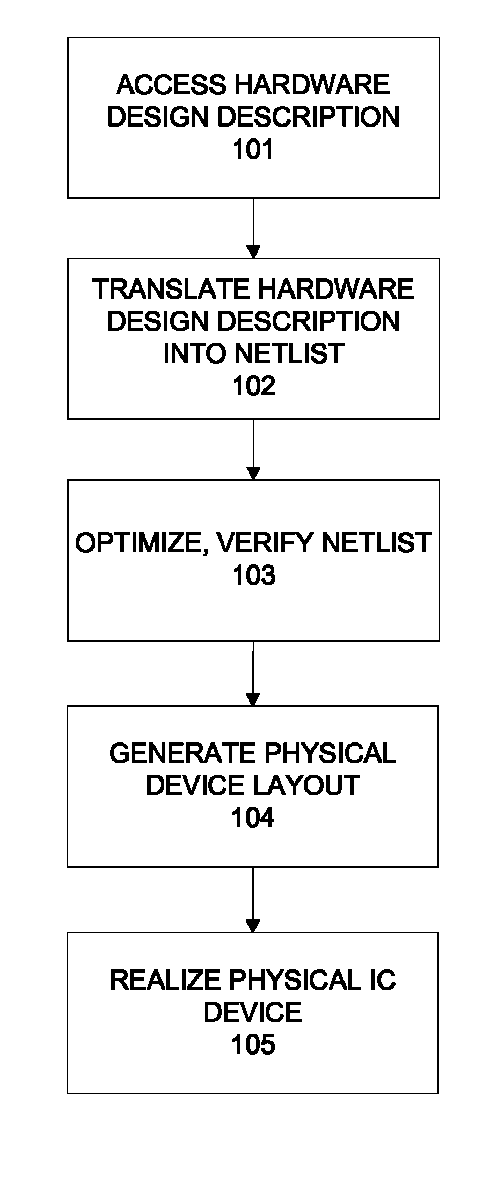

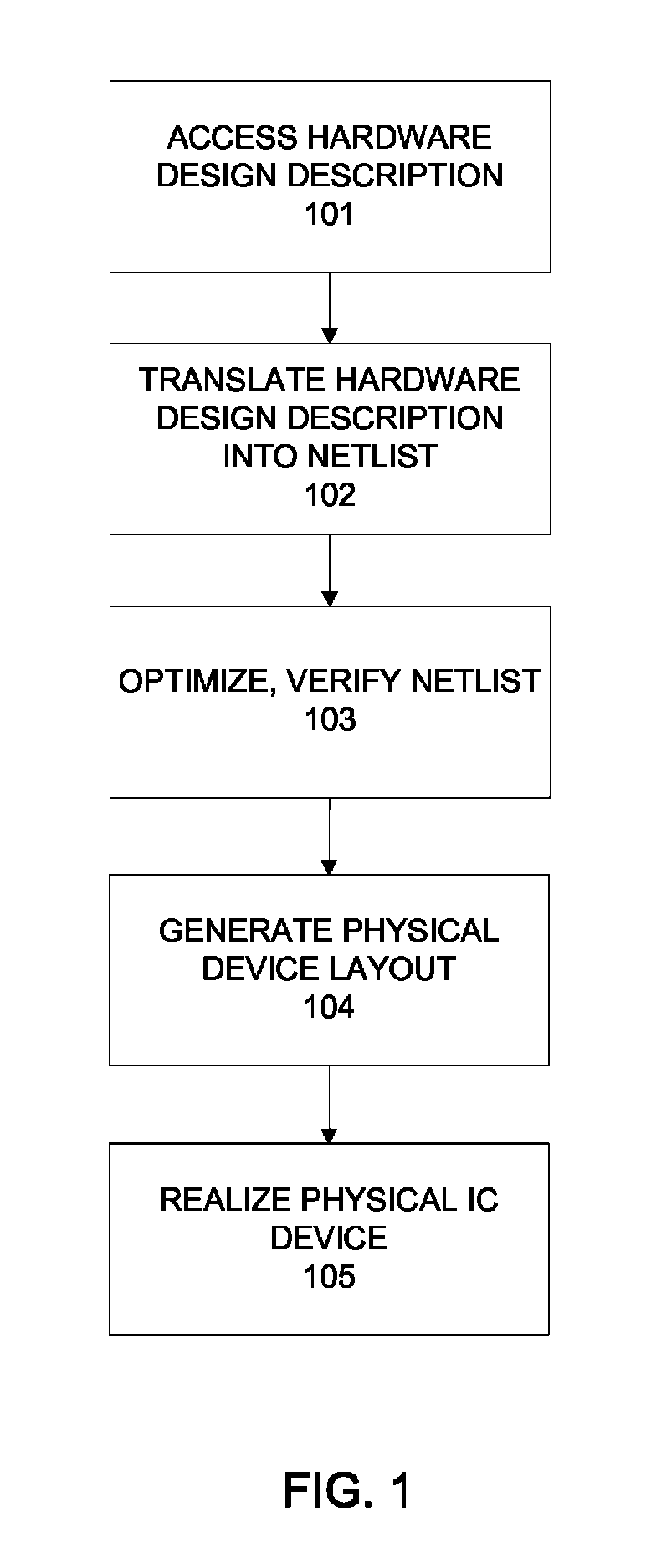

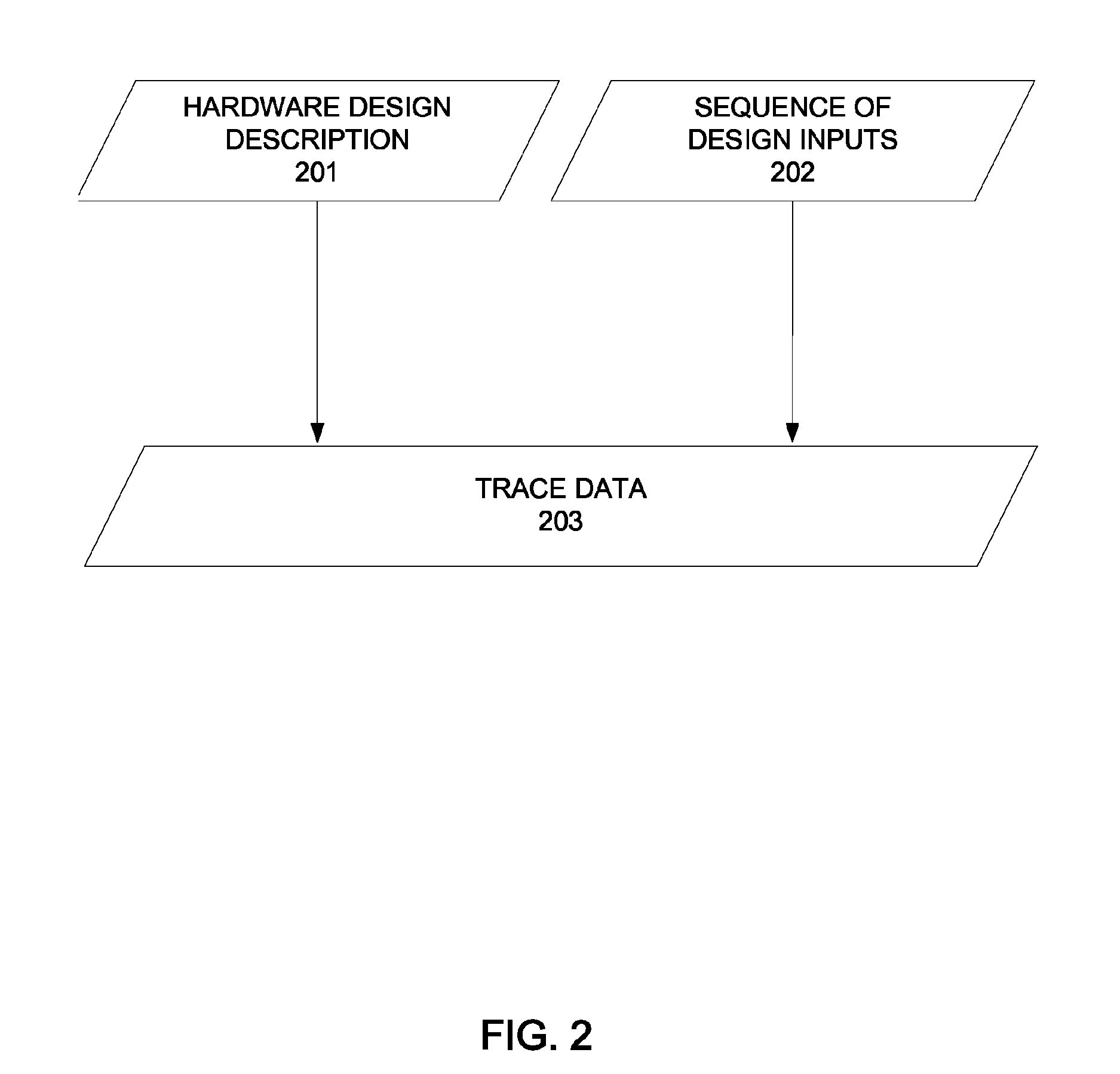

Methods for automatically generating assertions

ActiveUS7926020B1Detecting faulty computer hardwareCAD circuit designLogic optimizationTheoretical computer science

One embodiment of the present invention provides a method that automatically generates assertions of a hardware design. The method includes accessing a trace and a set of predicates of the hardware design. Then, the trace is projected over the set of predicates to generate a second trace. Then, a new set of states of the second trace is computed and the result is represented as a logical formula. The formula is reduced by logic optimization techniques. And finally, a set of logical consequences of the logic formula is produced and each logical consequence is enumerated as an assertion.

Owner:SYNOPSYS INC

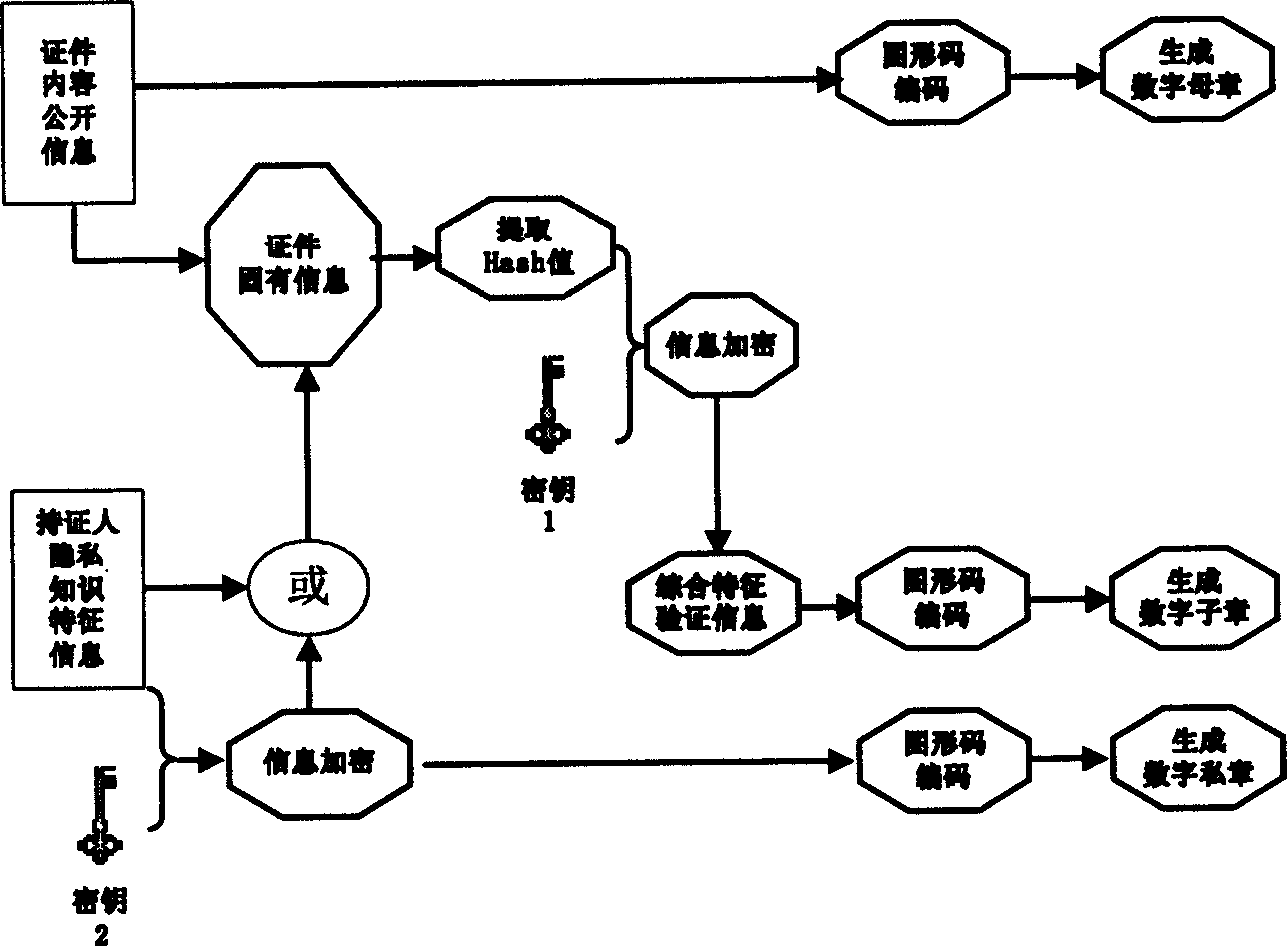

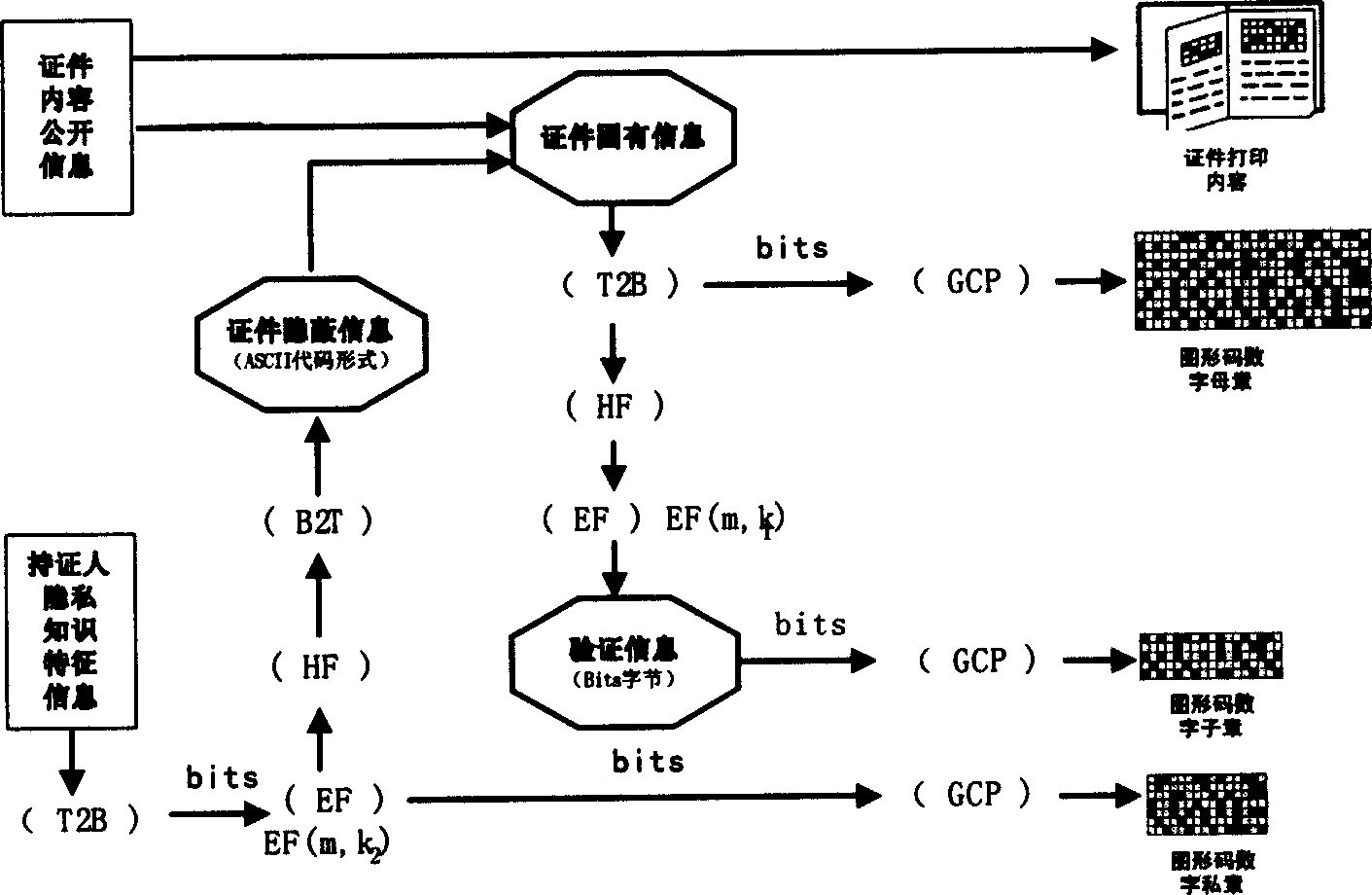

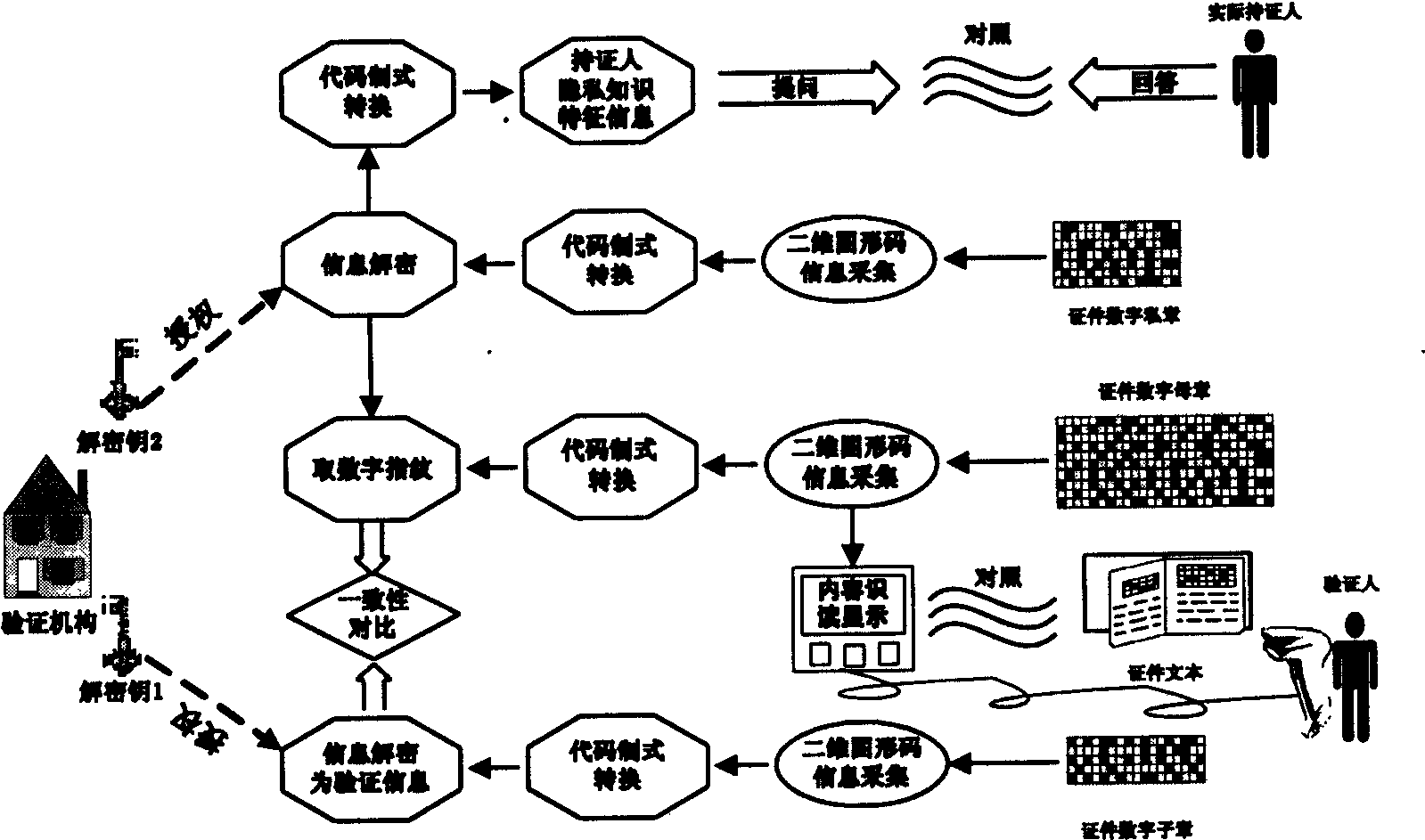

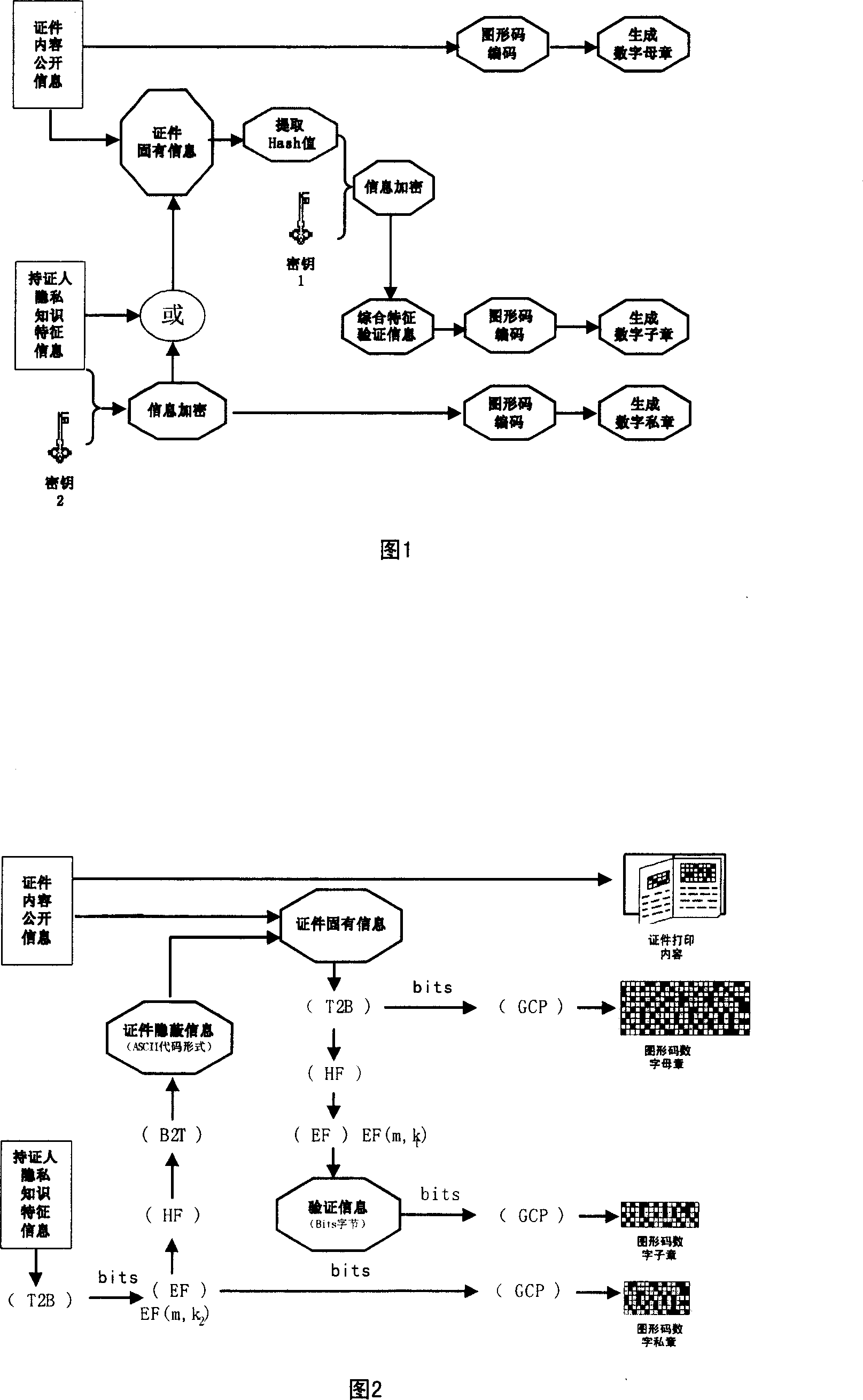

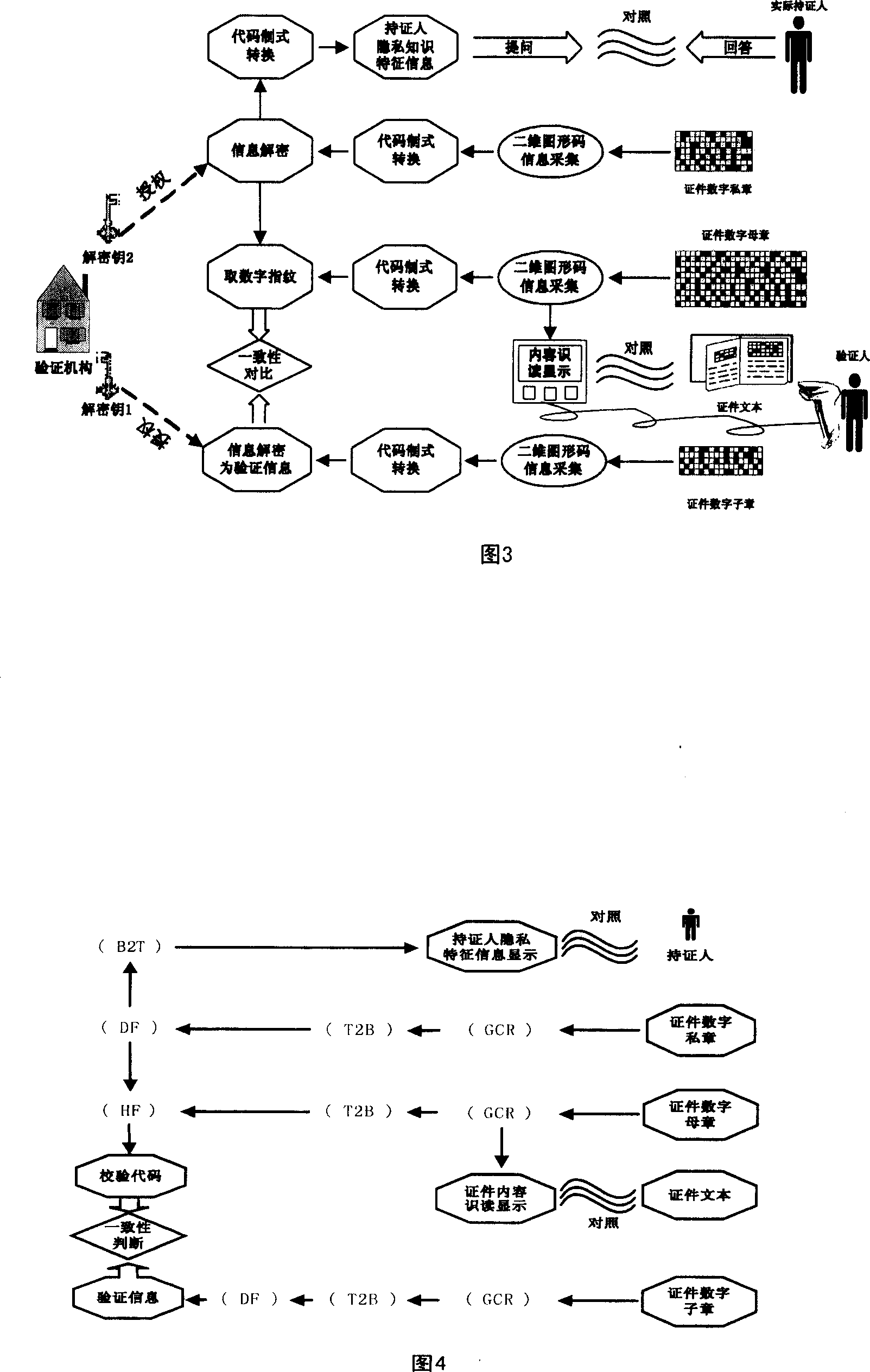

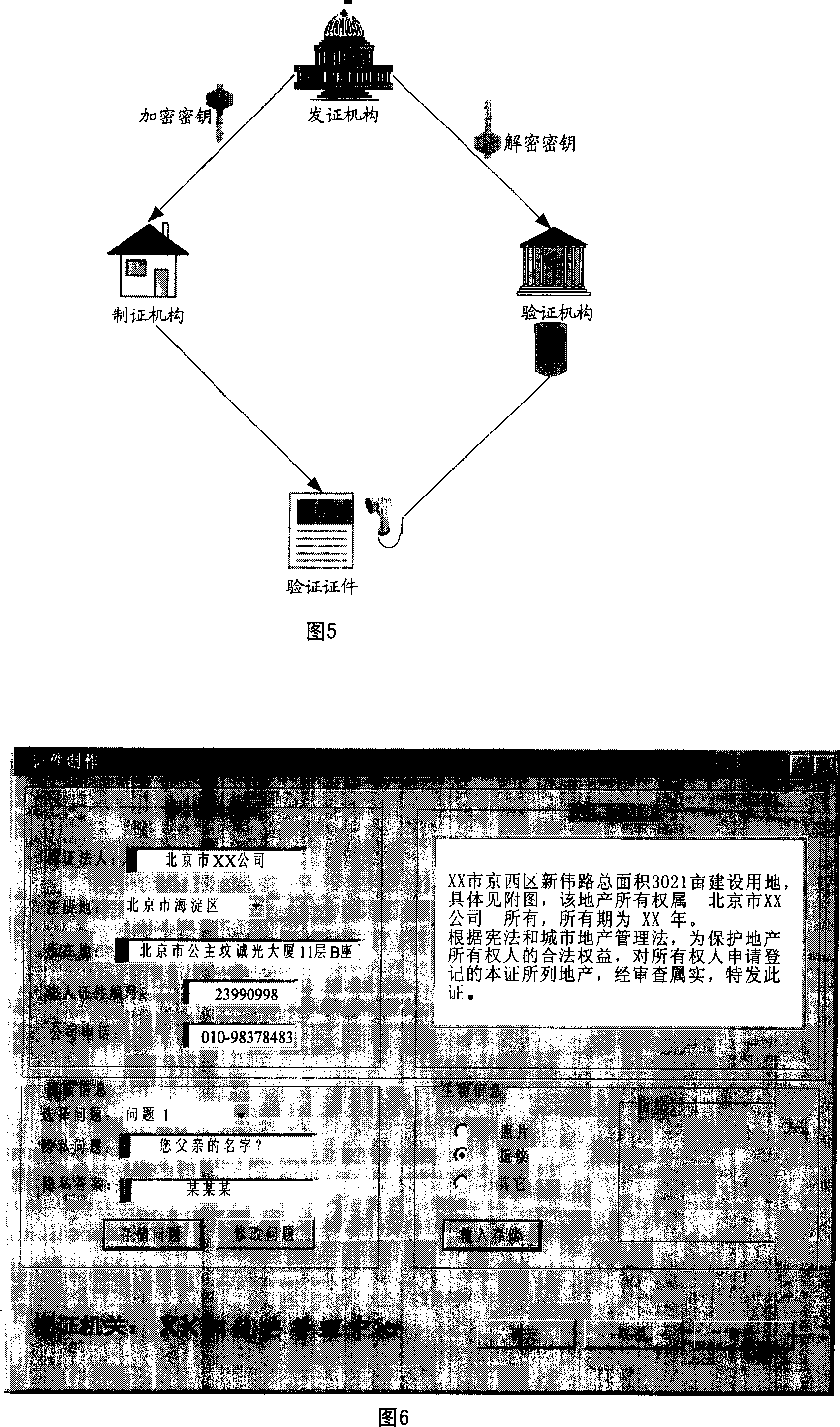

Soft certification anti-false method based on graphic code primary and secondary signet series information association mechanism

InactiveCN1570962AGood choiceEasy to implementUser identity/authority verificationCo-operative working arrangementsGraphicsHuman sense

Owner:中国科学院成都计算机应用研究所

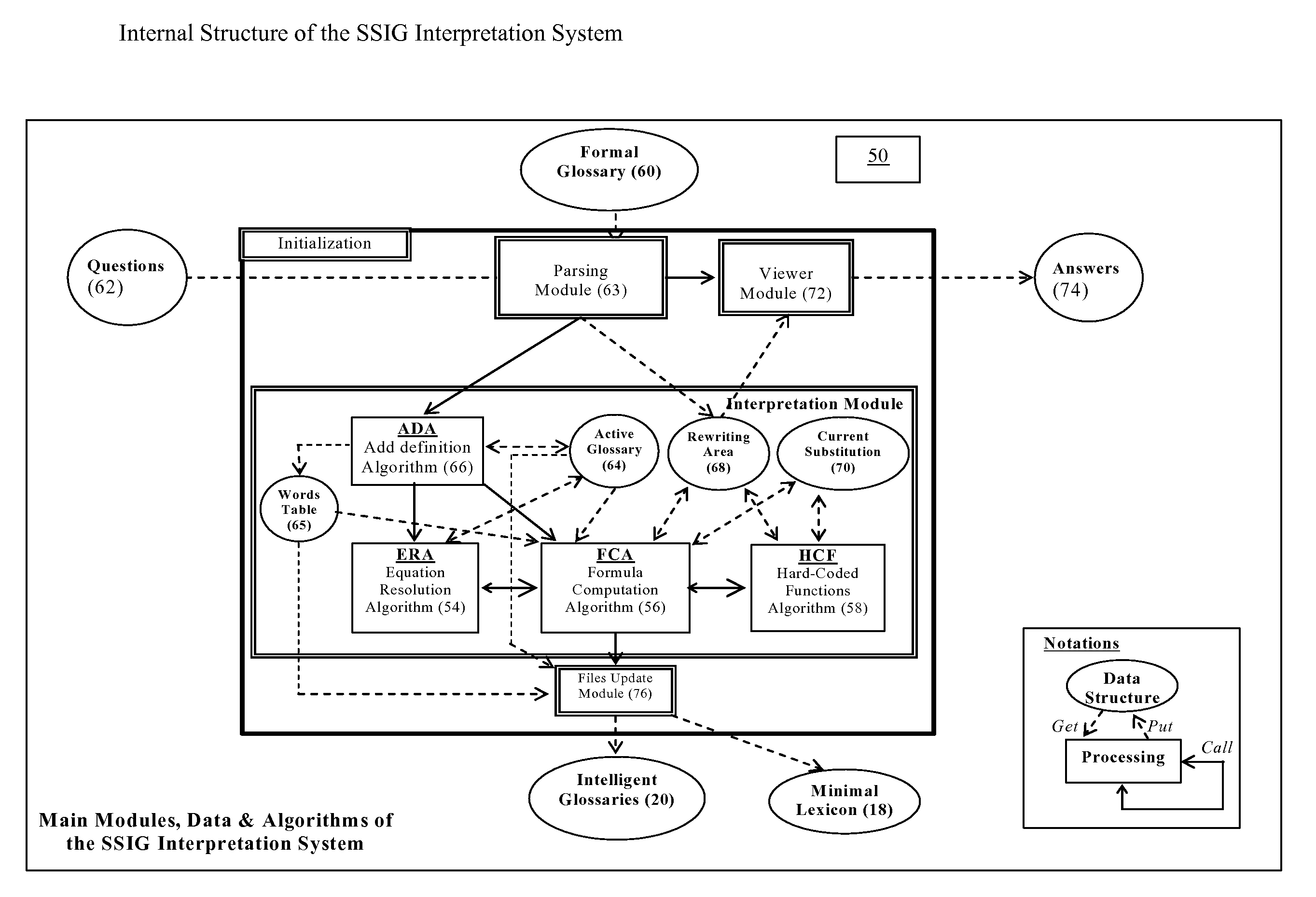

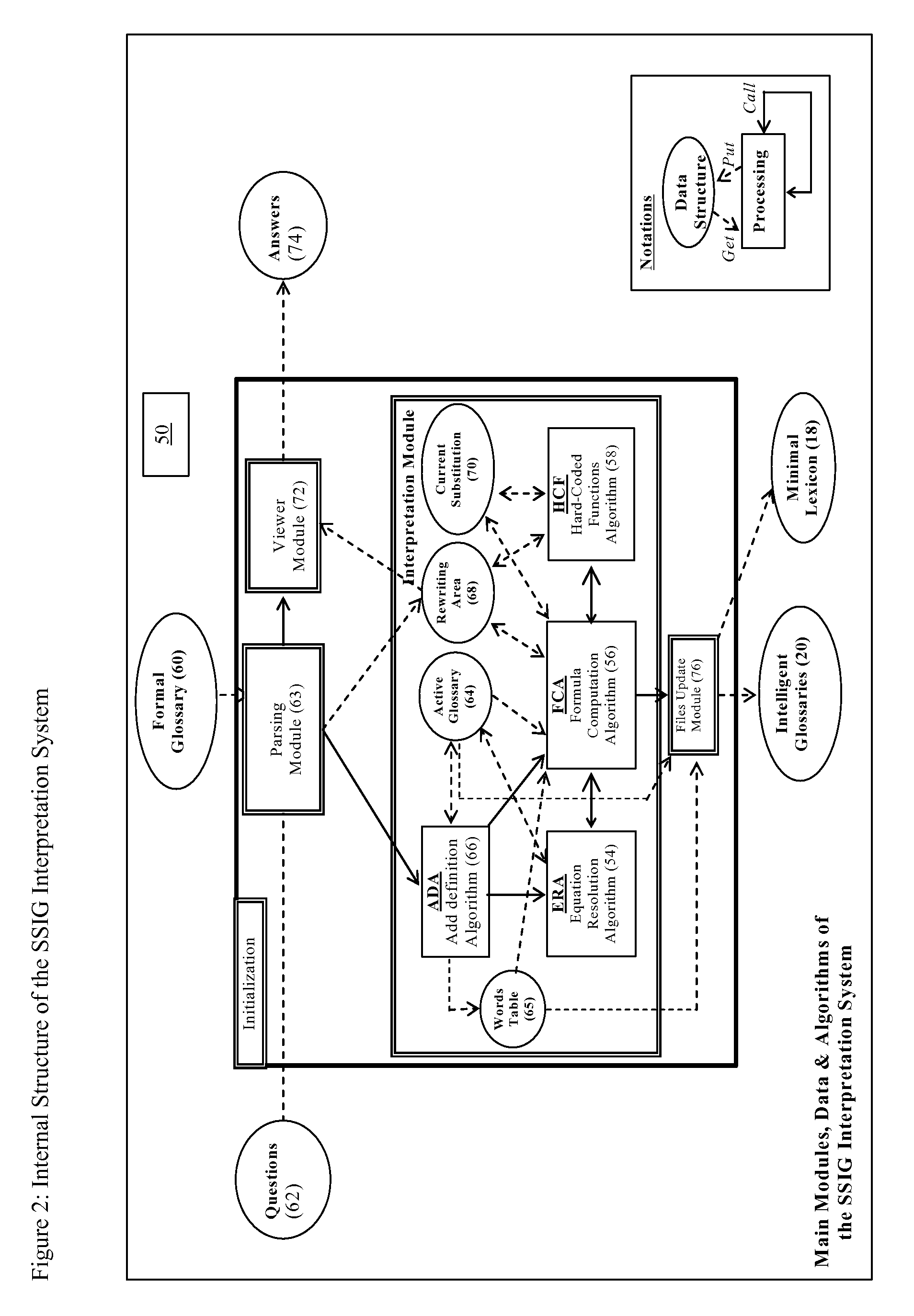

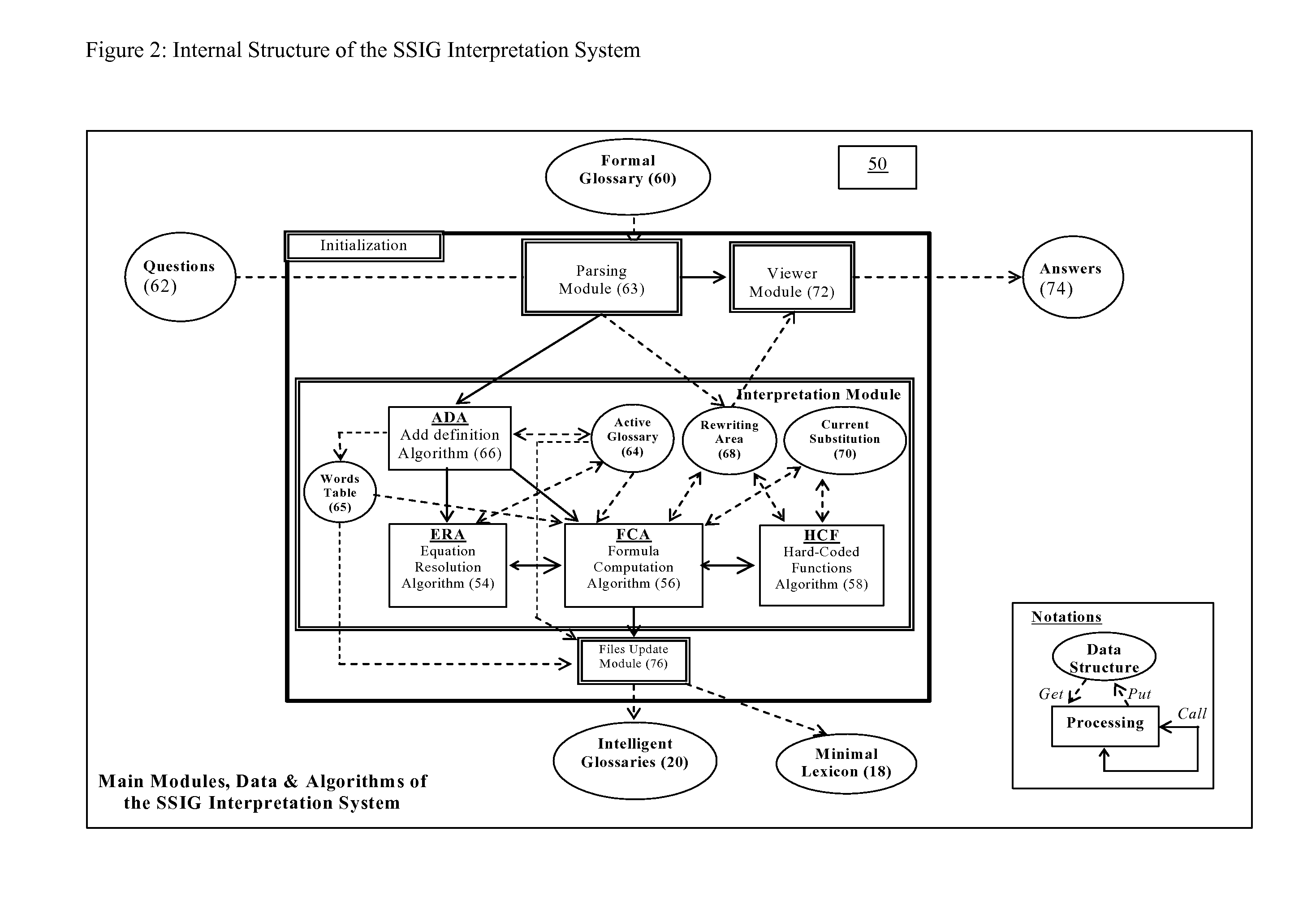

Methods and systems for interpreting text using intelligent glossaries

A computer implemented method used to interpret text, including from a set of formal glossaries which may refer one to the other and are intended to define precisely the terminology of a field of endeavor. Such glossaries are known as intelligent, in the sense that they allow machines to make deductions, without the need for human intervention. However, they may also accept human intervention. Once a word is defined in an intelligent glossary, all the logical consequences of the use of that word in a formal and well-formed sentence are computable. The process includes a question and answer mechanism, which applies the definitions contained in the intelligent glossaries to a given formal sentence. The methods may be applied in the development of knowledge management methods and tools that are based on semantics; for example: modeling of essential knowledge in the field based on the relevant semantics.

Owner:AEBIS

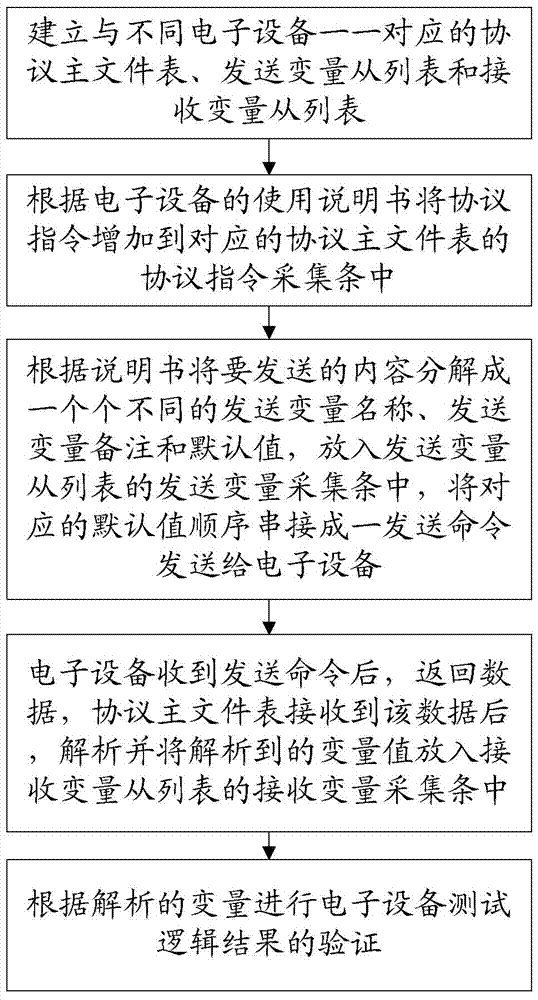

General processing method for testing assembly of different electronic devices

ActiveCN107038118AImprove compatibilityIncrease speedSoftware testing/debuggingTotal factory controlComputer hardwareComputer compatibility

The present invention provides a general processing method for testing assembly of different electronic devices. The method comprises: 1. establishing a protocol master file table, a sending variable slave list and a receiving variable slave list in one-to-one correspondence with different electronic devices; 2. according to an instruction of an electronic device, adding a protocol instruction into a protocol instruction acquisition strip of a corresponding protocol master file table; 3. according to the instruction, discomposing to-be-sent content into different sending variable names, sending variable notes and default values, putting the different sending variable names, sending variable notes and default values into a sending variable acquisition strip of a sending variable slave list, and connecting serially and sequentially corresponding default values into a sending command and sending the sending command to the electronic device; 4. after the electronic device receives the sending command, returning data, and after the protocol master file table receives the data, analyzing the data and putting a variable value obtain through analysis into a receiving variable acquisition strip of a receiving variable slave list; and 5. performing verification on an electronic device test logic result according to a variable obtained through analysis. The method provided by the present invention improves compatibility and fastness of testing.

Owner:FUJIAN NEBULA ELECTRONICS CO LTD

Methods and systems for interpreting text using intelligent glossaries

A computer implemented method and systems used to create and interpret a set of formal glossaries which refer one to the other and are intended to define precisely the terminology of a field of endeavor. Such glossaries are known as intelligent, in the sense that they allow machines to make deductions, with interaction of human actors. Once a word is defined in an intelligent glossary, all the logical consequences of the use of that word in a formal and well-formed sentence are computable. The process includes a question and answer mechanism, which applies the definitions contained in the intelligent glossaries to a given formal sentence. The methods may be applied in the development of knowledge management methods and tools that are based on semantics; for example: modeling of essential knowledge in the field based on the relevant semantics; and computer-aided human-reasoning.

Owner:AEBIS

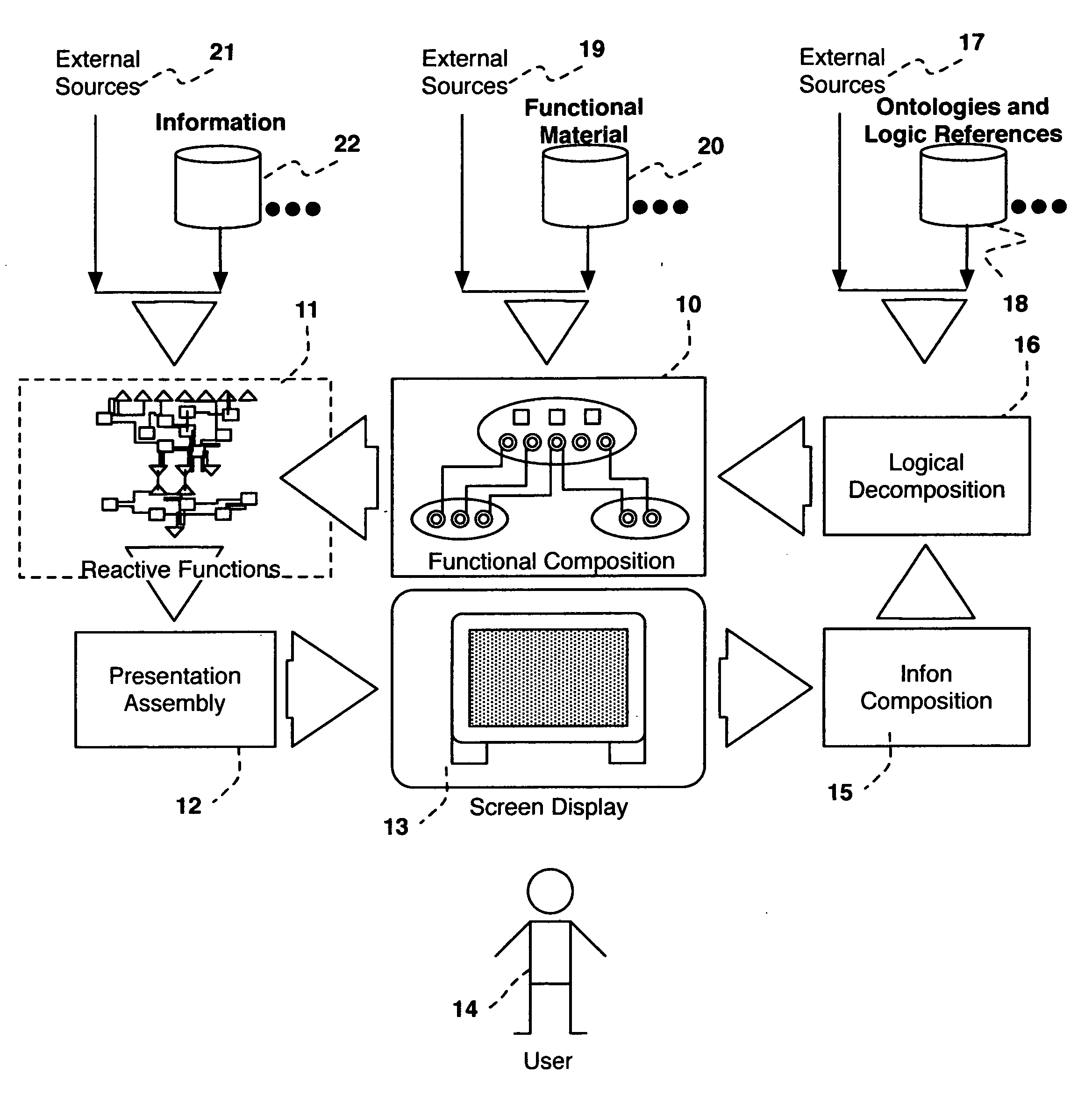

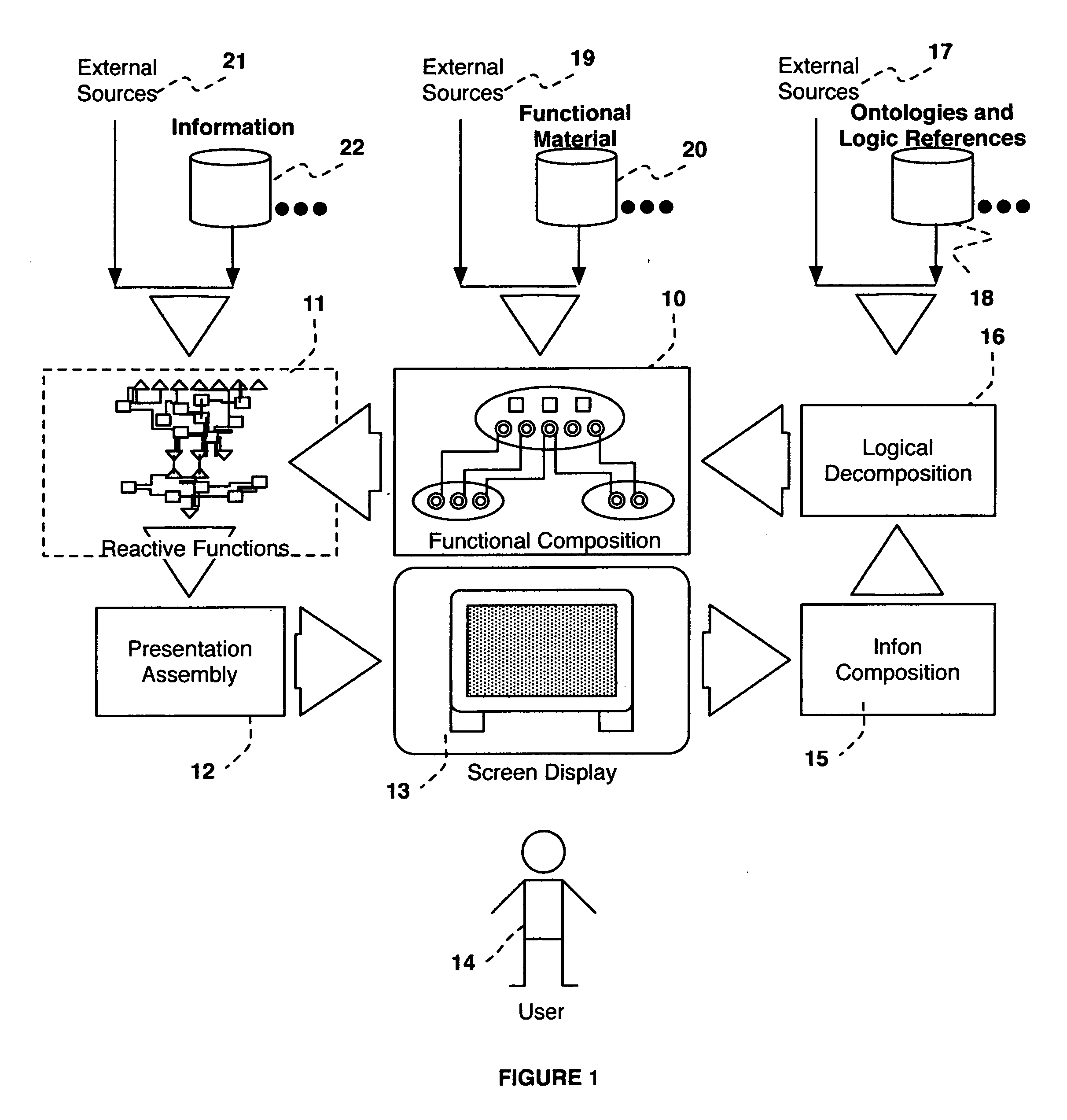

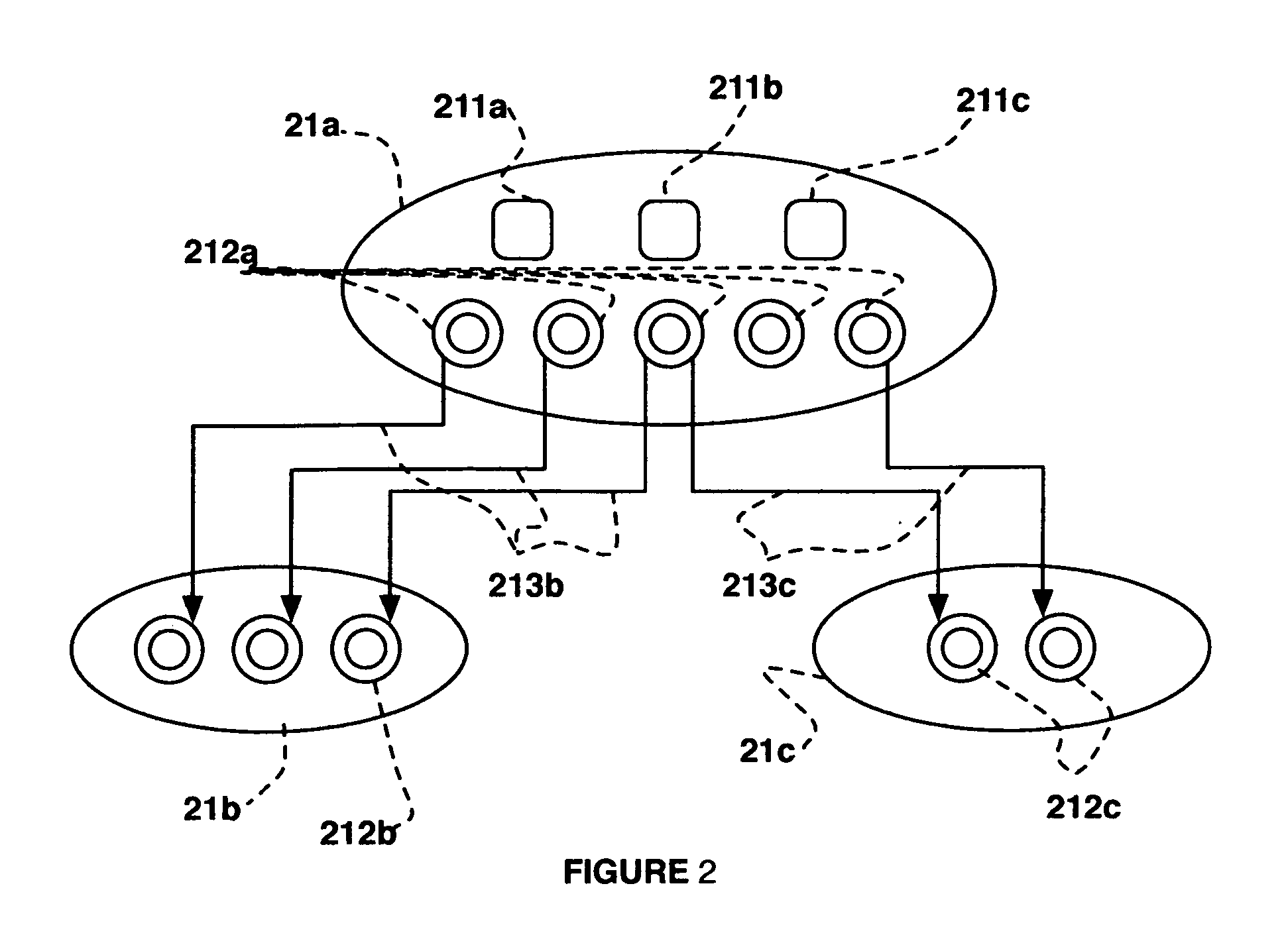

System and method for structuring information

InactiveUS20100268769A1Digital data processing detailsMultiple digital computer combinationsData flow programmingMathematical logic

The present invention provides a novel computer system that synthesizes object programming, functional programming, data-flow programming, mathematical logic and cognitive modeling. The synthesis allows a system to exist which provides for close alignment among the manner in which a user interacts with a system, how that interaction is logically parsed, how set-theoretic composition of the logic results, how that set-theoretic algorithm builds functional reactive flows and how those flows are structured for display to a user.

Owner:GORANSON H TED

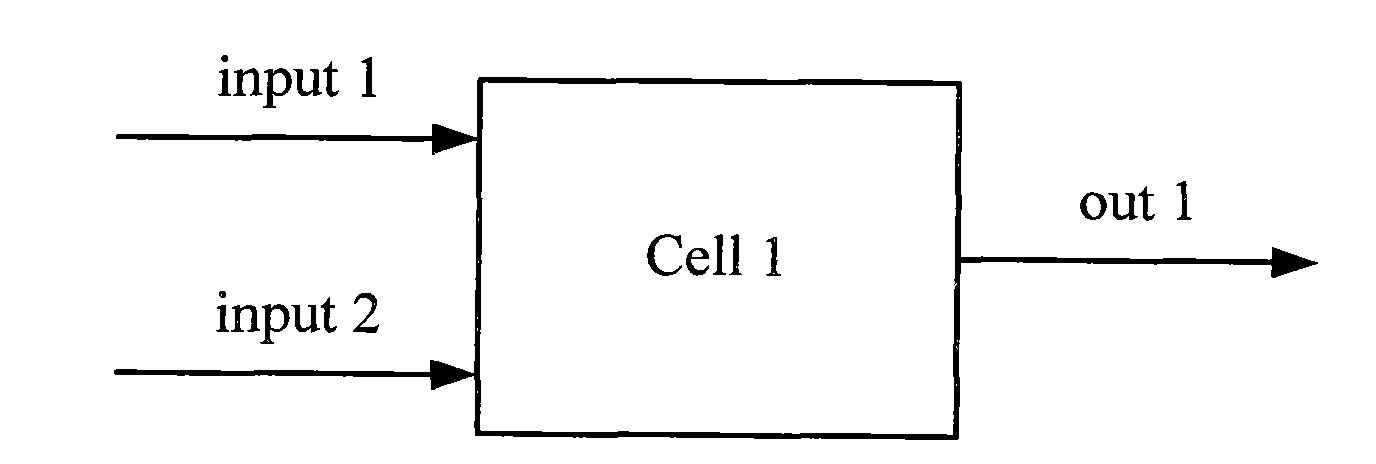

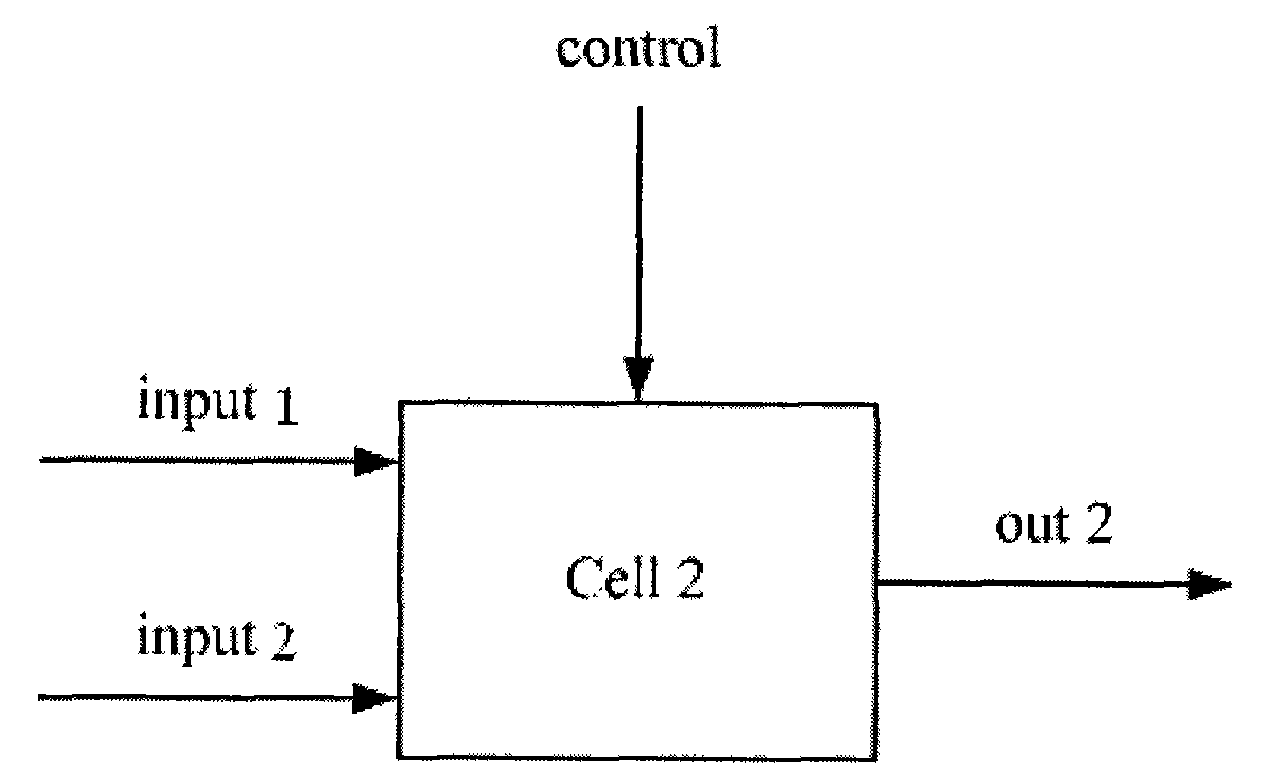

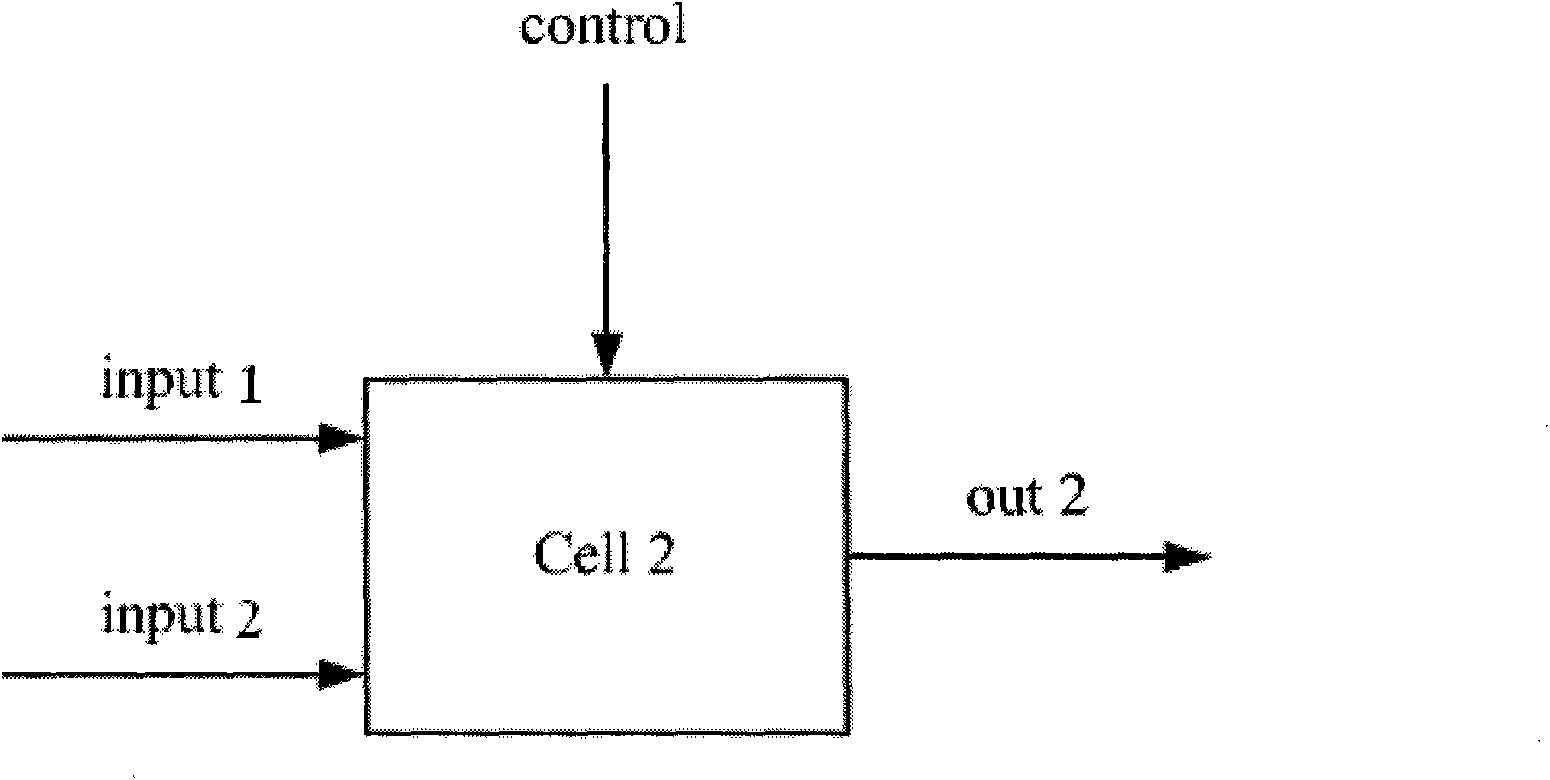

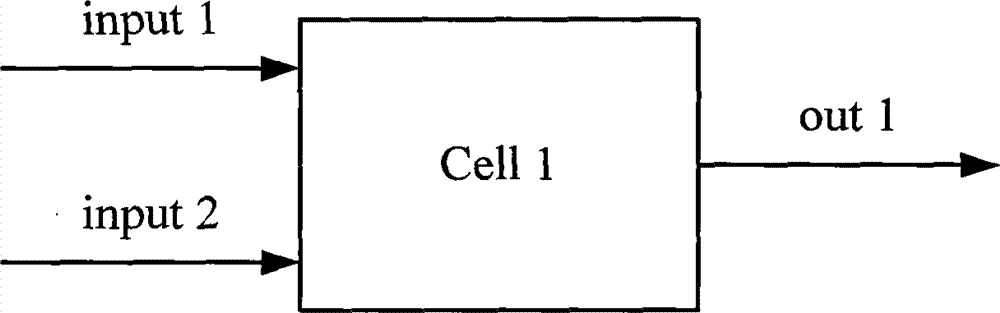

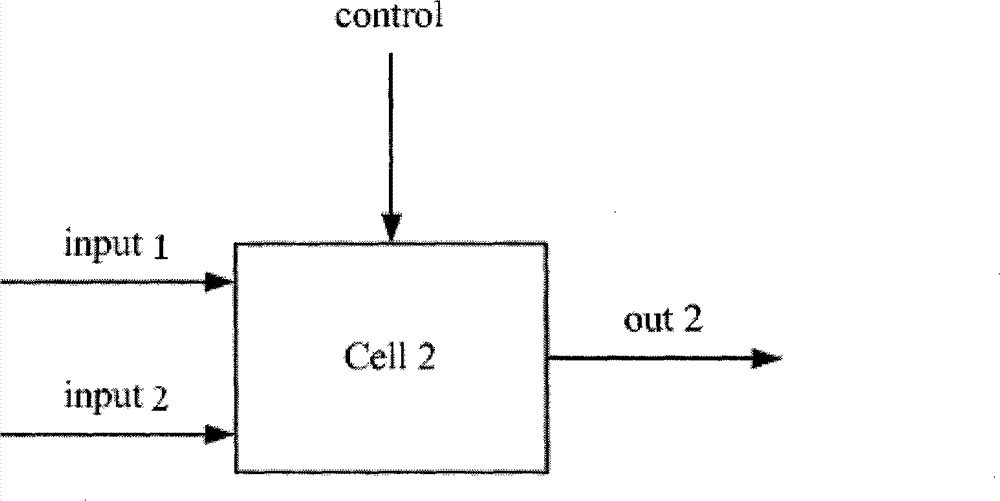

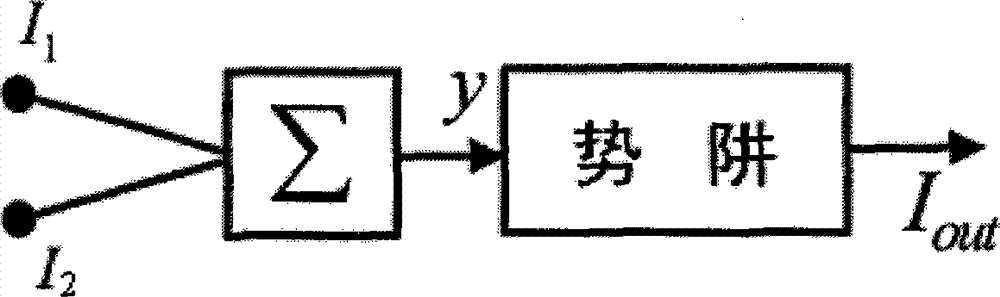

Reconfigurable dynamic logic gate circuit

InactiveCN101783670AHigh Logic Conversion SpeedRich and varied logical resultsLogic circuits characterised by logic functionLogical operationsWeighting coefficient

The invention discloses a reconfigurable dynamic logic gate circuit capable of dynamically switching among various logics. The circuit comprises a first input end, a second input end, a third input end, an arithmetic circuit and an output end, wherein the first input end is used for receiving an input signal; the second input end is used for receiving a window threshold and a weighting coefficient used for weighting the input signal; the third input end is used for receiving a control command; the arithmetic circuit is respectively connected with the first input end, the second input end and the third input end, and is used for acquiring the logical operation result of the dynamic logic gate circuit according to the input signal, the weighting coefficient, the window threshold and the control command; and the output end is connected with the arithmetic circuit and is used for outputting the logical operation result. The invention realizes the logics in a dynamic logic gate circuit technology of quick switching among various. The technical scheme of the invention has the advantages of higher logic switching speed and various logical consequences.

Owner:BEIJING UNIV OF POSTS & TELECOMM

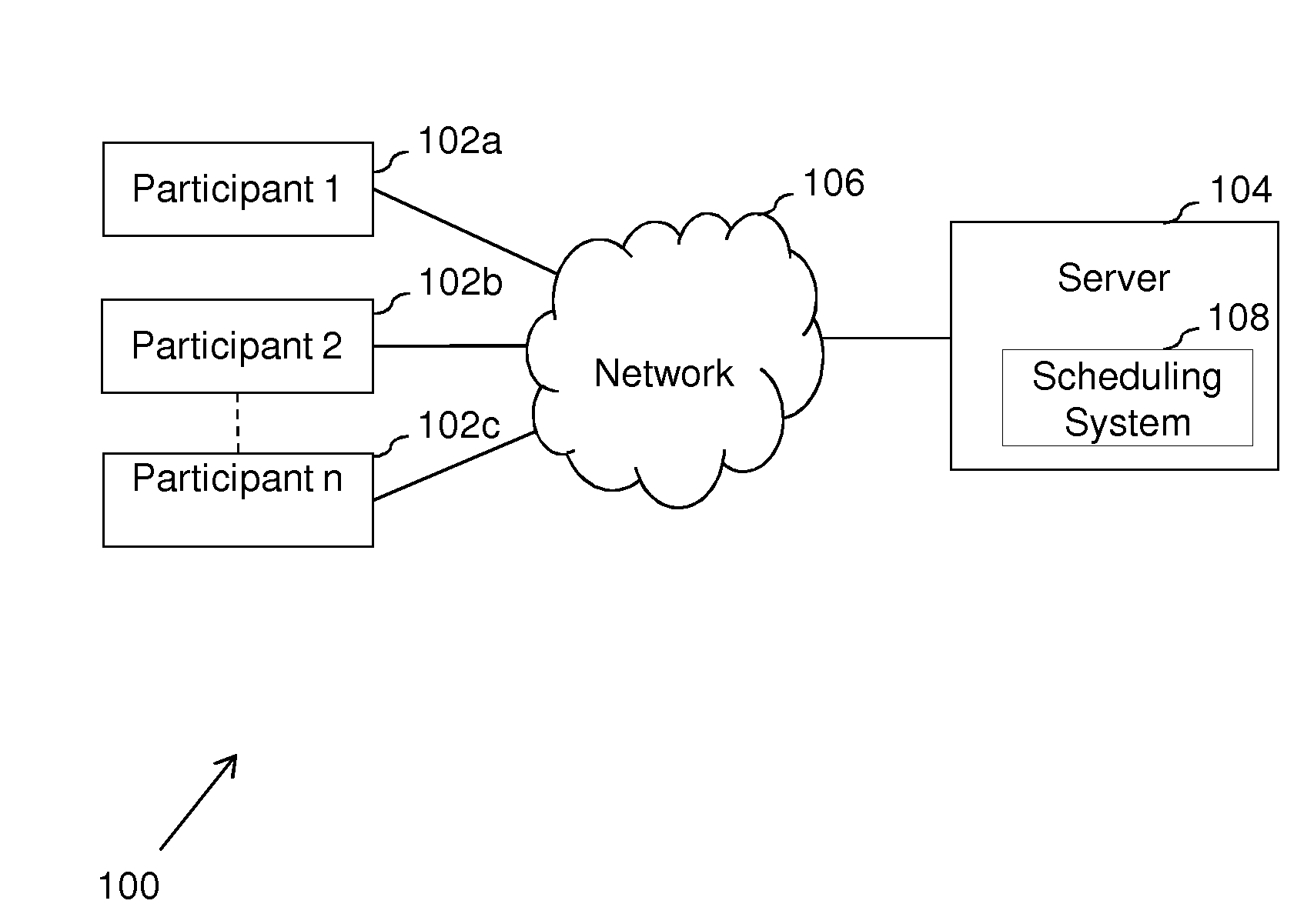

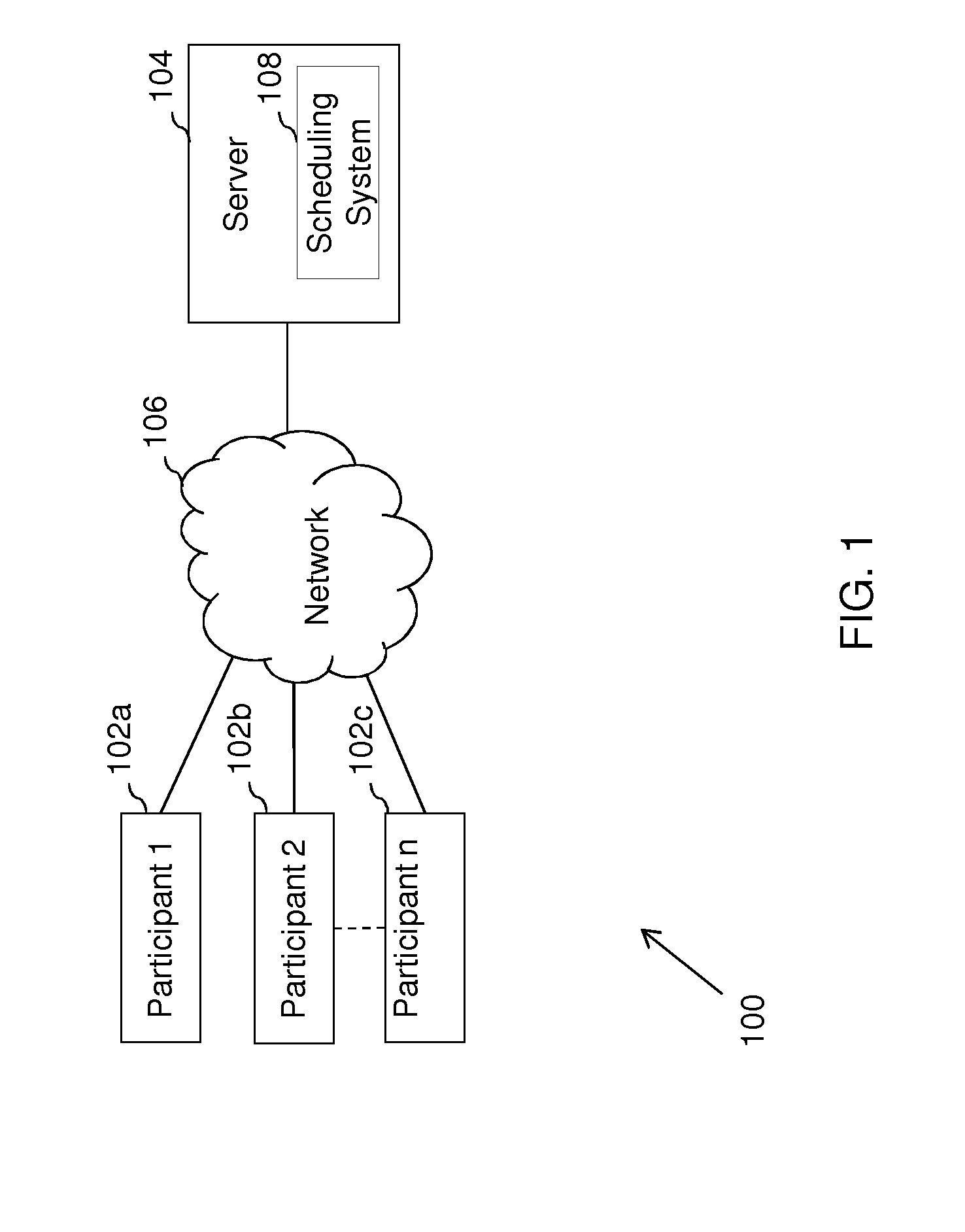

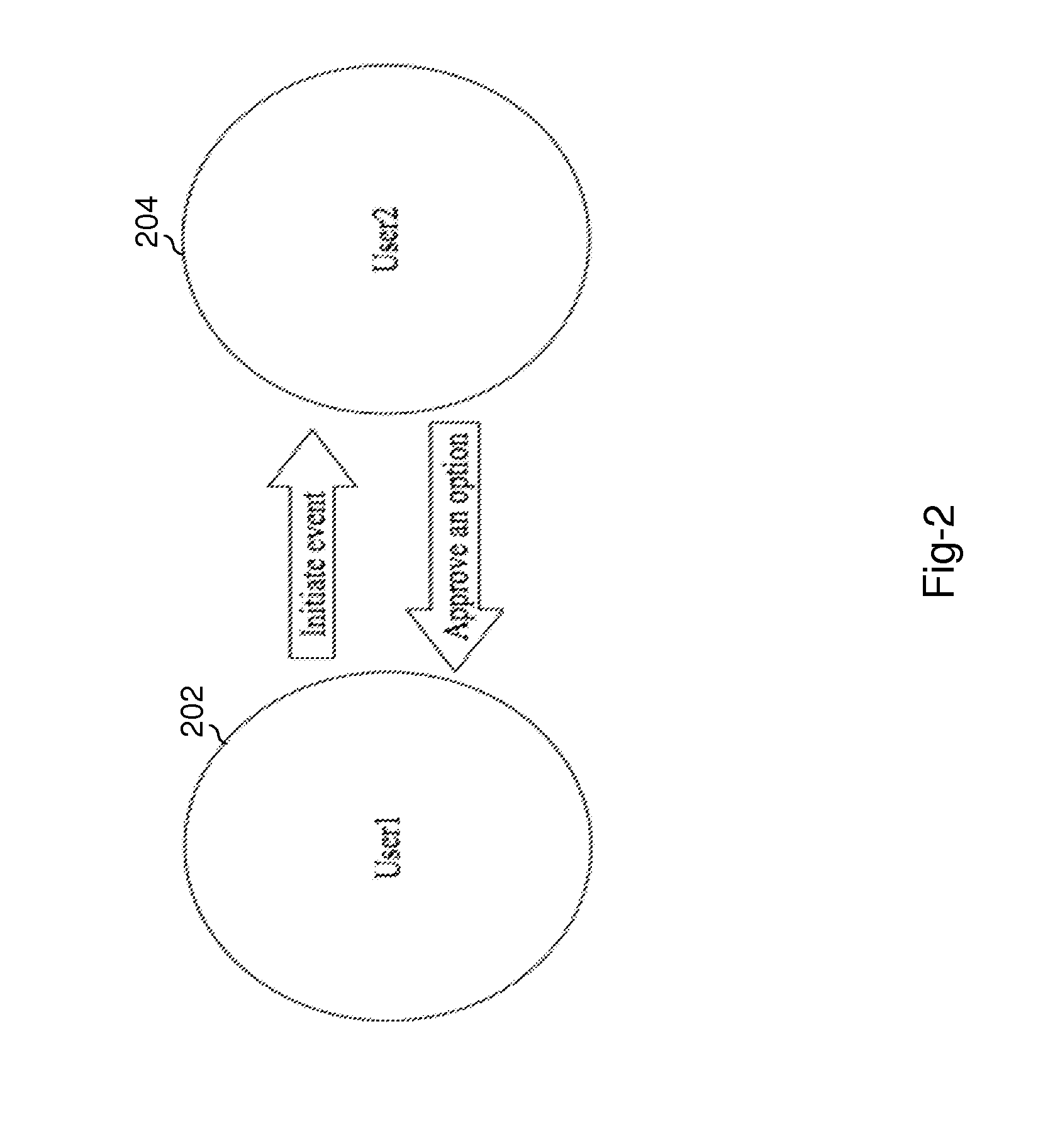

System and method for facilitating scheduling of events

Embodiments of the present invention provide a system and corresponding methods for facilitating scheduling of an event among plurality of users. The system may include various modules to received scheduling information corresponding to the event. The system may determine logical consequences corresponding to the schedule of the event based on predetermined plans of the users. The scheduling information may be shared among the plurality of users for enabling the users to update the scheduling information iteratively. The system may finalize the event automatically based on the updated scheduling information when each of the plurality of users approves the updated scheduling information. The system facilitates the scheduling of events with possibly limited resources by allowing incremental shared input from all participants and possibly by sharing their personal calendar information.

Owner:KONCHITSKY ALON

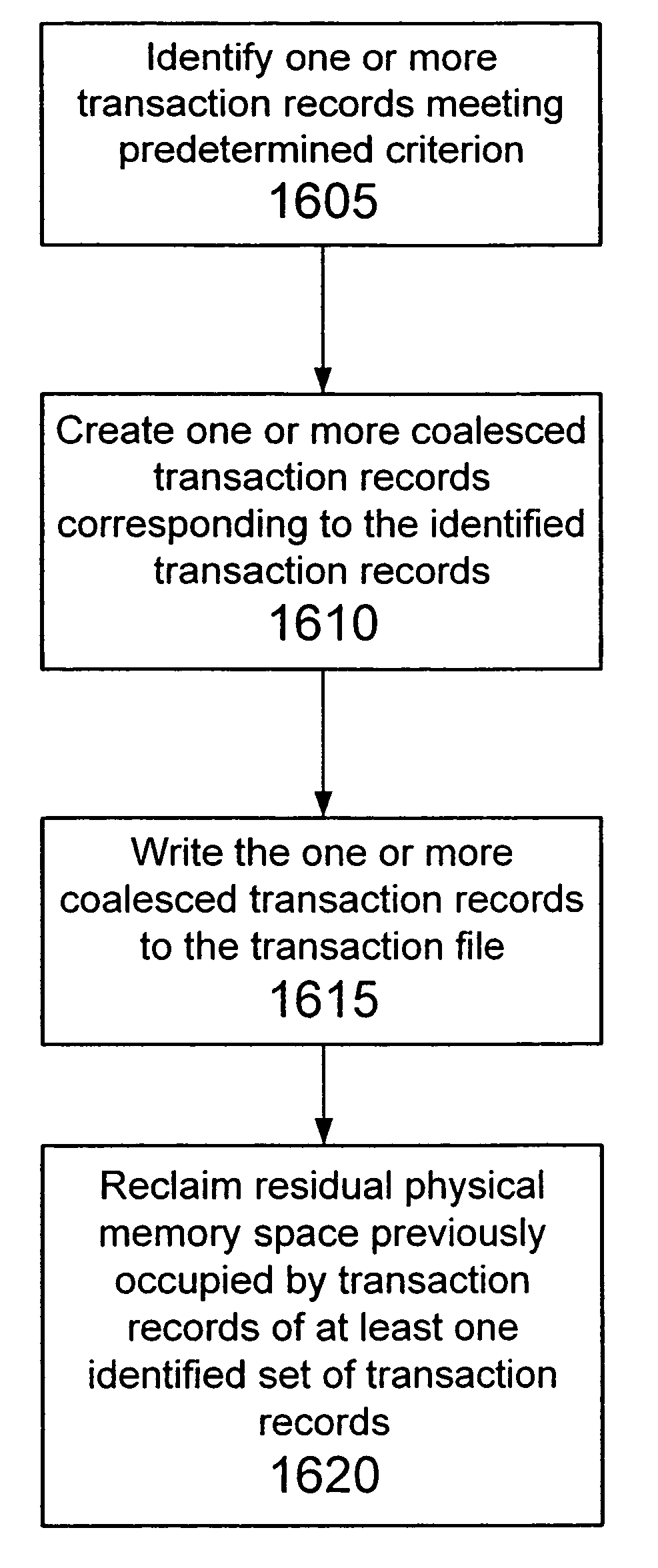

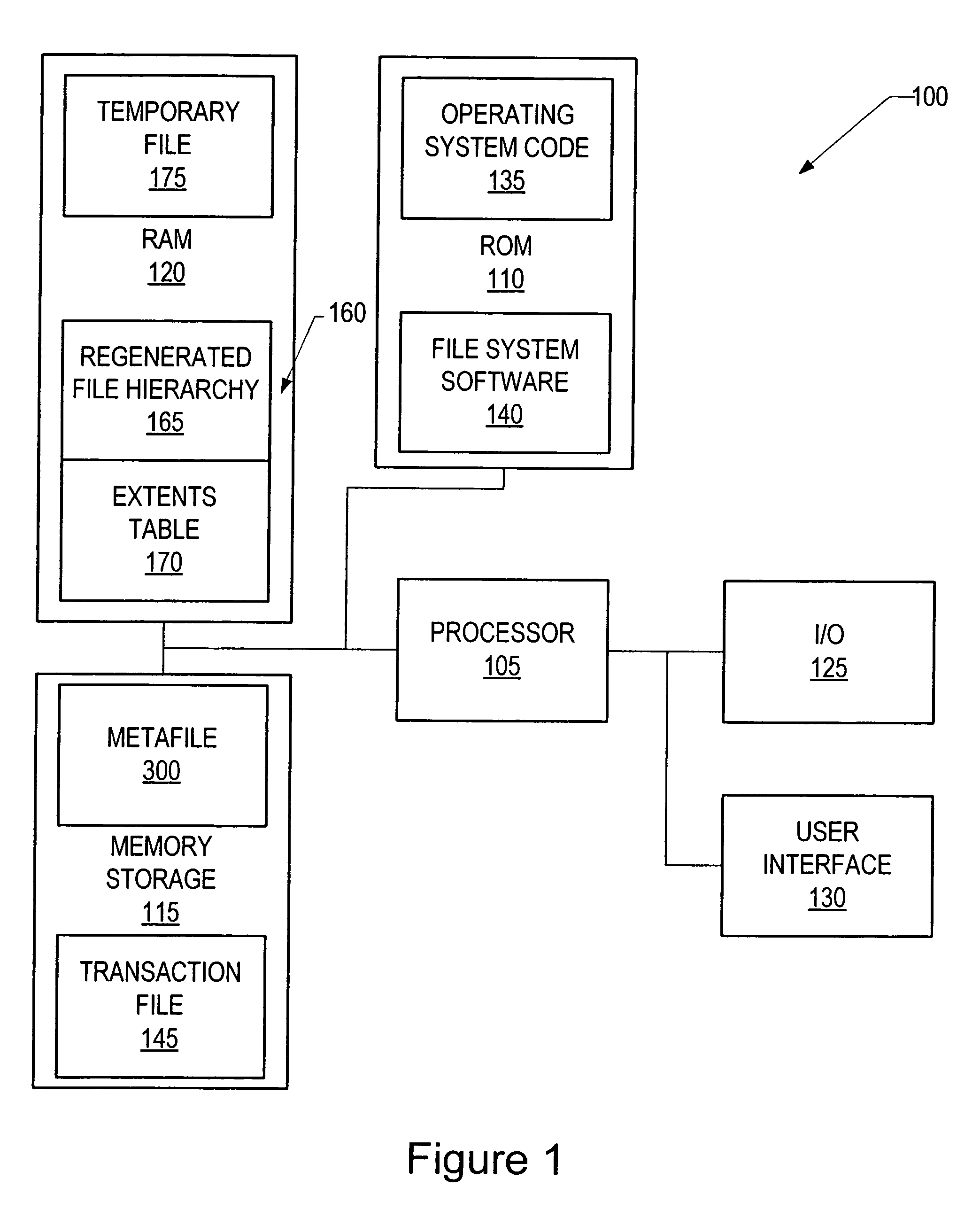

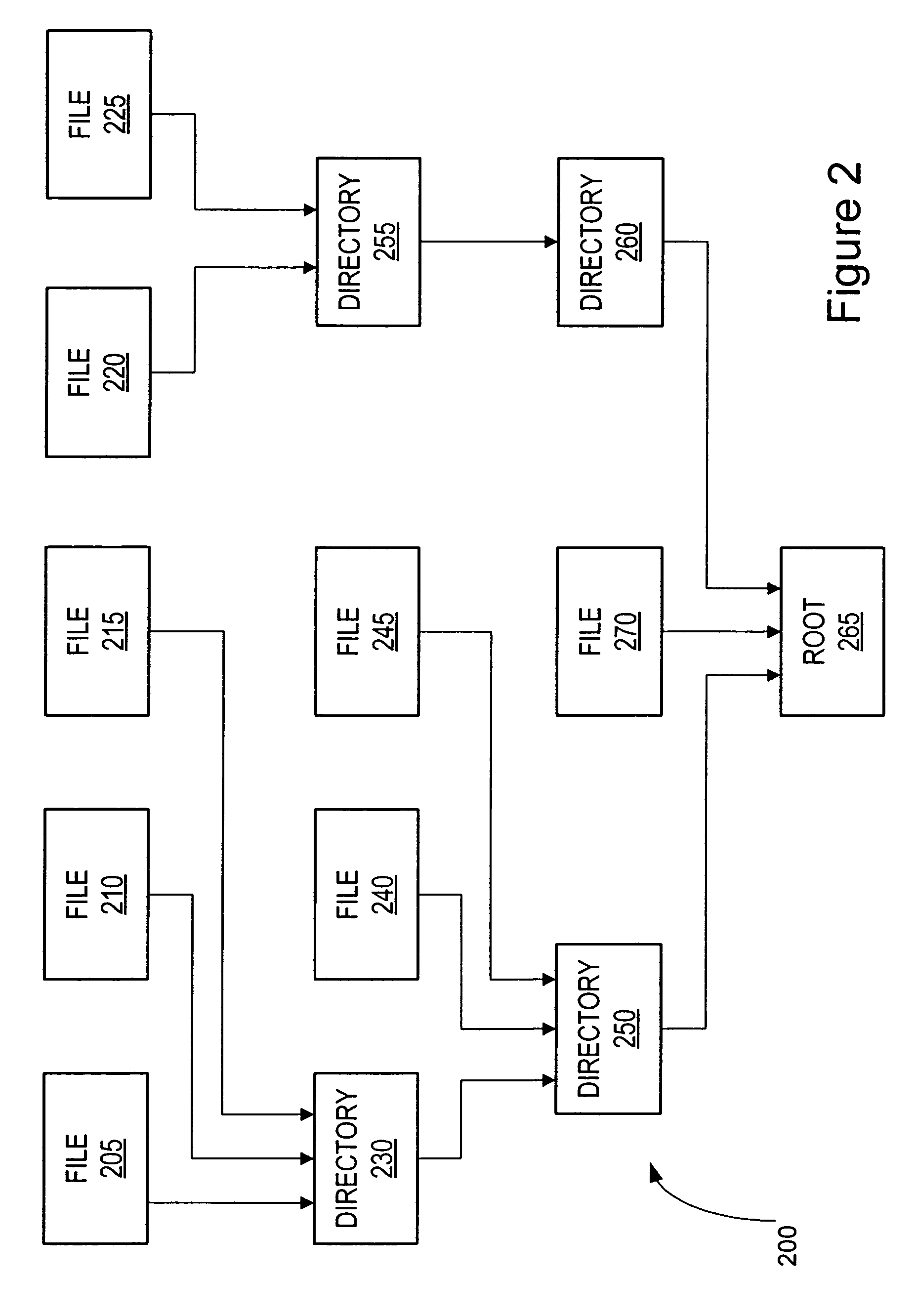

File system having transaction record coalescing

An electronic data system comprises memory storage having stored data, file system software, and a transaction file. The transaction file is maintained by the file system software, and includes a plurality of transaction records corresponding to transactions that have been or are to be executed on one or more files and / or the or more directories of the file system. The file system software operates to organize and maintain the stored data in the files and directories and also to coalesce multiple transaction records meeting one or more criteria into fewer coalesced transaction records. The physical memory space required by the transaction file is reduced by the transaction record coalescing. The coalesced transaction records may be constructed so that they represent a logical result of applying each transaction record of a transaction record set in chronological order. Once the coalesced transaction records have been committed in the file system, the physical memory used by the original transaction records in the set may be reclaimed for further use (e.g., to store further transaction records) or may be otherwise removed from further use (e.g., when the physical memory is located in a block of memory in a flash-like memory device that has reached its maximum number of write and / or erase cycles).

Owner:MALIKIE INNOVATIONS LTD

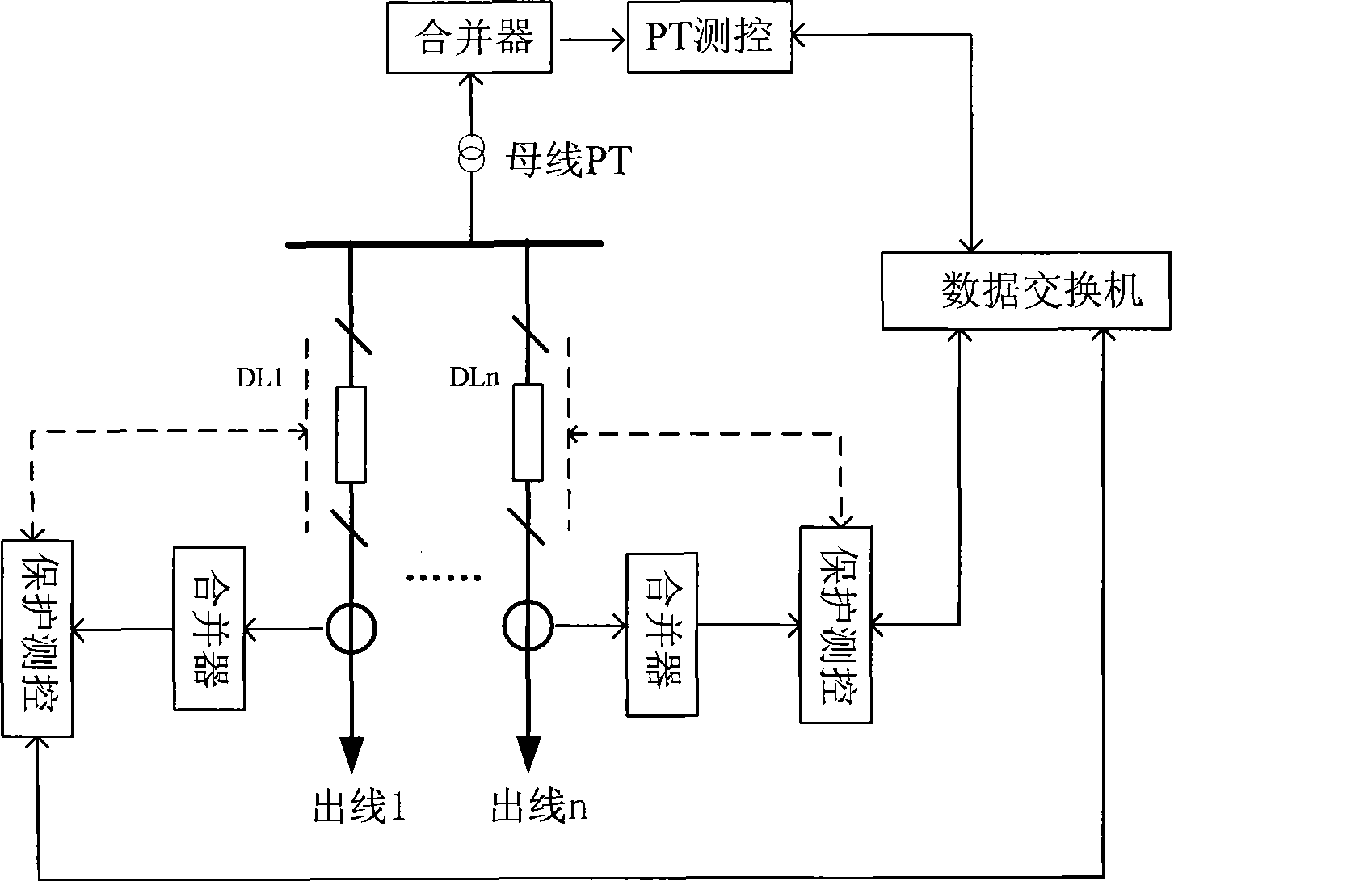

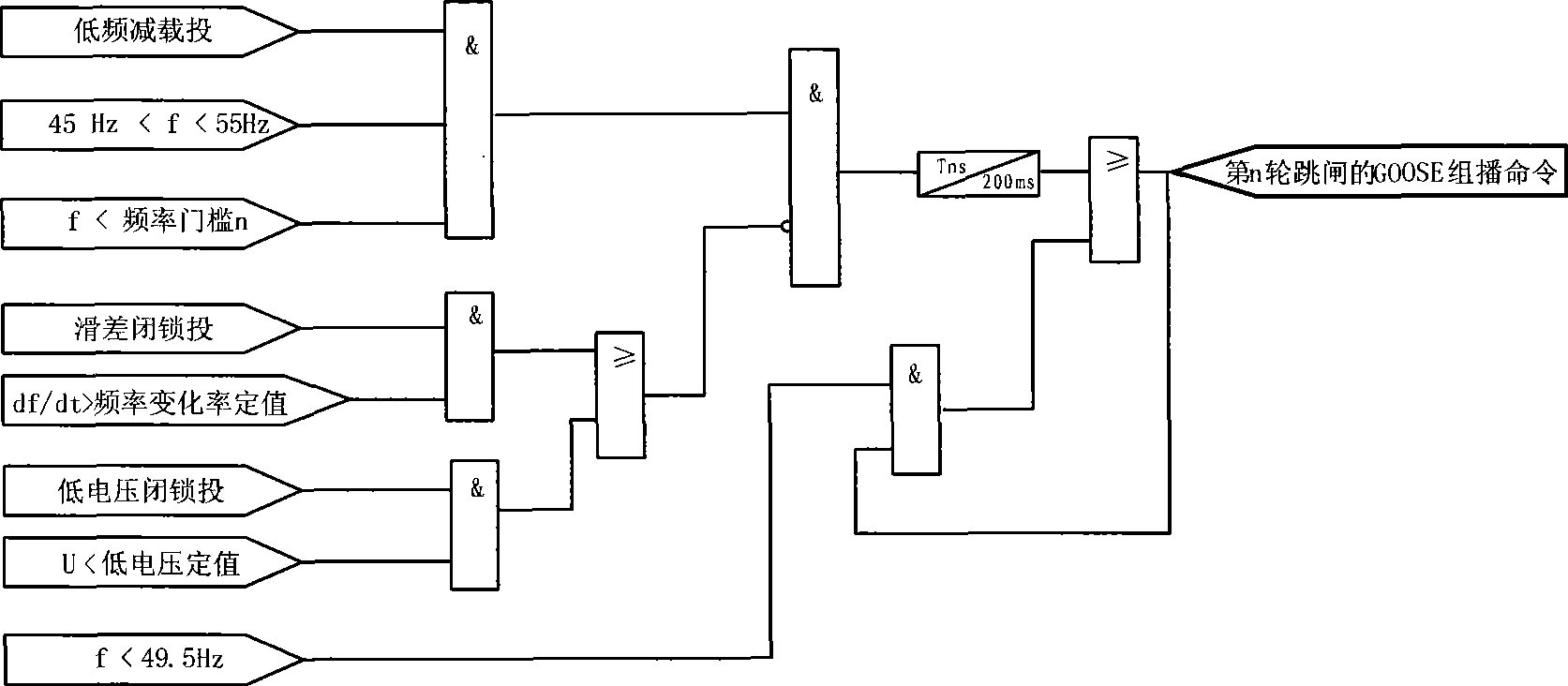

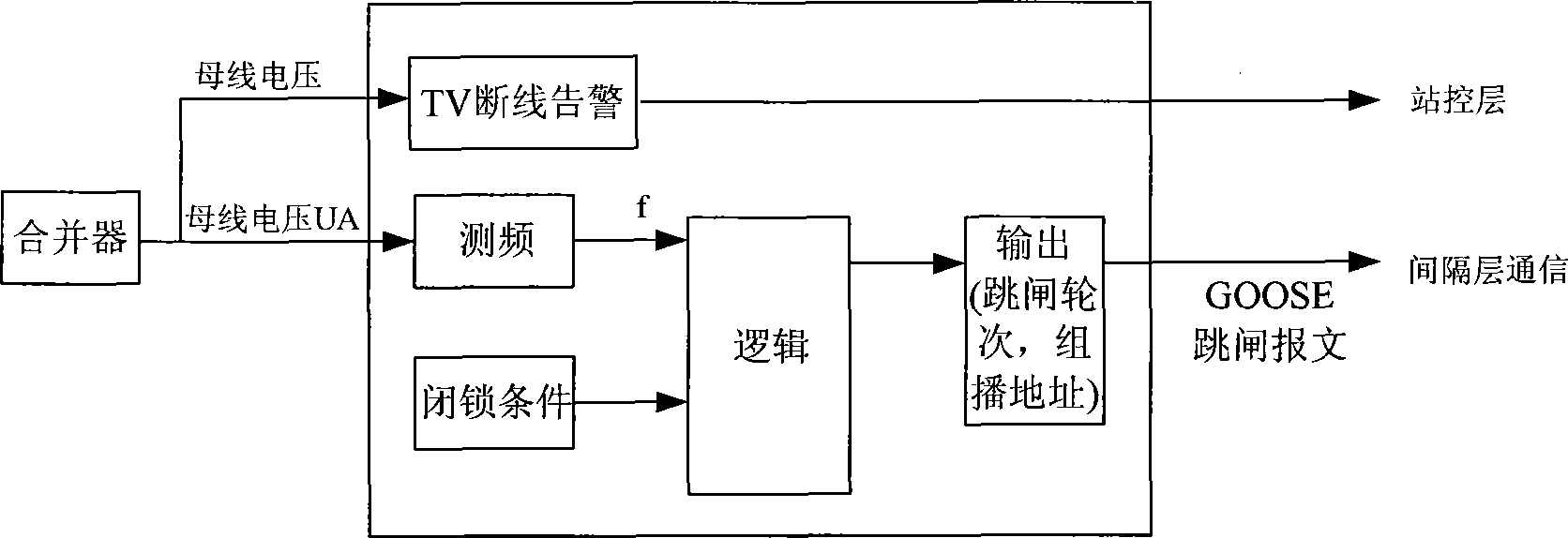

GOOSE mode network low frequency deloading method based on digital transmission network

InactiveCN101459336APower network operation systems integrationAc network voltage adjustmentDigitizationLoad following power plant

The invention relates to a GOOSE mode network low frequency load reduction method based on digital transmission network, wherein a part of outgoing line loads is removed according to given tripping runs and the changing of frequency, whole low frequency load reduction function is jointly completed by interval layer devices of different protected objects, a bus control unit is responsible for low frequency logical decision, a discriminant result is transmitted to various outgoing line control devices (dispersion execution units) in the mode of GOOSE signals through digital network, and an intelligent switch is driven by a control unit to trip and remove the loads to complete the whole logical function. Collected analog quantity is transferred to the control device by using IEC61850 standard SMV service message, and a discriminant logical result is transferred by using a GOOSE channel. The whole low frequency load reduction function can be directly used in a digital substation which is built based on IEC61850.

Owner:STATE GRID HENAN ELECTRIC POWER +1

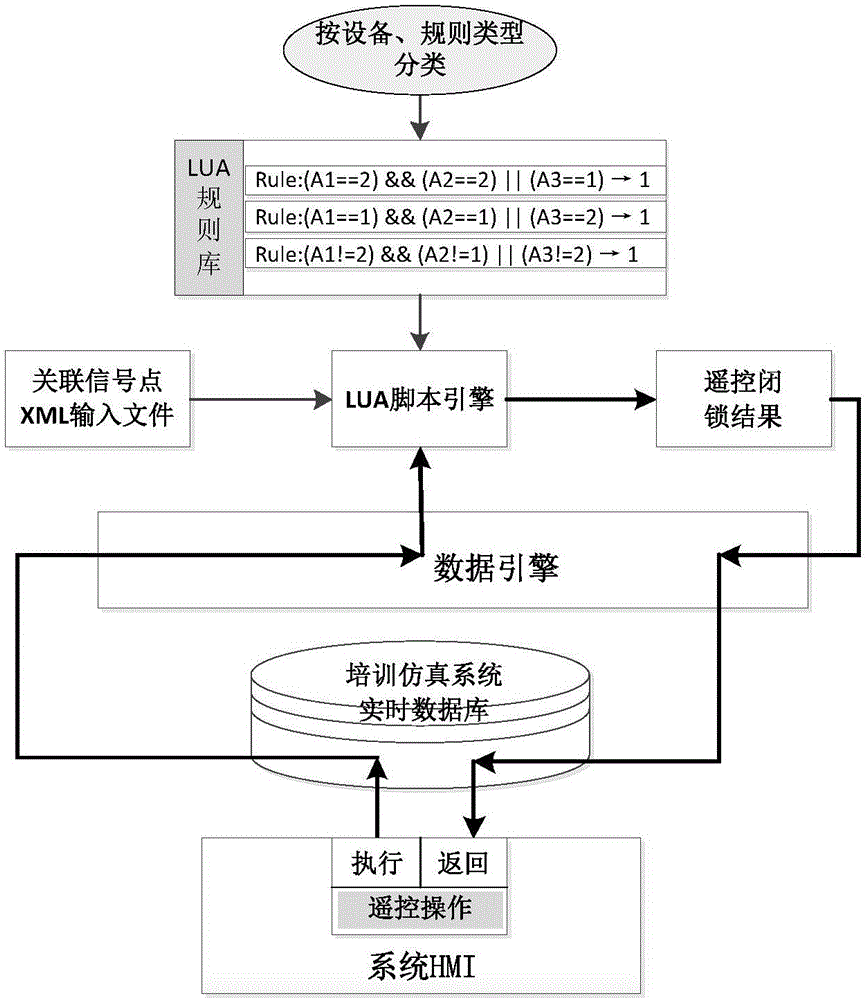

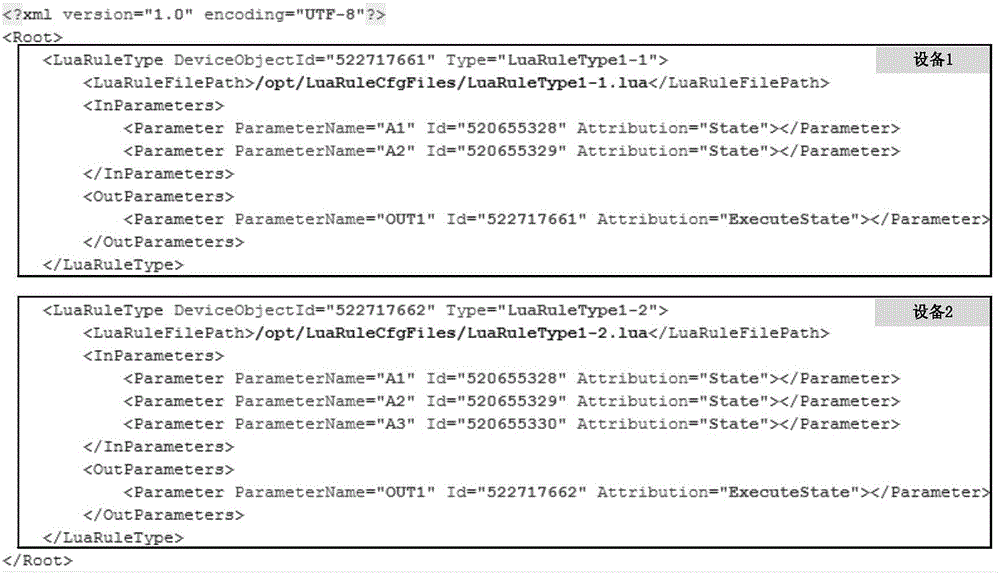

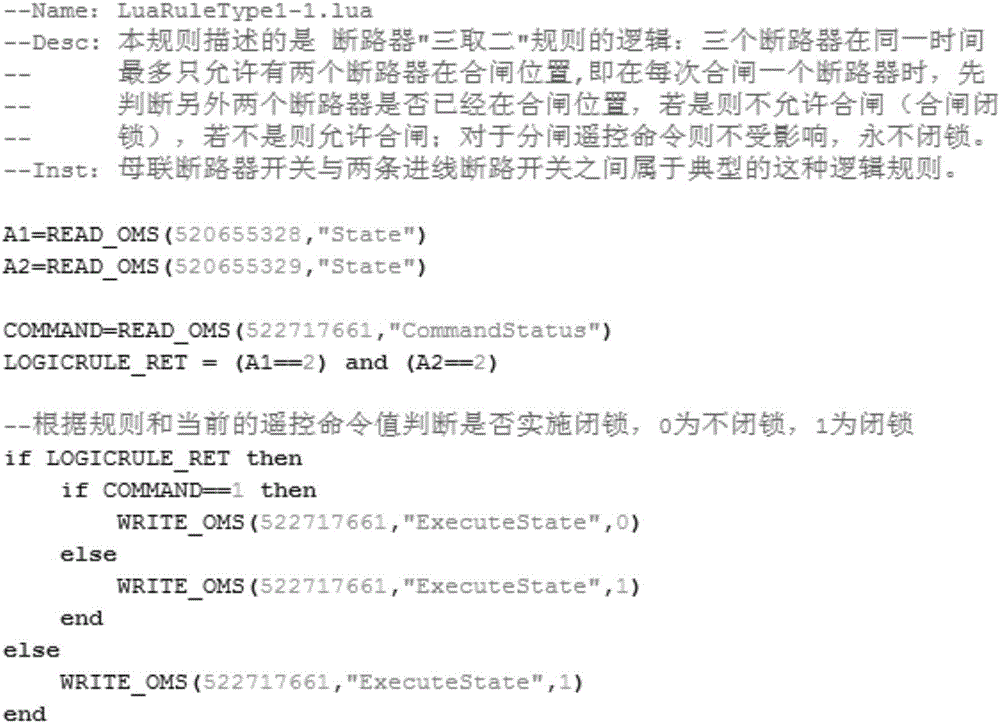

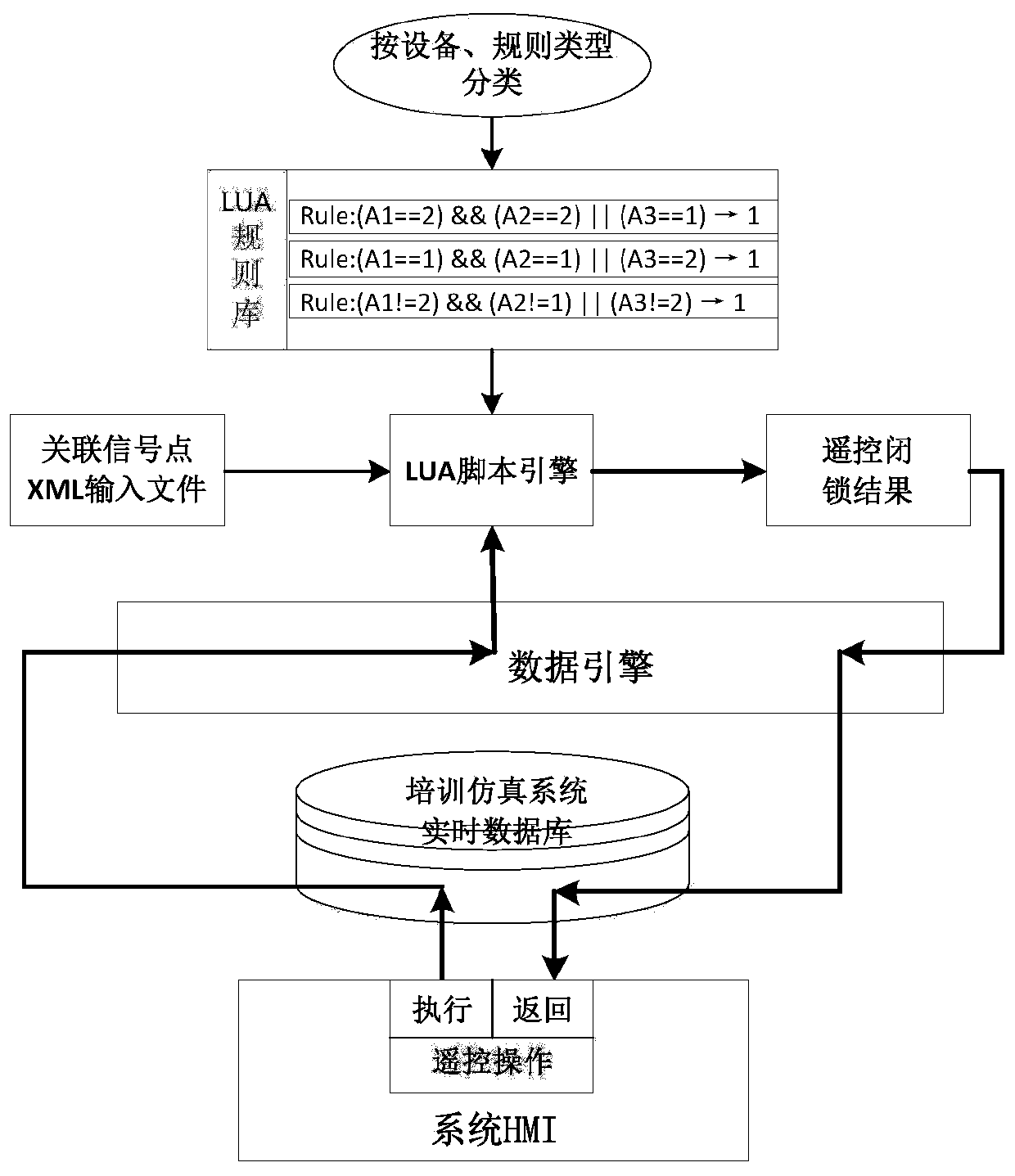

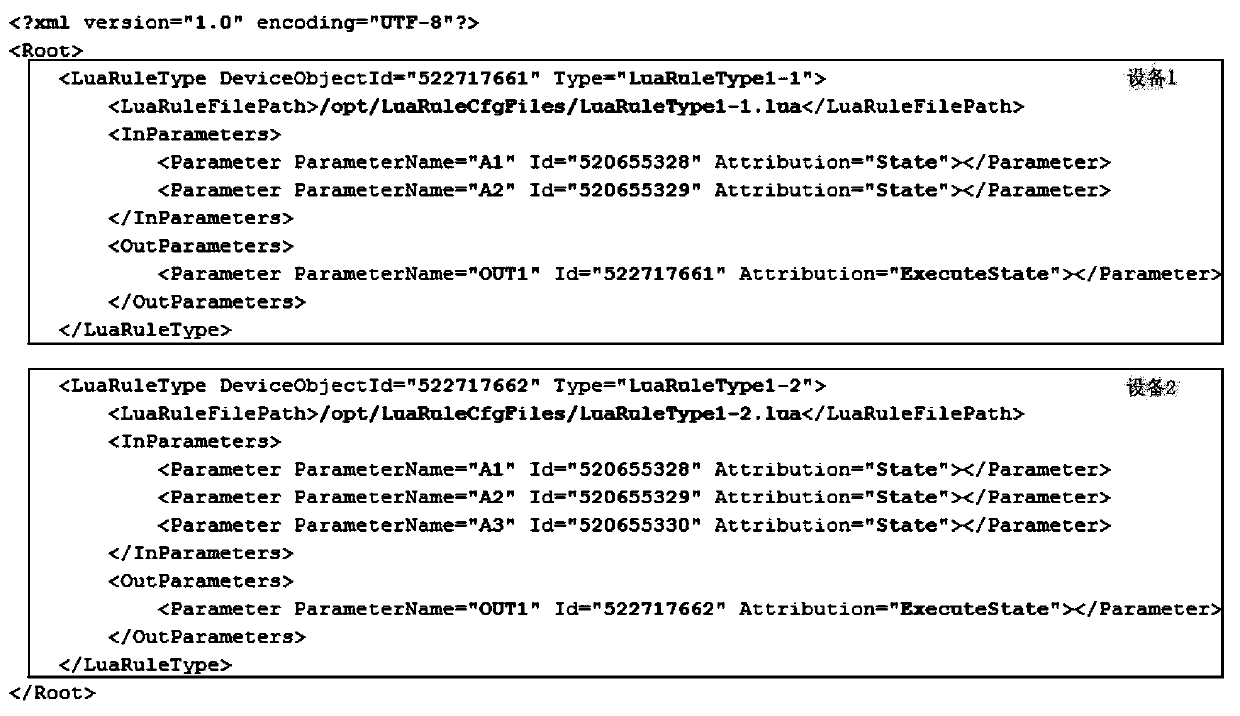

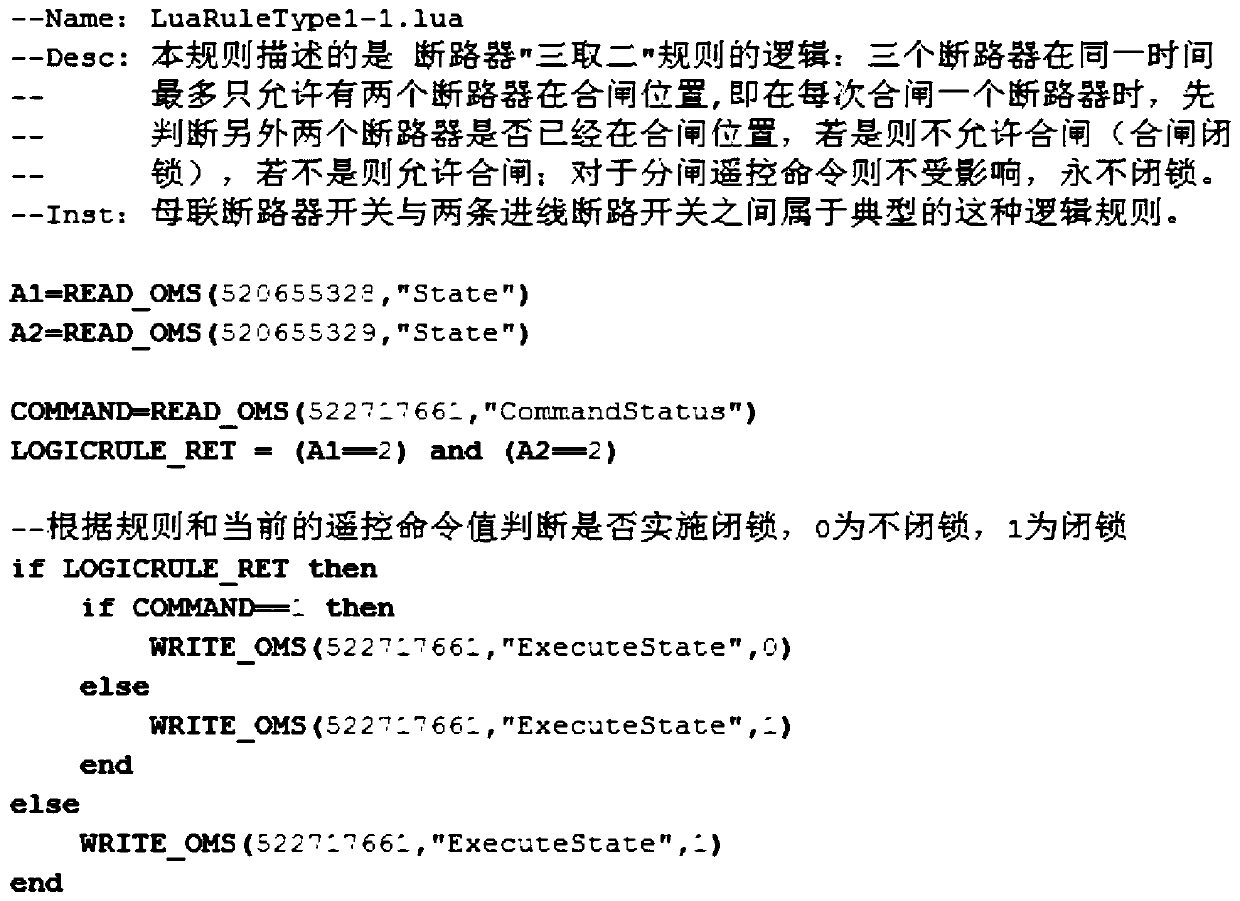

Electrical equipment remote control locking characteristic simulation method based on LUA scripts

ActiveCN106647337AAchieving associativitySimulation Realization of Remote Locking CharacteristicsSimulator controlRemote controlEngineering

The invention relates to an electrical equipment remote control locking characteristic simulation method based on LUA scripts. An operator triggers a remote control simulation operation of the electrical equipment on a system HMI interface. A system real-time library detects a remote control simulation event and submits the event to a data engine at the bottom layer of the real-time library. The data engine then submits the remote control point information to an LUA script engine. The LUA script engine retrieves the LUA script rule of the remote control point in a rule base and finds out a signal point that the electrical equipment is required to be associated with in a configured association point XML input file. The LUA script engine obtains the real-time value of the relevant signal points from the real-time library through the data engine and calculates the logical result of the rule according to the rule. If the result is 1, the remote control characteristic of the electrical equipment is satisfied and the remote control is performed normally. Otherwise, it does not meet the remote control characteristics of the electrical equipment, the current remote control is rejected. The result whether to meet the remote control locking characteristic is written in the real-time library by the data engine, and is ultimately fed to the system HMI interface.

Owner:南京国电南自轨道交通工程有限公司

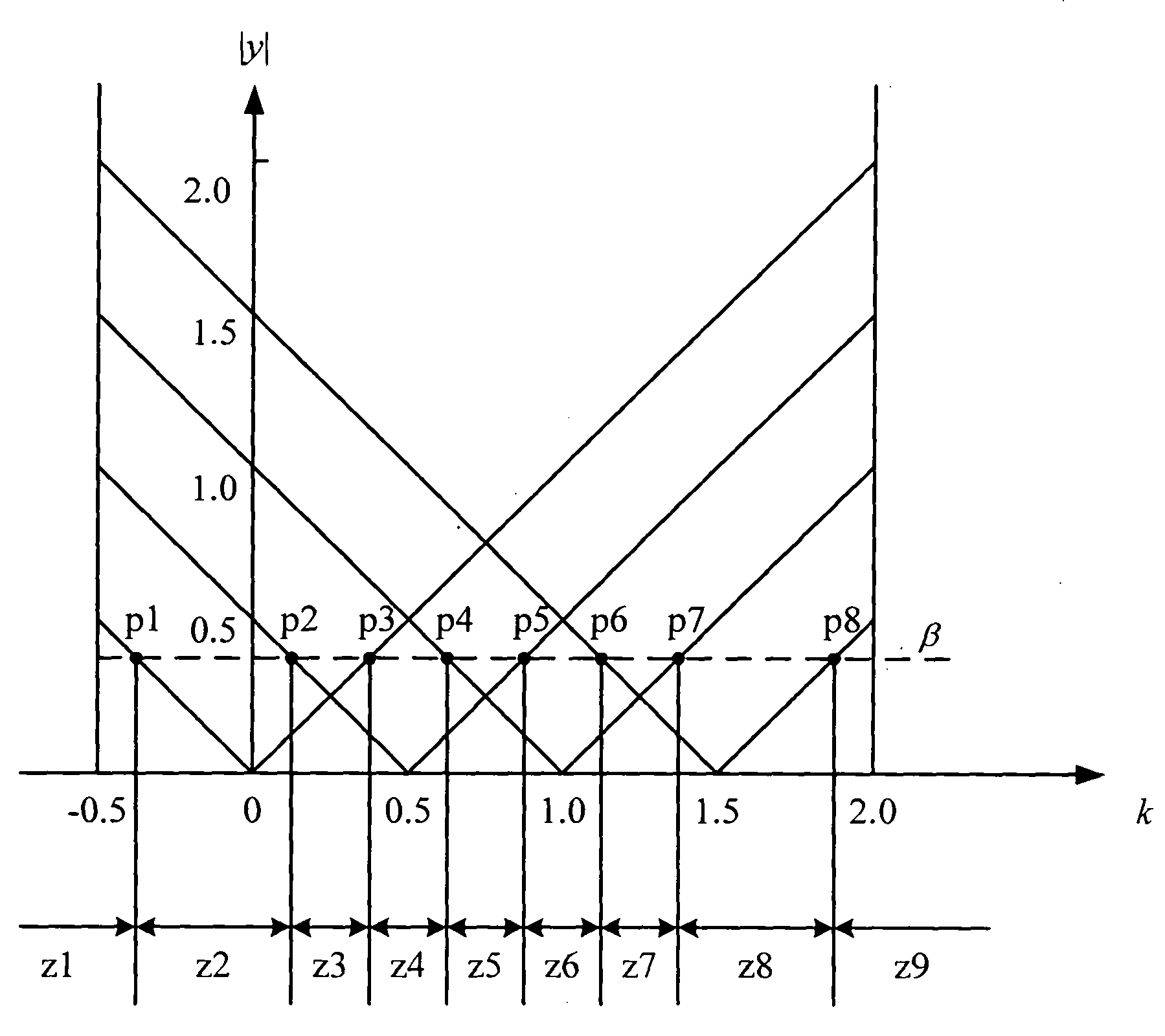

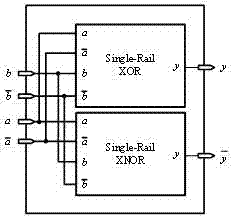

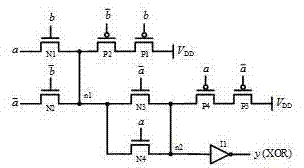

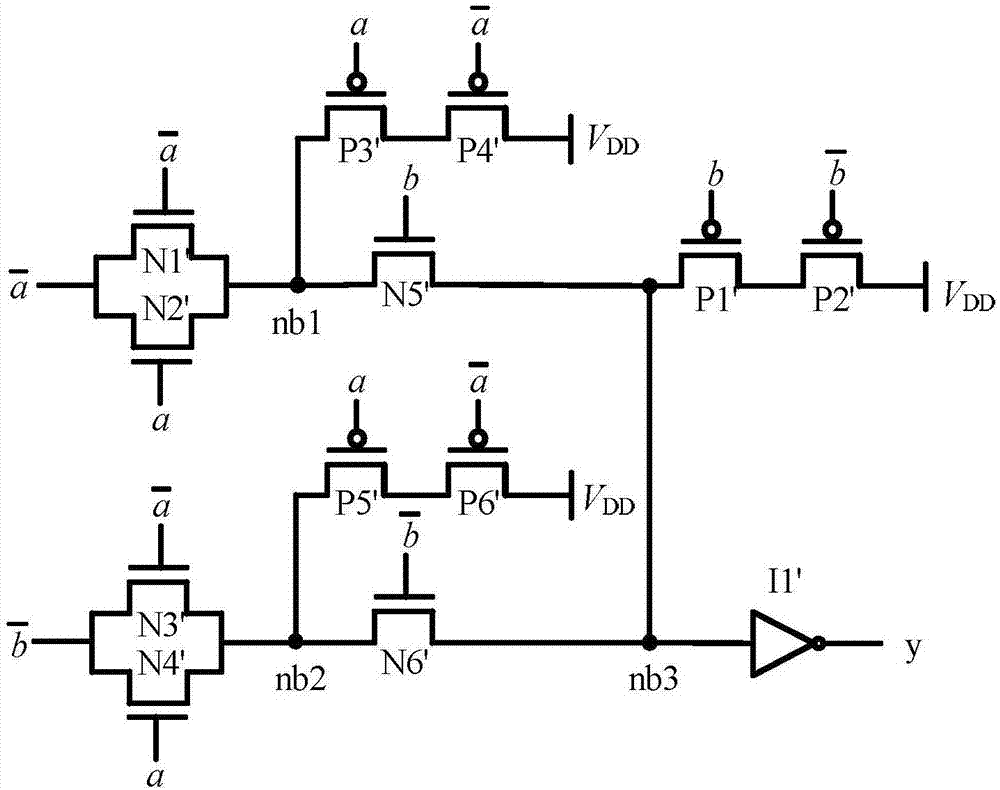

XNOR-XOR double-rail pre-charge logic unit

ActiveCN104333362AGood symmetryBalanced power consumptionElectronic switchingMemory effectPre-charge

The invention relates to an XNOR-XOR double-rail pre-charge logic unit and belongs to the field of circuit electronics. The XNOR-XOR double-rail pre-charge logic unit comprises a single-rail XOR logic circuit and a single-rail XNOR logic circuit complementing the single-rail XOR logic circuit. The two circuits are each provided with four input ends respectively connected with four input signals a, a<->, b and b<->; the output signal y of the single-rail XOR logic circuit is an XOR logic result of the input signals a and b; and the output signal y<-> of the single-rail XNOR logic circuit is an XNOR logic result of the input signals a and b. According to the invention, under the condition of not large area expenditure, power consumption of nodes inside a logic unit can be effectively balanced, the memory effect of the internal nodes is eliminated, the problem of early spreading effect of the XNOR-XOR double-rail pre-charge logic unit is effectively solved, and safe and effective XNOR-XOR logic is realized.

Owner:HARBIN INST OF TECH AT WEIHAI

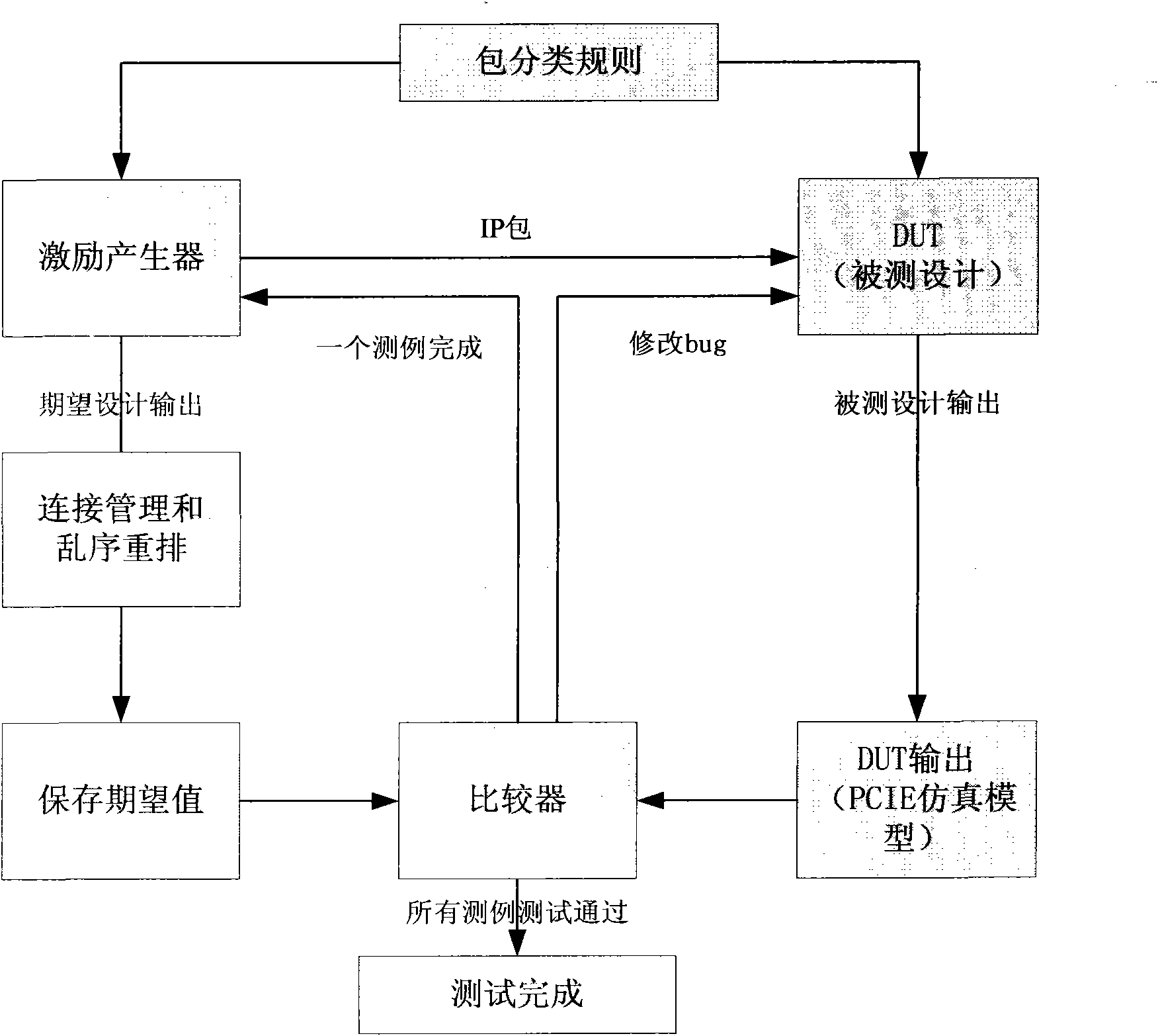

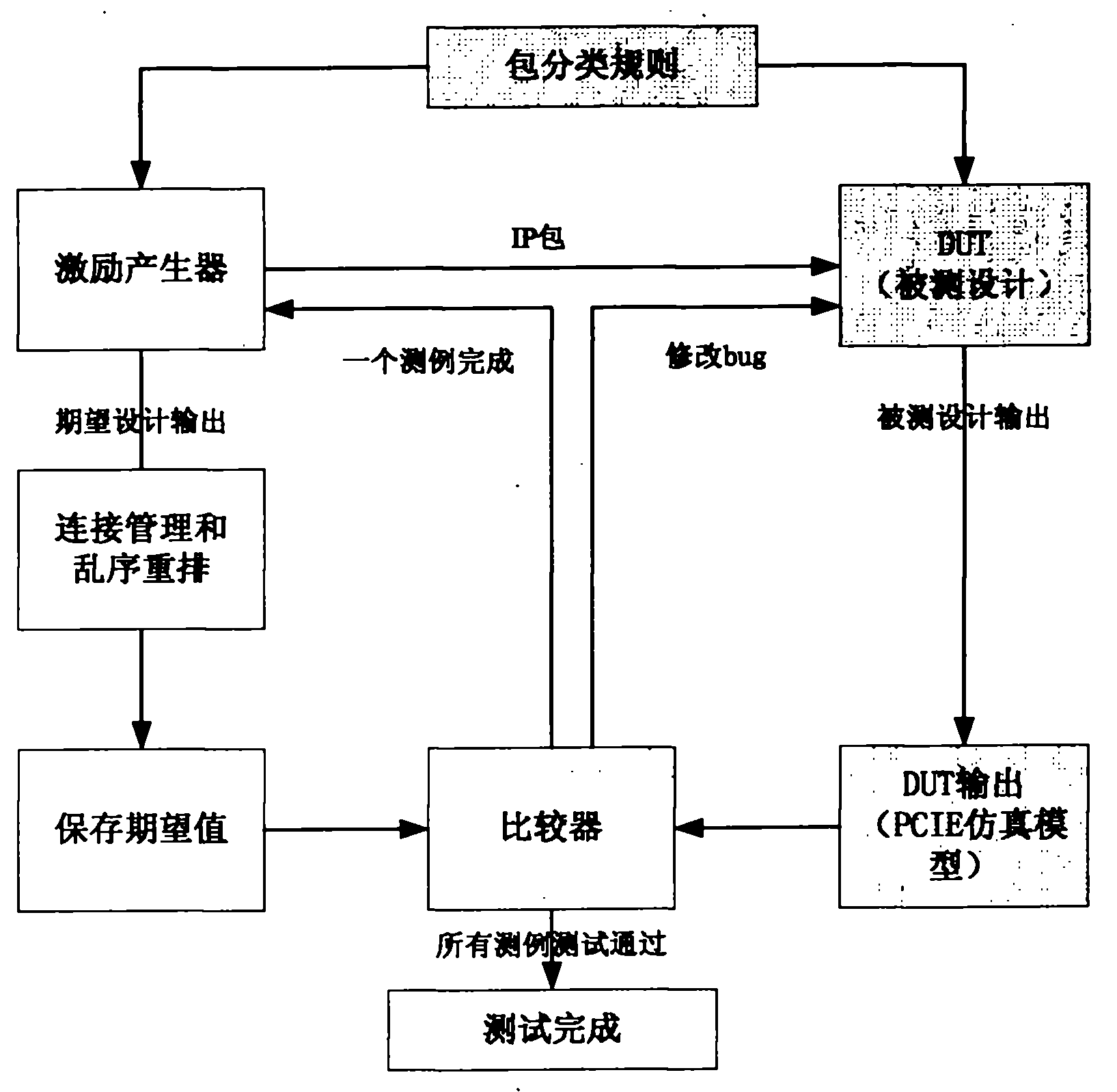

TCP (transmission control protocol) stream based verification method

InactiveCN102096619AImprove design qualityShorten development timeLogical operation testingValidation methodsComputer module

The invention provides a TCP (transmission control protocol) stream based verification method. An exciter continuously generates constrained random TCP connection based network packet structures comprising various abnormal connection conditions, a logic task is enabled, and an automatic comparator receives a logic output result and saves the logic output result into a logic result buffer zone; a connection management module records connection status, a rearrangement module performs unordered rearrangement according to the result of the management module, and the automatic comparator saves the result into an expected buffer zone; and the automatic comparator automatically compares the result of the result buffer zone and the result of the expected buffer zone to verify whether the logic result is correct. In the invention, comprehensive logic function verification is carried out before board-level test to correct a potential bug, improve the design quality and reduce the project development time.

Owner:SUGON INFORMATION IND

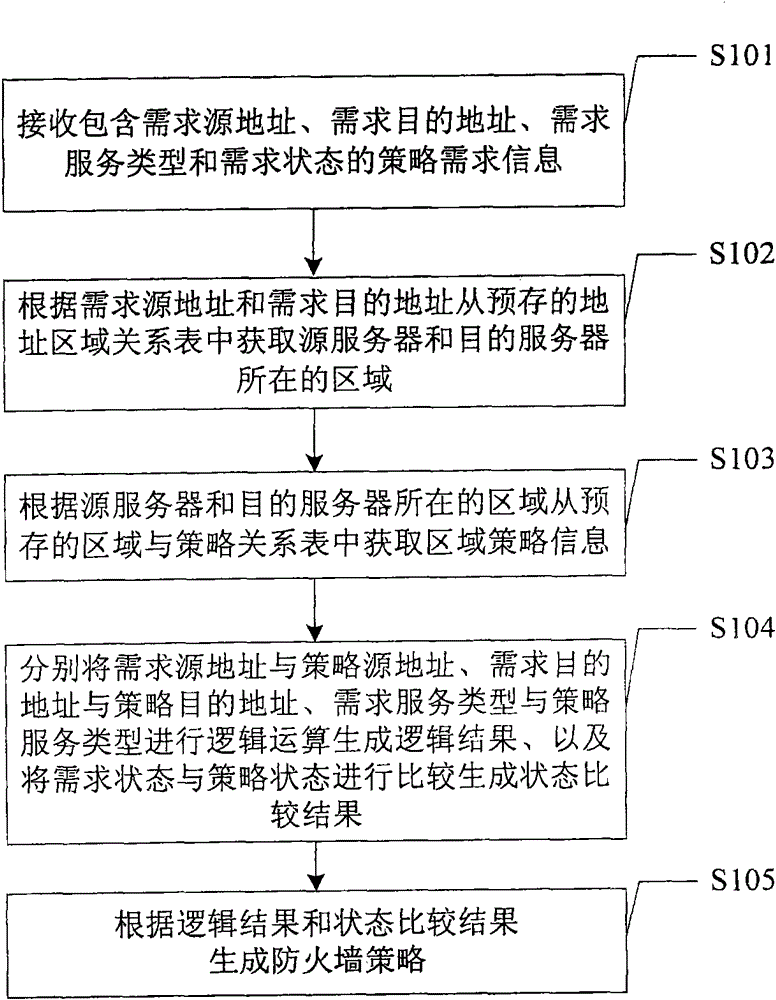

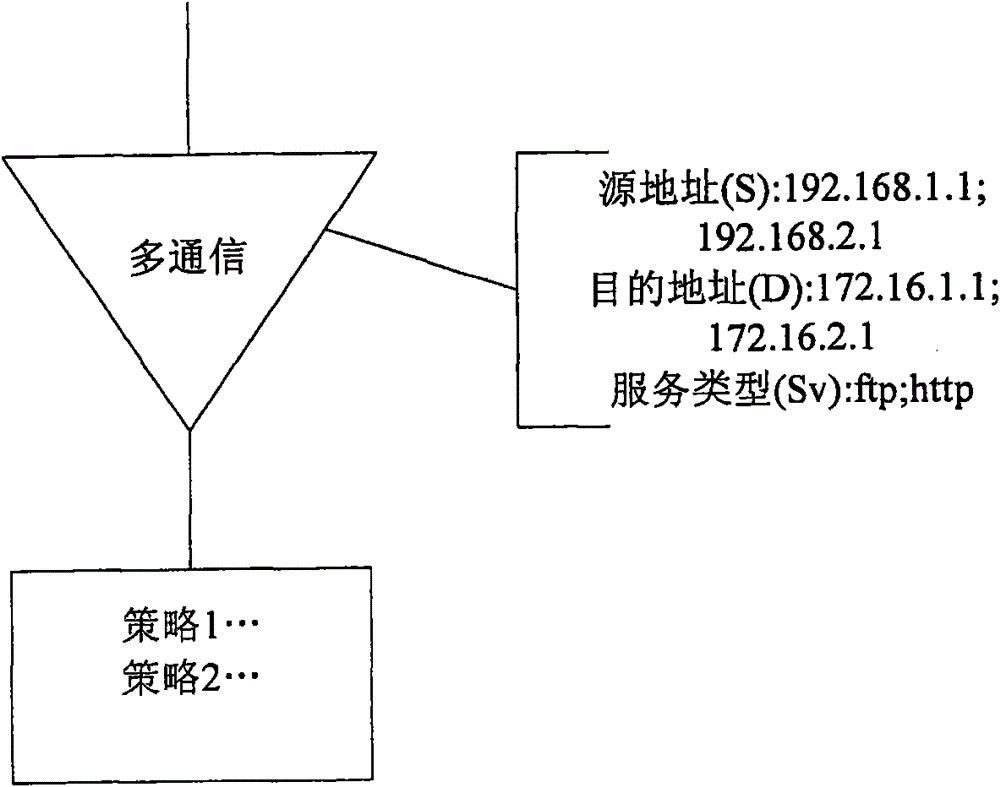

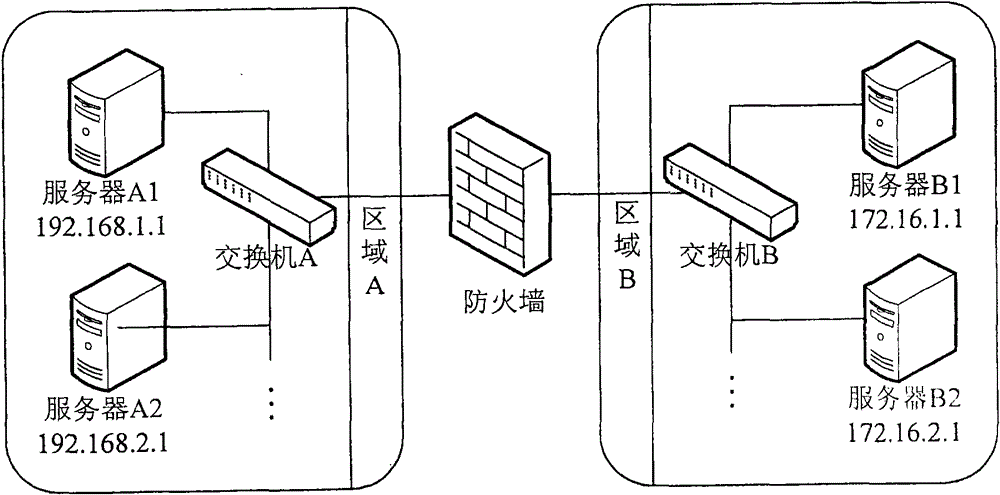

Firewall strategy-generating method, device and system

The invention provides firewall strategy-generating method, device and system. The firewall strategy-generating method comprises the following steps: receiving strategy demand information containing a demand source address, a demand destination address and a demand service type; acquiring the regions of a source server and a destination server from a prestored address region relation table according to the demand source address and the demand destination address; acquiring region strategy information from a prestored region and strategy relation table according to the regions of the source server and the destination server, wherein the region strategy information corresponds to the regions of the source server and the destination server and contains a strategy source address, a strategy destination address and a strategy service type; logically calculating the demand source address and the strategy source address to generate a source address logic result; logically calculating the demand destination address and the strategy destination address to generate a destination address logic result; logically calculating the demand service type and the strategy service type to generate a service type logic result; and generating a firewall strategy according to the source address logic result, the destination address logic result, the service type logic result and the relation between a demand state and a strategy state.

Owner:INDUSTRIAL AND COMMERCIAL BANK OF CHINA

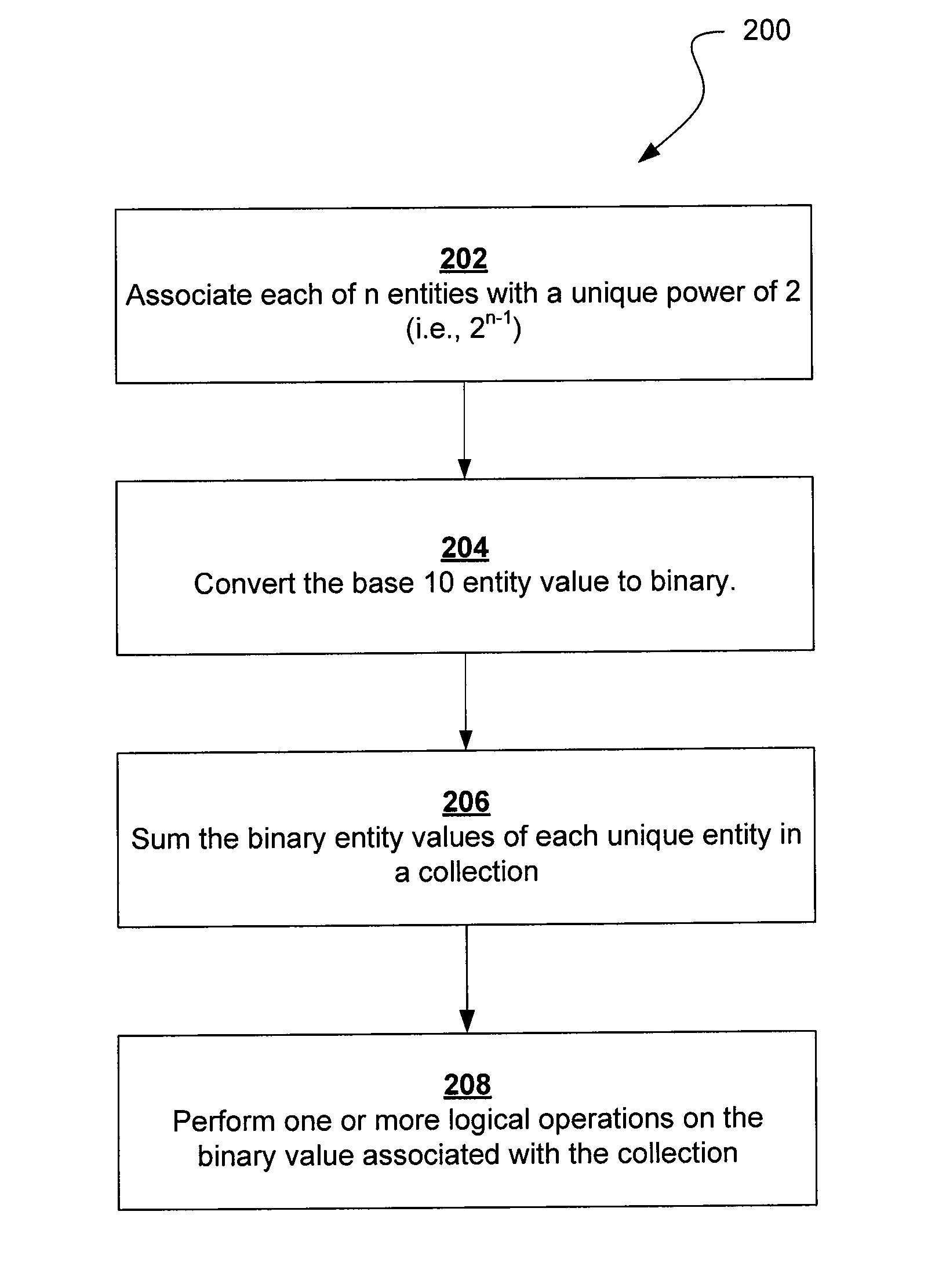

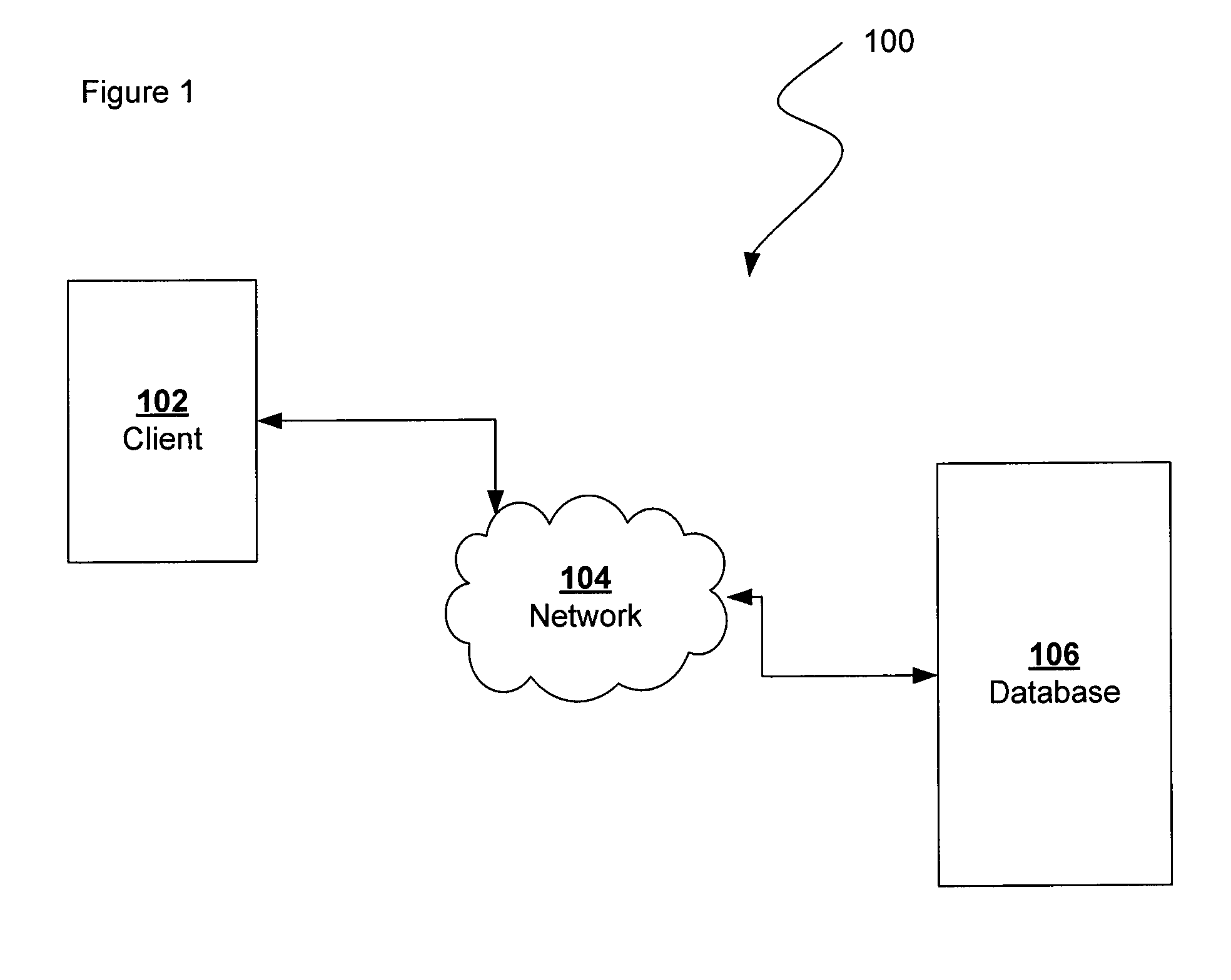

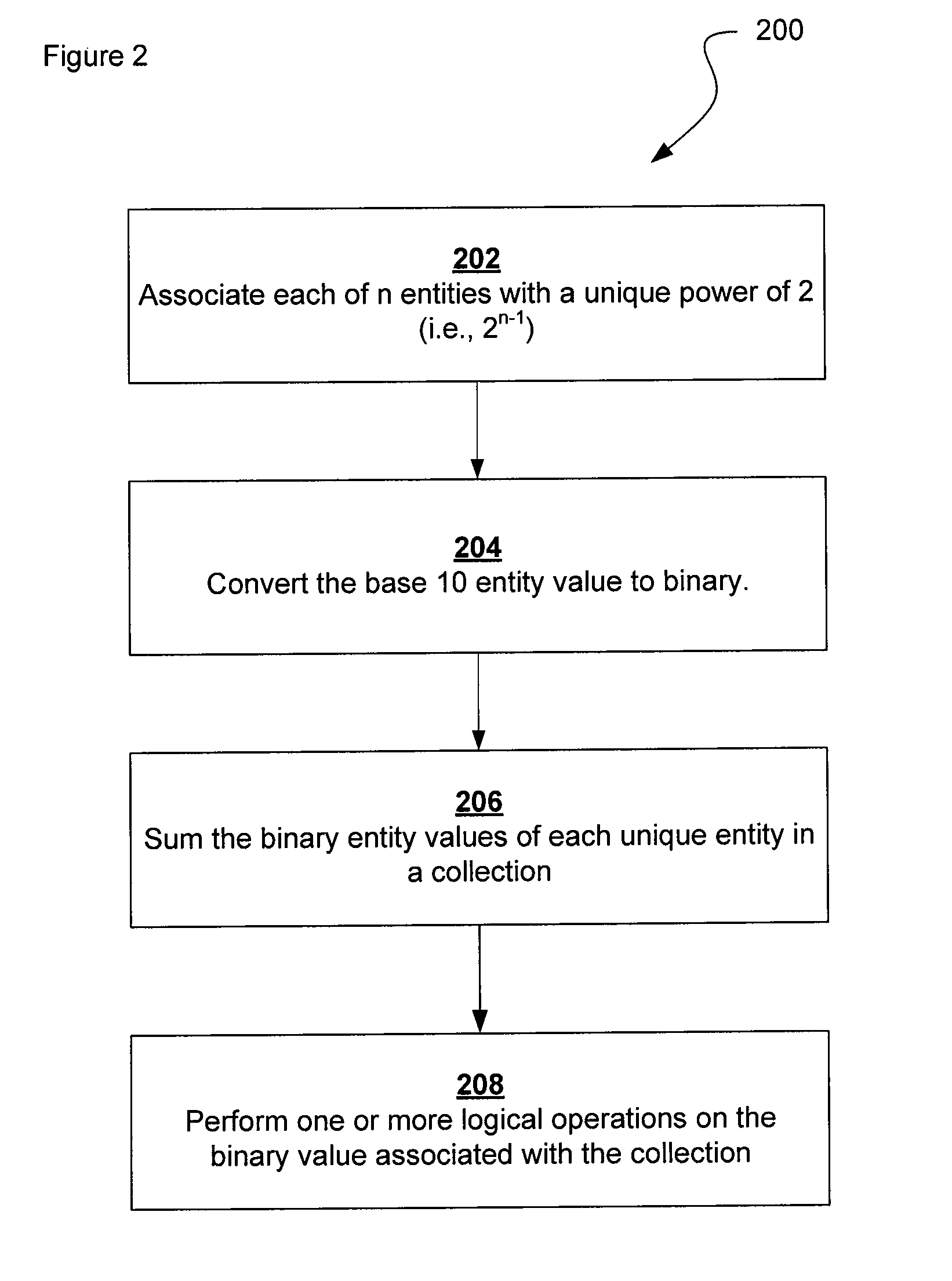

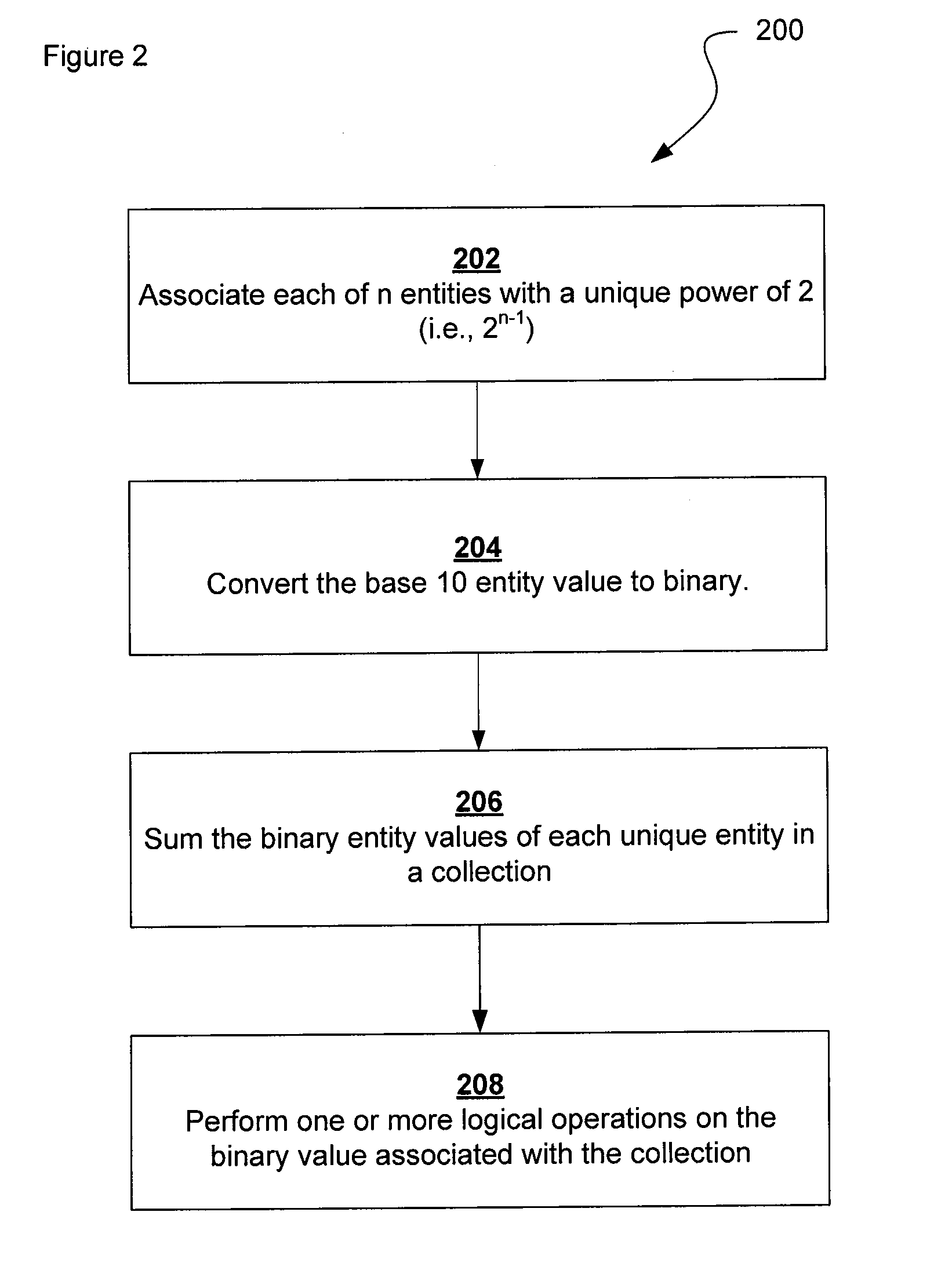

Systems and methods for lossless compression of data and high speed manipulation thereof

The present disclosure includes a system, method, and article of manufacture for lossless compression of data and high speed manipulation thereof. The method may comprise associating one or more of a plurality of unique entities with one or more of a plurality of unique binary numbers; associating a collection with the plurality of unique entities; and determining that the collection includes one of the plurality of unique entities based upon the unique binary number associated with the unique entity. The associating the collection with the plurality of unique entities may further comprise summing the unique binary numbers associated with the plurality of unique entities, and / or associating the collection with a binary number that is a logical result of a bitwise operation between unique binary numbers associated with the plurality of unique entities.

Owner:LIBERTY PEAK VENTURES LLC

Systems and methods for lossless compression of data and high speed manipulation thereof

InactiveUS20120278506A1Increase speedDigital data processing detailsCode conversionBitwise operationLossless compression

The present disclosure includes a system, method, and article of manufacture for lossless compression of data and high speed manipulation thereof. The method may comprise associating one or more of a plurality of unique entities with one or more of a plurality of unique binary numbers; associating a collection with the plurality of unique entities; and determining that the collection includes one of the plurality of unique entities based upon the unique binary number associated with the unique entity. The associating the collection with the plurality of unique entities may further comprise summing the unique binary numbers associated with the plurality of unique entities, and / or associating the collection with a binary number that is a logical result of a bitwise operation between unique binary numbers associated with the plurality of unique entities.

Owner:LIBERTY PEAK VENTURES LLC

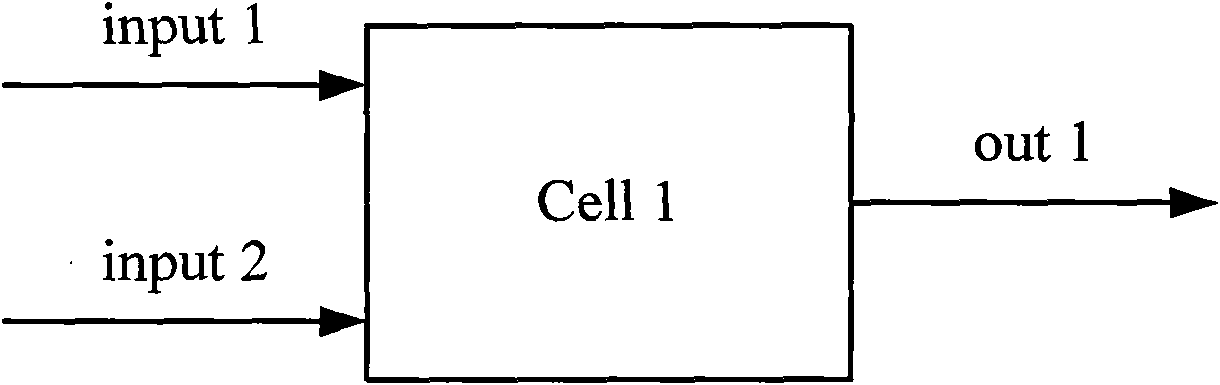

Dynamic logical gate circuit

InactiveCN101951257AHigh Logic Conversion SpeedRich and varied logical resultsLogic circuits characterised by logic functionPotential wellWeight coefficient

The invention discloses a reconfigurable dynamic logical gate circuit which can carry out dynamic conversion among various logical functions. The circuit comprises a first input end, a second input end, a third input end, an operational circuit and an output end, wherein the first input end is used for receiving input signals; the second input end is used for receiving weighting coefficients for weighting the input signals and is also used for receiving potential well parameters; the third input end is used for receiving control instructions; the operational circuit is respectively connected with the first input end, the second input end and the third input end and is used for acquiring the logical operation results of the dynamic logical gate circuit according to the input signals, the weighting coefficients, the control instructions and the potential well parameters; and the output end is connected with the operational circuit and is used for outputting the logical operation results. The invention realizes the technology of the dynamic logical gate circuit which can carry out fast conversion among various logical functions. The technical scheme of the invention has higher logical conversion speed, and logical results are various.

Owner:BEIJING UNIV OF POSTS & TELECOMM

Soft certification anti-false method based on graphic code primary and secondary signet series information association mechanism

InactiveCN1321507CEasy to identifyEasy to see throughUser identity/authority verificationCo-operative working arrangementsGraphicsHuman sense

This invention is a kind of soft certification false proof method that based on graphic code primary and secondary seal family information association mechanism. The primary and secondary seal family of the certification embeds the knowledge-type privacy character information of certification holder. There is some logic constrained relation between the primary and secondary seal information, and can stop the counterfeit and fraud. The non-simulation capability of this certification is decided by the logic result of key and knowledge character information of certification holder, and doesn't relate to the technique and equipment. So the technical regulation can be an open system. This invention also replaces the high-cost physical equipment process complexity method with the low-cost logic calculus complexity method. And replaces the human sense identifying and other technical method with the electronic information processing method.

Owner:中国科学院成都计算机应用研究所

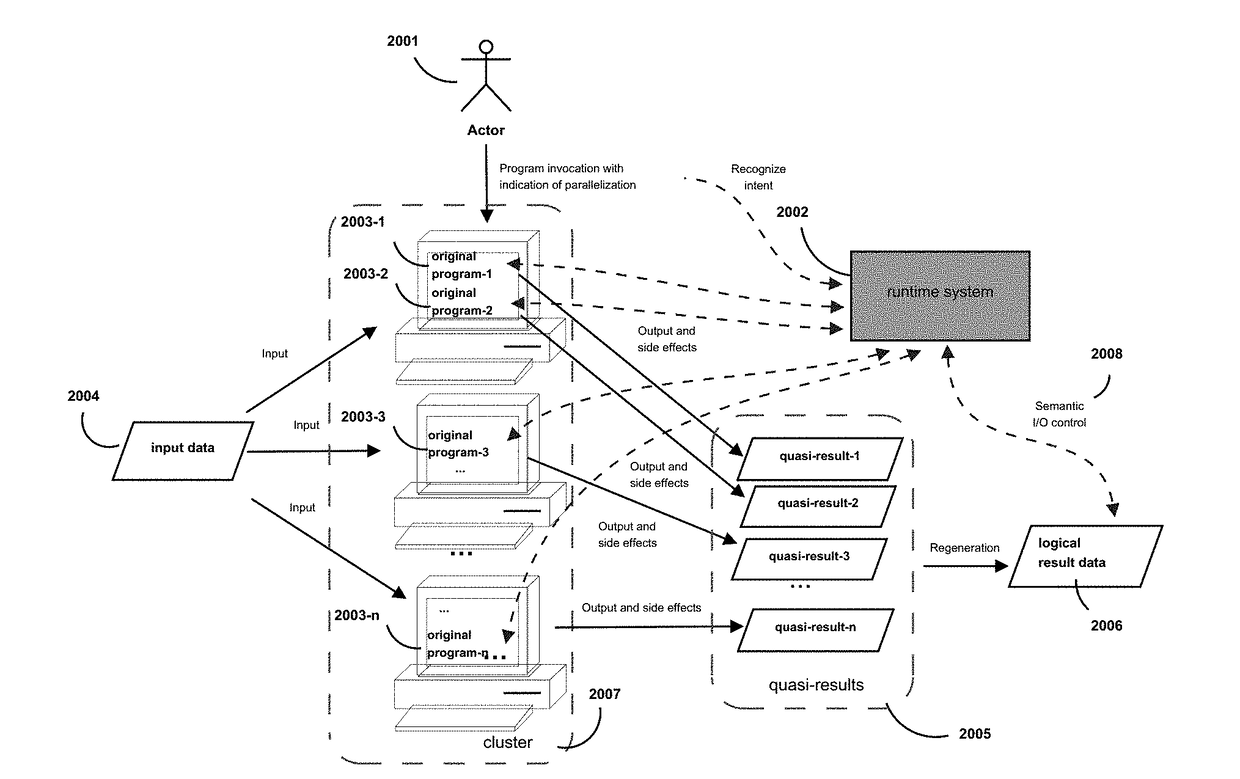

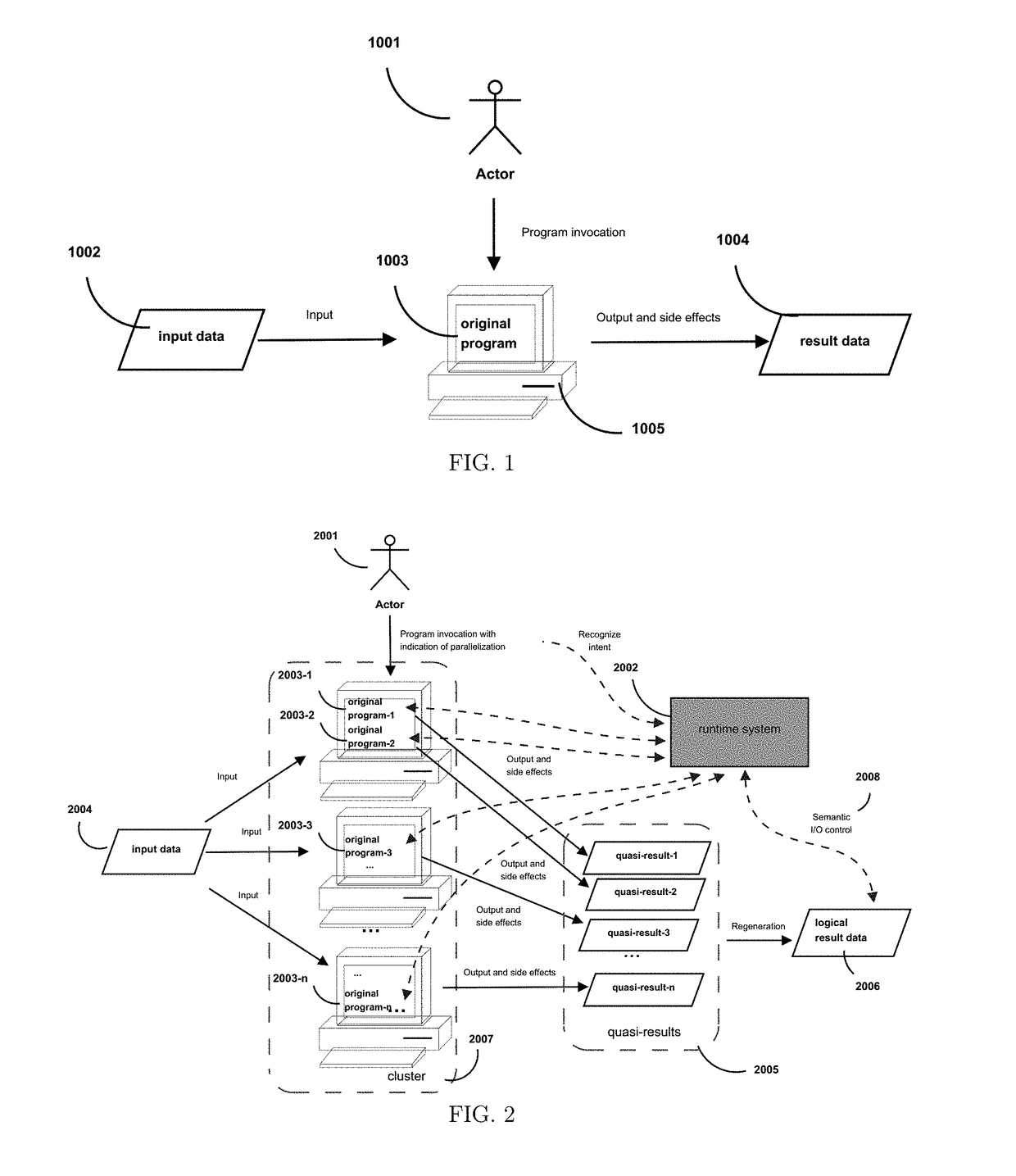

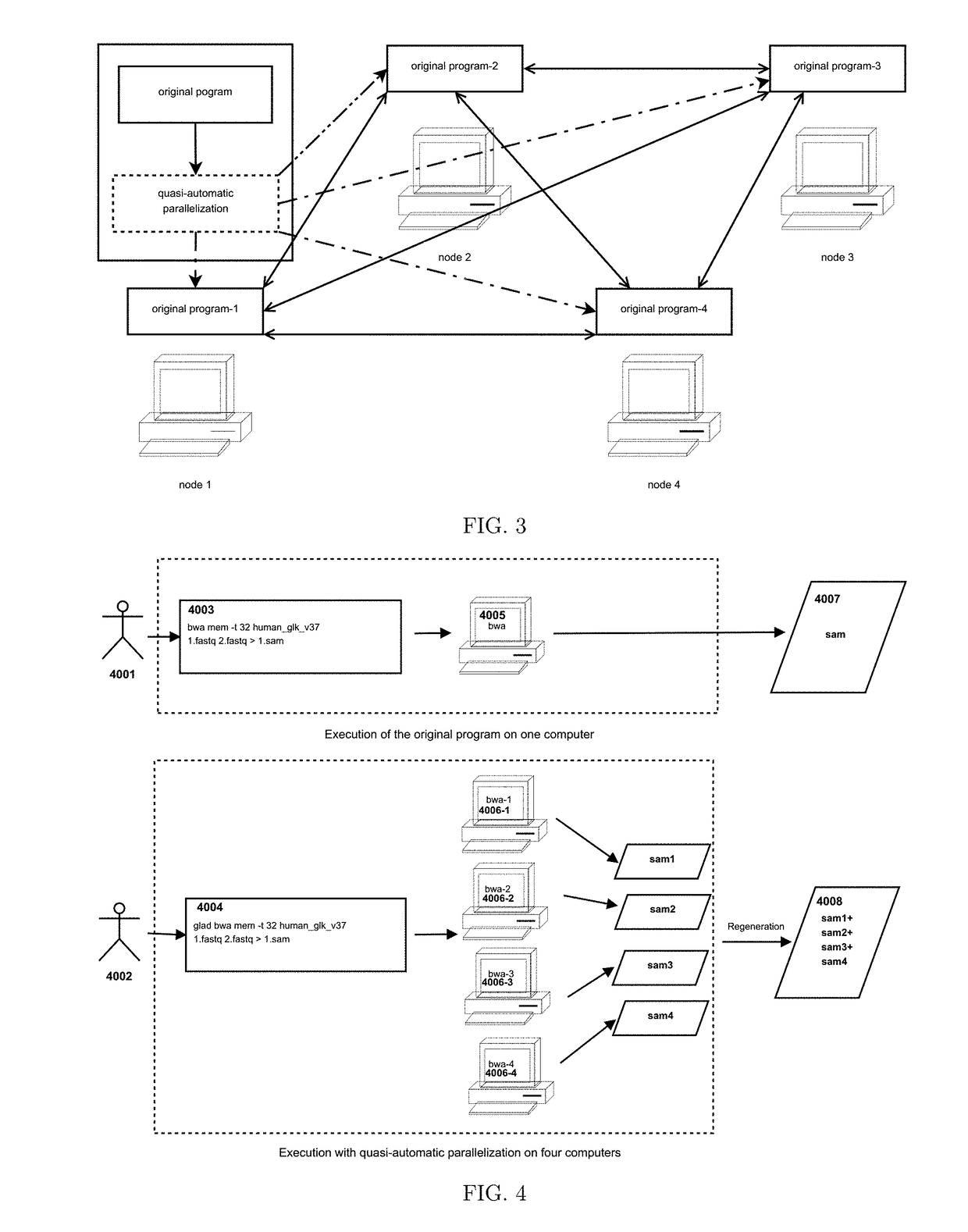

Method for Quasi-automatic Parallelization of Application Programs

InactiveUS20180157526A1Reduce difficultyIncrease the amount of calculationProgram initiation/switchingSoftware engineeringSemanticsApplication software

A quasi-automatic method is provided to parallelize user programs with little or no changes in their original design, implementation or compiled binary code. The users issues a simple indication to inform a runtime system about the intent to run the programs in a parallel or distributed manner, and the runtime system executes a plurality of programs based on the original program to conduct the same computation with parallelization. The semantics of the original program is reused, and task instances are created based on the semantics and executed in parallel or distributedly. The method provides an easy yet reliable method for accelerating computation by distributing the original program processes on multiple computers. Through a semantics-aware I / O control and coordination, the runtime system improves the consistency between the logical result data generated by the parallel computation and the expected result data from the original program should it be executed on one computer.

Owner:GU LIN +3

Dynamic logical gate circuit

InactiveCN101951257BHigh Logic Conversion SpeedRich and varied logical resultsLogic circuits characterised by logic functionPotential wellWeight coefficient

The invention discloses a reconfigurable dynamic logical gate circuit which can carry out dynamic conversion among various logical functions. The circuit comprises a first input end, a second input end, a third input end, an operational circuit and an output end, wherein the first input end is used for receiving input signals; the second input end is used for receiving weighting coefficients for weighting the input signals and is also used for receiving potential well parameters; the third input end is used for receiving control instructions; the operational circuit is respectively connected with the first input end, the second input end and the third input end and is used for acquiring the logical operation results of the dynamic logical gate circuit according to the input signals, the weighting coefficients, the control instructions and the potential well parameters; and the output end is connected with the operational circuit and is used for outputting the logical operation results. The invention realizes the technology of the dynamic logical gate circuit which can carry out fast conversion among various logical functions. The technical scheme of the invention has higher logical conversion speed, and logical results are various.

Owner:BEIJING UNIV OF POSTS & TELECOMM

Simulation method of remote control locking characteristics of electrical equipment based on lua script

ActiveCN106647337BReduce configuration workReduce configuration workloadSimulator controlRemote controlElectrical devices

The invention relates to an electrical equipment remote control locking characteristic simulation method based on LUA scripts. An operator triggers a remote control simulation operation of the electrical equipment on a system HMI interface. A system real-time library detects a remote control simulation event and submits the event to a data engine at the bottom layer of the real-time library. The data engine then submits the remote control point information to an LUA script engine. The LUA script engine retrieves the LUA script rule of the remote control point in a rule base and finds out a signal point that the electrical equipment is required to be associated with in a configured association point XML input file. The LUA script engine obtains the real-time value of the relevant signal points from the real-time library through the data engine and calculates the logical result of the rule according to the rule. If the result is 1, the remote control characteristic of the electrical equipment is satisfied and the remote control is performed normally. Otherwise, it does not meet the remote control characteristics of the electrical equipment, the current remote control is rejected. The result whether to meet the remote control locking characteristic is written in the real-time library by the data engine, and is ultimately fed to the system HMI interface.

Owner:南京国电南自轨道交通工程有限公司

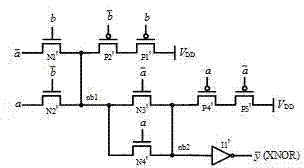

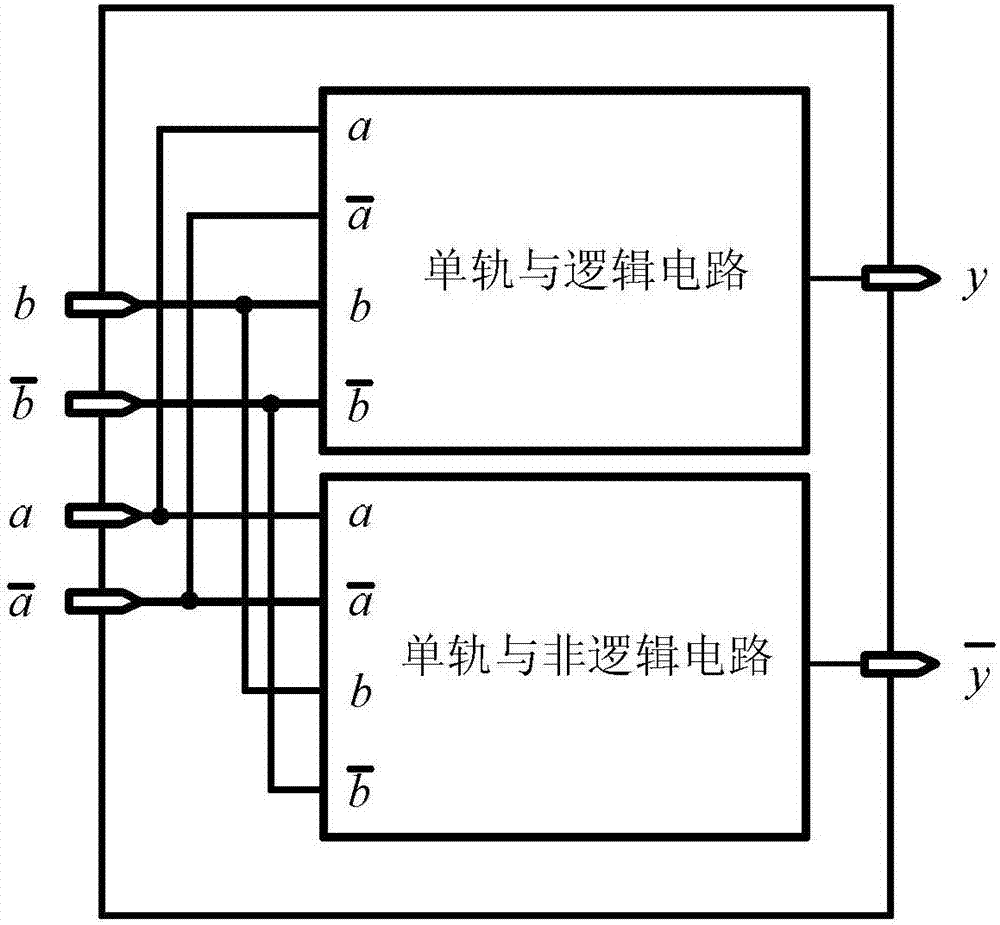

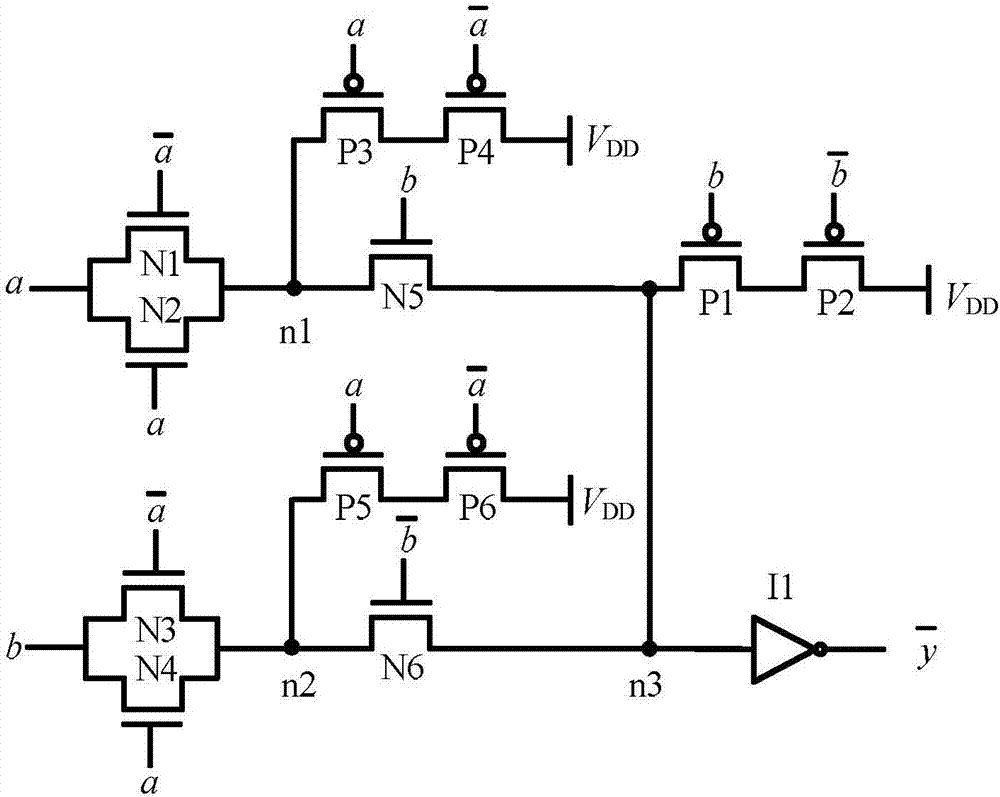

Dual-Rail Precharge Logic Cell Architecture

ActiveCN104378103BGood symmetryReduce in quantityLogic circuits characterised by logic functionEffective solutionLogic cell

The double-track precharge logic unit structure belongs to the field of circuit electronics. The invention aims to effectively solve the problem of early propagation effect under the condition of small area expenditure. The AND-NAND logic of the present invention comprises a monorail and logic circuit and a monorail and non-logic circuit; both circuits have four input terminals, respectively connected to four input signals a, b and the output signal y of the monorail and logic circuit as input signals The AND logic result of a and b; the output signal of the single-rail NOR logic circuit is the NAND logic result of the input signals a and b; OR-OR logic includes a single-rail OR logic circuit and a single-rail NOR logic circuit; both circuits have Four input terminals are respectively connected to four input signals a, b and the output signal y of the single-rail OR logic circuit is the OR logic result of the input signals a and b; the output signal of the single-rail OR non-logic circuit is the OR of the input signals a and b illogical result.

Owner:山东天聚汇能微电子有限公司