TCP (transmission control protocol) stream based verification method

A verification method and logic verification technology, applied in the field of integrated circuit verification, can solve problems such as inflexible writing of testbench, and achieve the effect of shortening development time and improving design quality

- Summary

- Abstract

- Description

- Claims

- Application Information

AI Technical Summary

Problems solved by technology

Method used

Image

Examples

Embodiment Construction

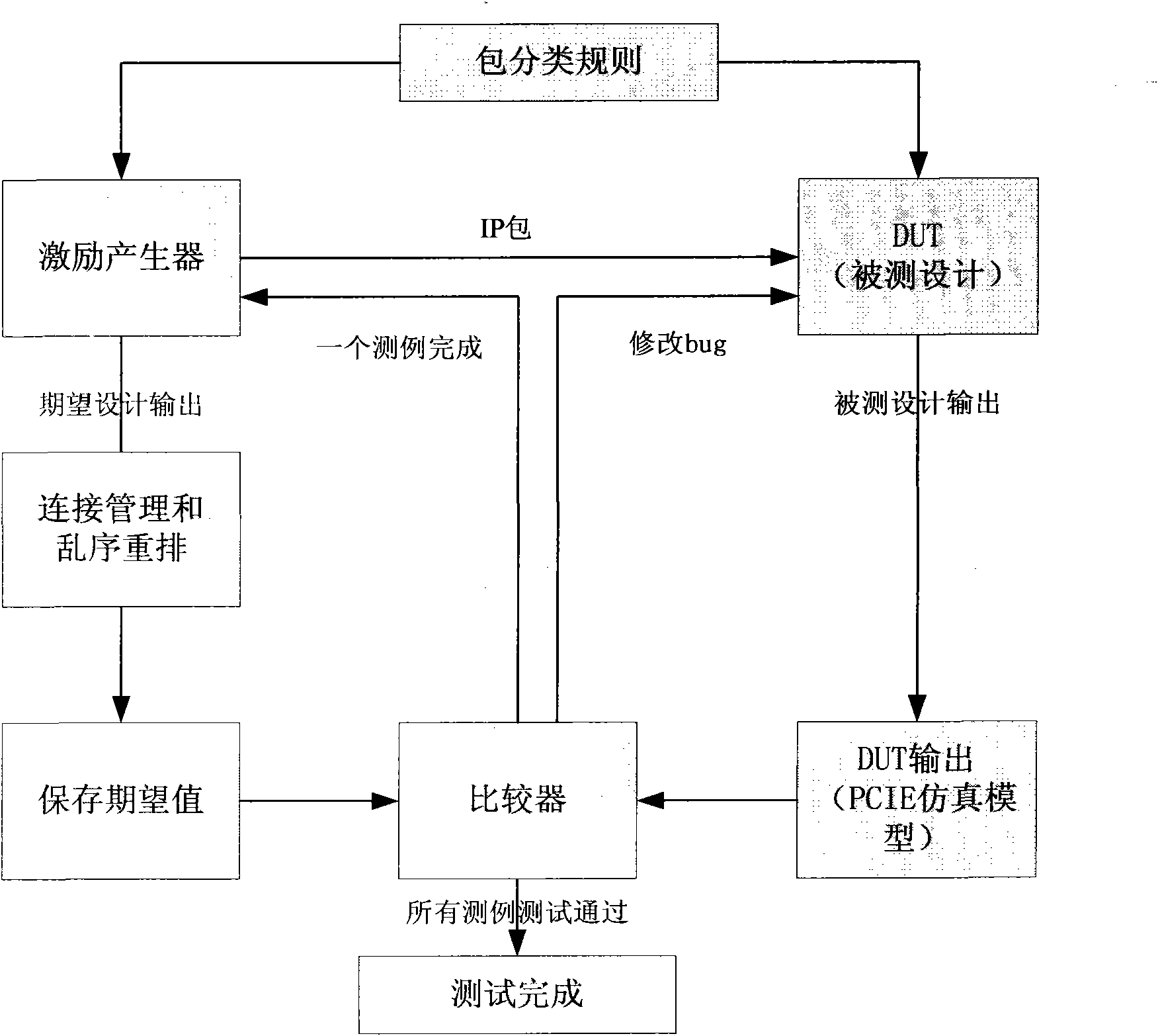

[0013] The technical solution uses systemVerilog language to establish a logic verification platform, including an incentive generator, stream management and stream sorting implementation, and an automatic comparator.

[0014] (1) Generate incentives

[0015] The exciter continuously generates a constrained random network packet structure based on TCP connections, including various abnormal connection situations, and drives logic work.

[0016] (2) Connection management and out-of-order rearrangement

[0017] The connection management module records the connection status, the rearrangement module performs random rearrangement according to the results of the management module, and the automatic comparator saves the results to the desired buffer;

[0018] (3) PCIE simulation model receives logic output results

[0019] PCIE receives the logical output result and saves it in the output result buffer. At the same time, it imitates the behavior of the host, sends commands to eac...

PUM

Login to View More

Login to View More Abstract

Description

Claims

Application Information

Login to View More

Login to View More