Address mappings method and operand parallel FFT processing system

An address mapping and processing system technology, applied in the field of FFT processing, can solve the problem that the processor cannot access operands in parallel

- Summary

- Abstract

- Description

- Claims

- Application Information

AI Technical Summary

Problems solved by technology

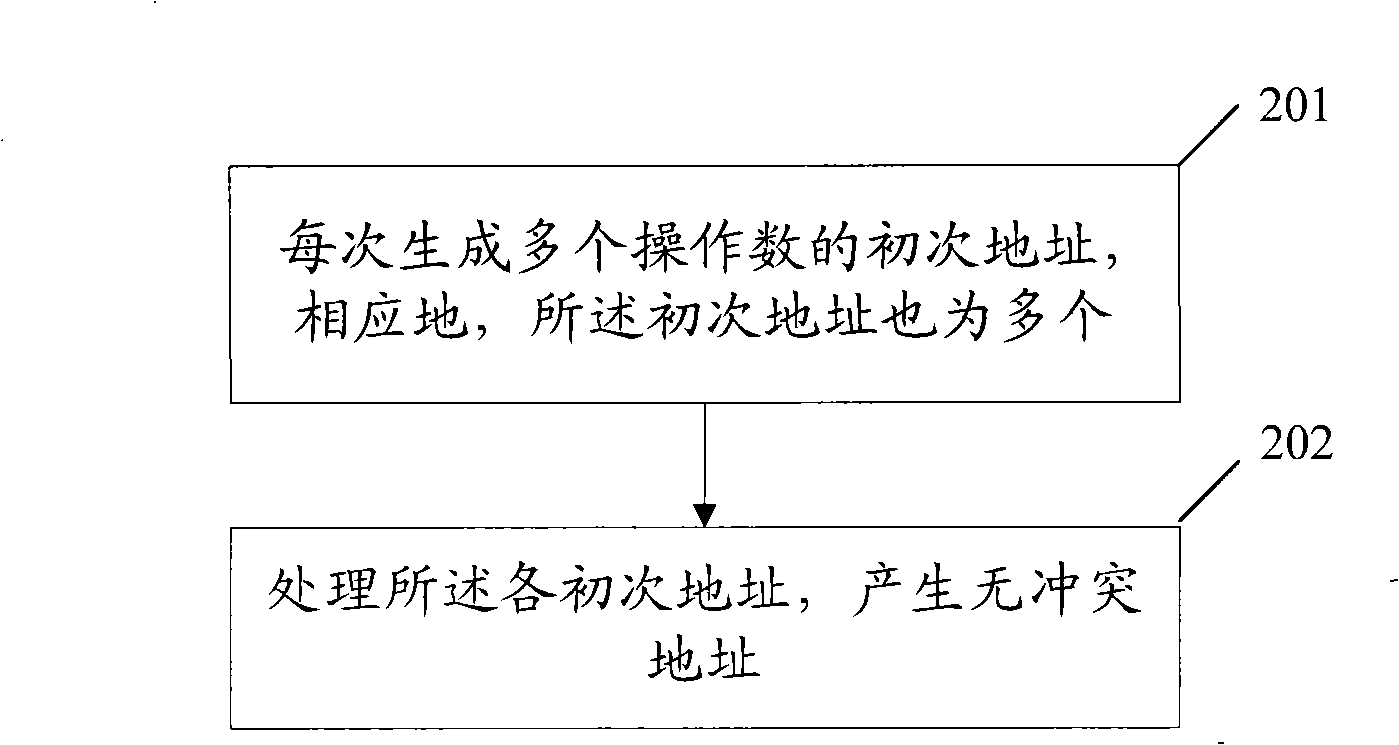

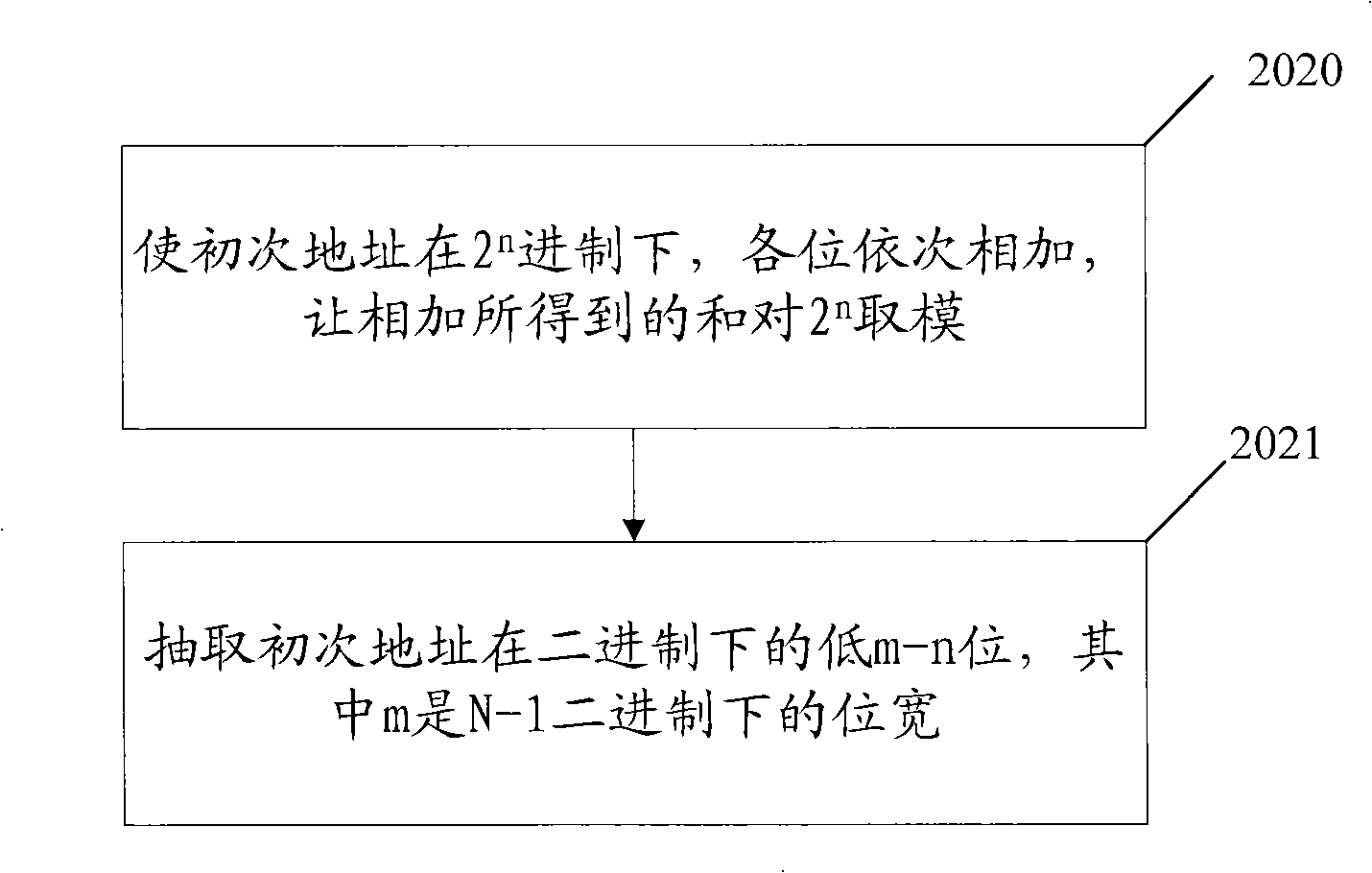

Method used

Image

Examples

example 1

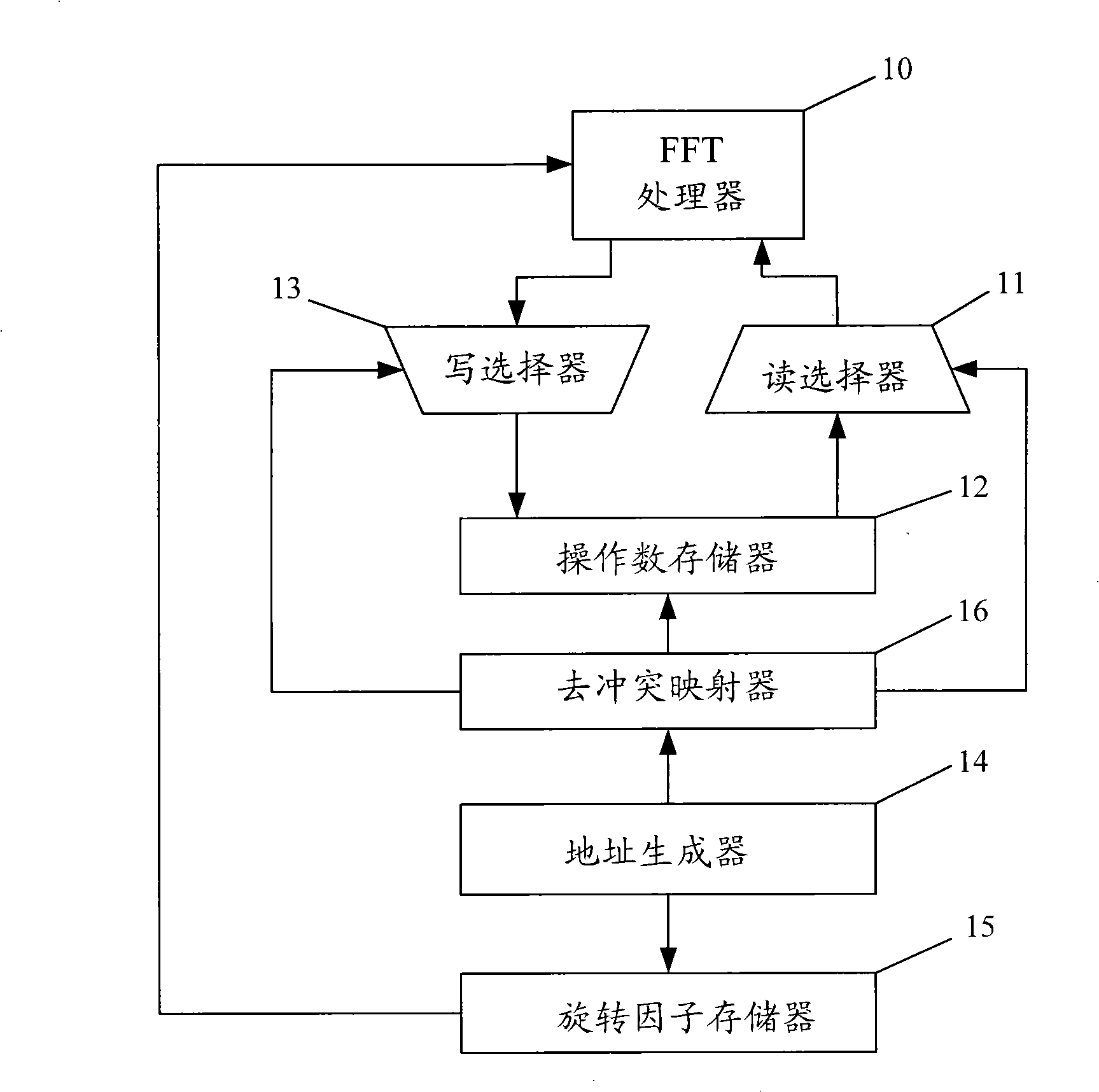

[0064] In this example, the base-4 butterfly operation is used for illustration, taking 64 points as an example.

[0065] FIG. 3 is a schematic structural diagram of an FFT processing system with parallel operands of radix-4 butterfly operation. As shown in the figure, the operand memory 12 is composed of 4 memory banks of 0# memory bank 120, 1# memory bank 121, 2# memory bank 122 and 3# memory bank 123, so the slice address is at least two bits. Each storage bank has 16 storage spaces, correspondingly, each storage bank has 16 internal addresses, so the internal address has at least four bits. Therefore, in this example, the transmission lines connecting the decollision mapper 16 to each memory bank must be able to transmit at least 6-bit addresses in parallel.

[0066] The read selector 11 and the write selector 13 are 4 to 4 selectors respectively, and their design methods are in the prior art, and will not be repeated here. The read selector 11 and the write selector 13 ...

example 2

[0089] In this example, the radix-8 butterfly operation is used for illustration, taking 512 points as an example.

[0090] In this example, the first memory 12 includes 8 memory banks; both the read selector and the write selector are 8 to 8 selectors.

[0091] According to the existing address mapping method, in the 512-point radix-8 butterfly operation, the initial address is up to 9 bits, so the transmission line from the address generator 14 to the decollision mapper 16 can transmit at least 9 bits of address.

[0092] 512-point radix-8 butterfly operation, the operand memory 12 includes 8 memory banks, so the chip select address has at least 3 bits. The maximum internal address is 63, so the internal address must be at least 6 bits. Therefore, in this example, the transmission line connecting the decollision mapper 16 to each memory bank needs to be able to transmit at least 9-bit addresses.

[0093] Only the main differences between this example and Example 1 will be ...

example 3

[0125] This example is a mixed operation of radix 4 and radix 2 with 2048 points. The butterfly operation of 2048 points requires 1-level base 2 calculation and 5-level base 4 calculation; in actual processing, 5-level base 4 calculation can be performed after base 2 calculation; it can also be performed after 5-level base 4 calculation , and then do the base 2 operation.

[0126] In this example, the radix-2 operation is performed first as an example, but it does not show that the present invention is limited to this only. Those skilled in the art can easily transform it into performing 5-level radix-4 operations first, and then performing 1-level radix-2 operations.

[0127] In this example, Figure 3 is still taken as an example for illustration. The initial address of 2048 points is up to 11 bits. Compared with example 1, the difference of the FFT processing system with parallel operands mainly lies in that the transmission line connecting the address generator 14 and the ...

PUM

Login to View More

Login to View More Abstract

Description

Claims

Application Information

Login to View More

Login to View More