Method of realizing parallel structure for FFT processor based on FPGA

A processor and multiplier technology, applied in the field of FFT implementation, can solve problems such as insufficient flexibility, and achieve the effect of improving processing speed and system throughput

- Summary

- Abstract

- Description

- Claims

- Application Information

AI Technical Summary

Problems solved by technology

Method used

Image

Examples

Embodiment Construction

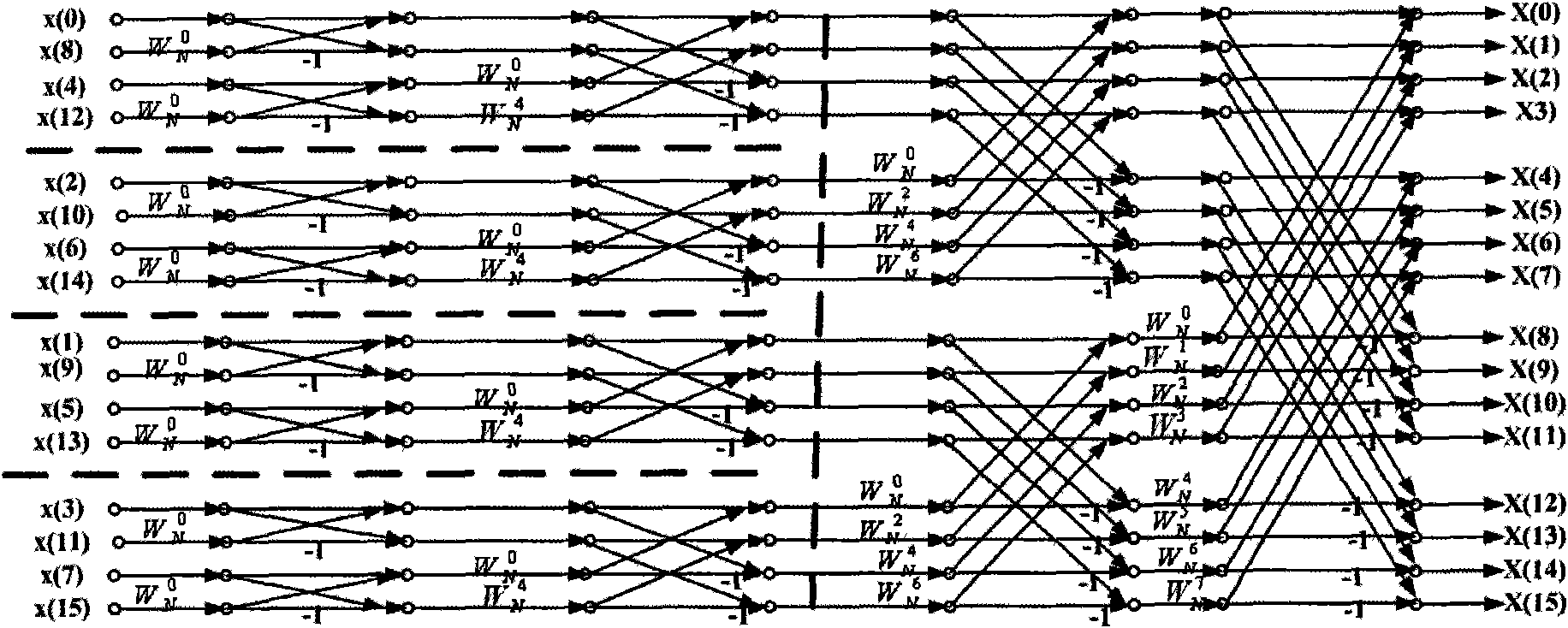

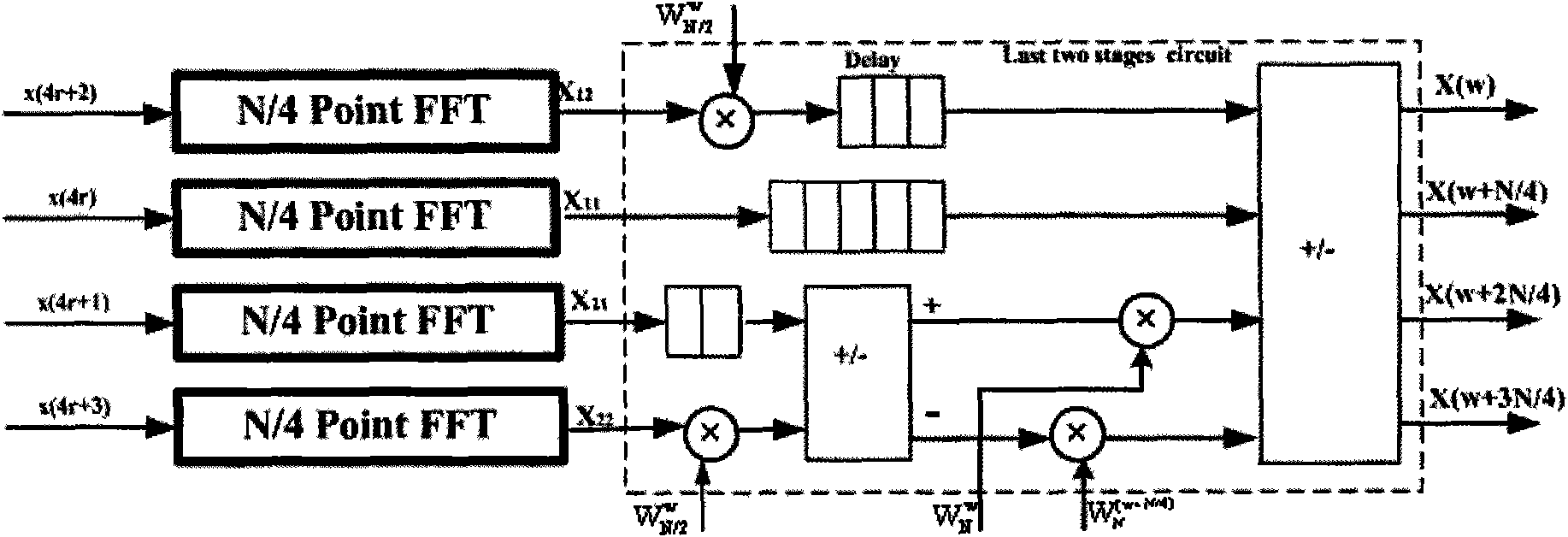

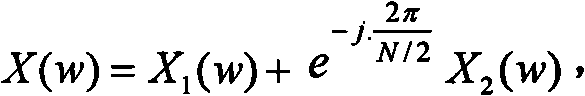

[0012] The present invention theoretically analyzes and designs a parallel FFT processor structure based on FPGA—splits long sequences into shorter sequences, and realizes the FFT of short sequences in parallel by multiple FFT units, and finally uses a specific structure inside FPGA The calculation circuit of each unit is used to process the calculation results of each unit, so as to obtain the final result.

[0013] The method of implementing parallel structure FFT processor based on FPGA is used to perform N (N is the k power of 2, or less than the k power, and the sequence is filled with 0 to make N become the k power of 2, k is a positive integer) points The FFT operation, described FPGA comprises a plurality of dedicated multipliers, a plurality of a large number of block RAMs, and a plurality of logic gates, comprising the following steps:

[0014] (1) Dividing the N points into M segments equally, each segment having N / M points;

[0015] (2) the FFT operation of the N ...

PUM

Login to View More

Login to View More Abstract

Description

Claims

Application Information

Login to View More

Login to View More