Multi-processor circuit with shared memory banks

A multi-processor, memory bank technology, applied in memory systems, electrical digital data processing, instruments, etc., can solve problems such as complex memory design

- Summary

- Abstract

- Description

- Claims

- Application Information

AI Technical Summary

Problems solved by technology

Method used

Image

Examples

Embodiment Construction

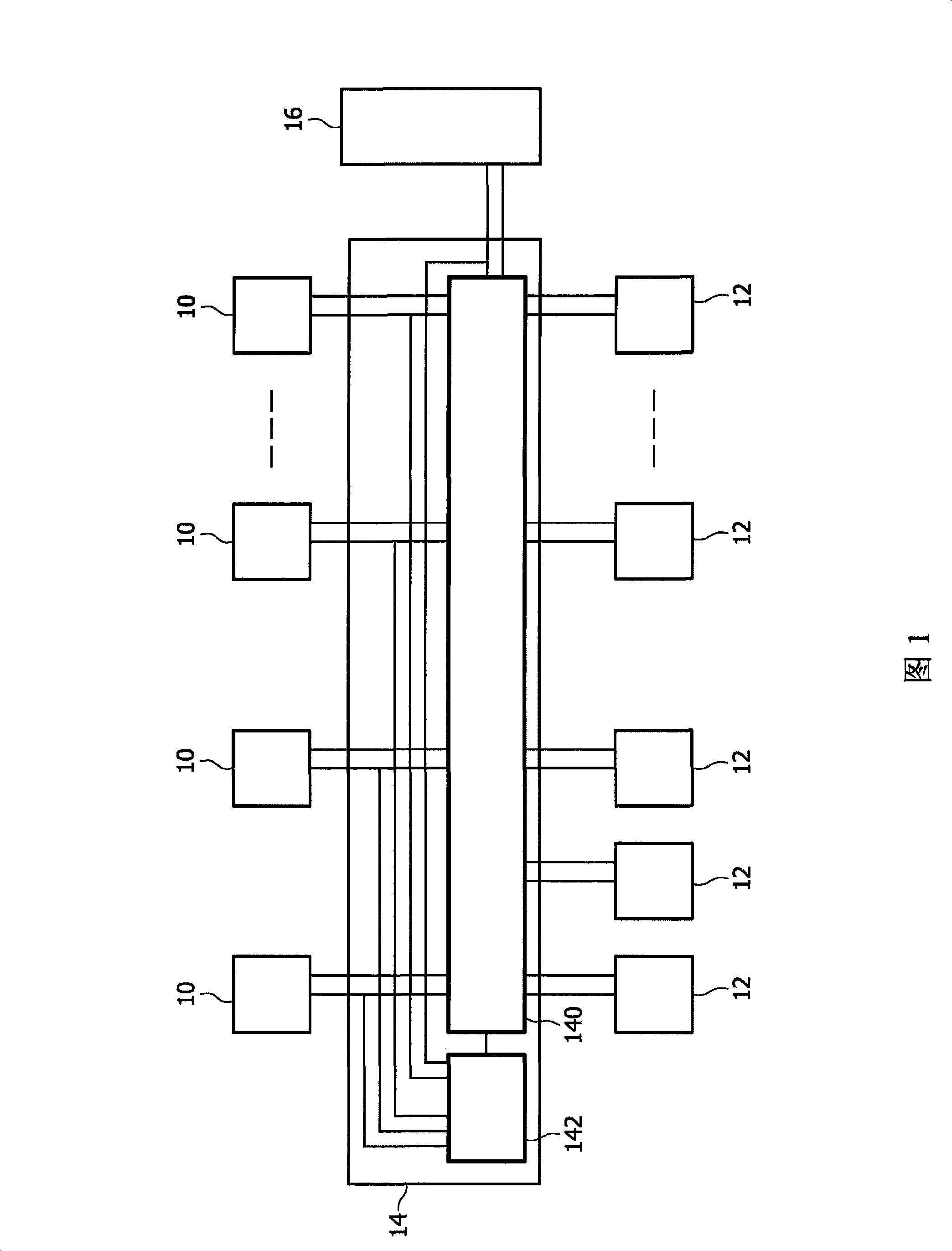

[0017] FIG. 1 shows a data processing circuit including a plurality of processors 10 , a plurality of memory banks 12 , connection circuits 14 and a disk defragmentation device 16 . The processor 10 and the disk defragmentation device 16 are coupled to the memory bank 12 through the connection circuit 14 . The connection circuit 14 includes a crossbar circuit 140 and an address arbiter 142 . The address output and data input / output of the processor 10 and the disk defragmentation device 16 are coupled to the crossbar circuit 140 . Address input and data input / output of memory bank 12 are coupled to crossbar circuit 140 . The address outputs of processor 10 and disk defragmentation device 16 are coupled to address arbiter 142, which has output terminals (only one shown) coupled to switch control inputs of crossbar circuit 140, and confirms processing input to device 10. Preferably, the disk defragmentation device 16 is coupled to the memory bank 12 as a processor similar to ...

PUM

Login to View More

Login to View More Abstract

Description

Claims

Application Information

Login to View More

Login to View More