Semiconductor packaging construction with weld crack restraint ring

A semiconductor and structural technology, applied in the field of high-density packaging stacking module architecture, can solve the problems of stress resistance becoming more sensitive, general products do not have suitable structure, open circuit, etc., to increase the welding fixing strength and high product durability. degree, and the effect of inhibiting the spread of cracks

- Summary

- Abstract

- Description

- Claims

- Application Information

AI Technical Summary

Problems solved by technology

Method used

Image

Examples

no. 1 Embodiment

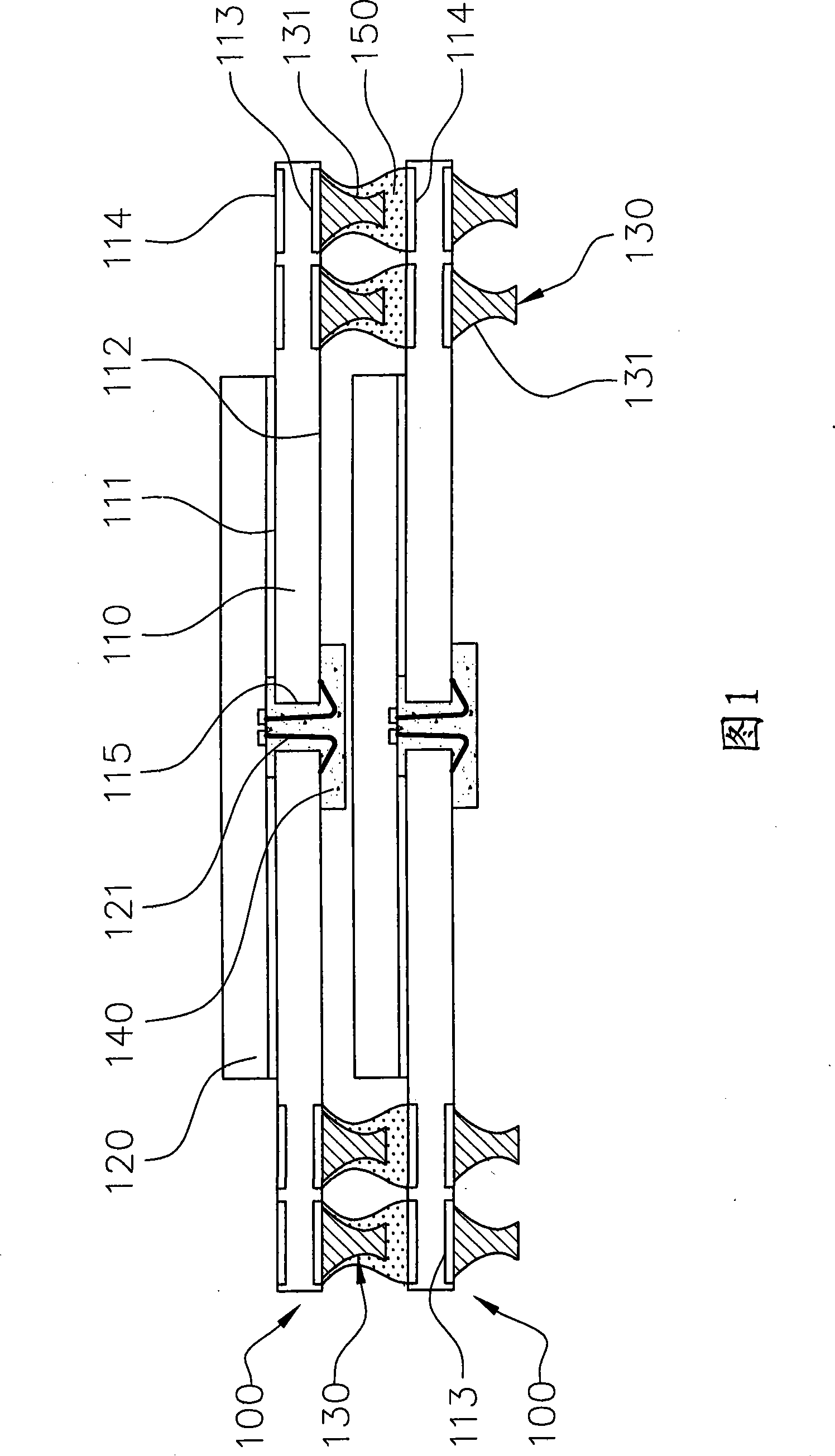

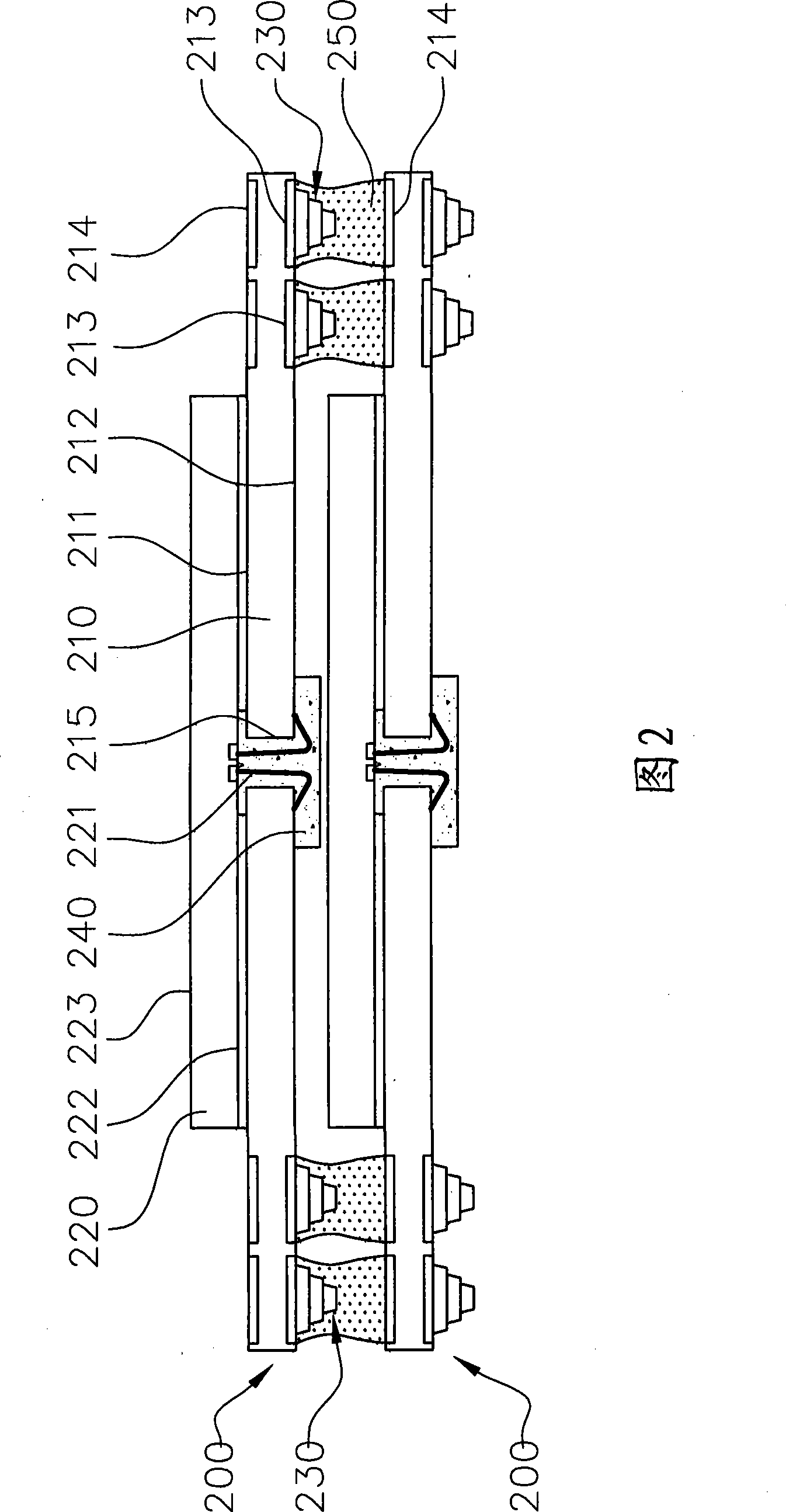

[0069] Please refer to FIG. 2 , which is a schematic cross-sectional view of stacked semiconductor package structures with solder crack suppression rings according to the first embodiment of the present invention. It is a stacking combination of two semiconductor package structures 200 , but without limitation, more semiconductor package structures 200 can be stacked on top, such as three, four or more. Each semiconductor package structure 200 mainly includes a chip carrier 210 , a chip 220 and a plurality of tower bumps 230 .

[0070] The chip carrier 210 mentioned above can be a multi-layer printed circuit board with a double-sided electrical conduction structure. The wafer carrier 210 has an upper surface 211 and a lower surface 212, wherein:

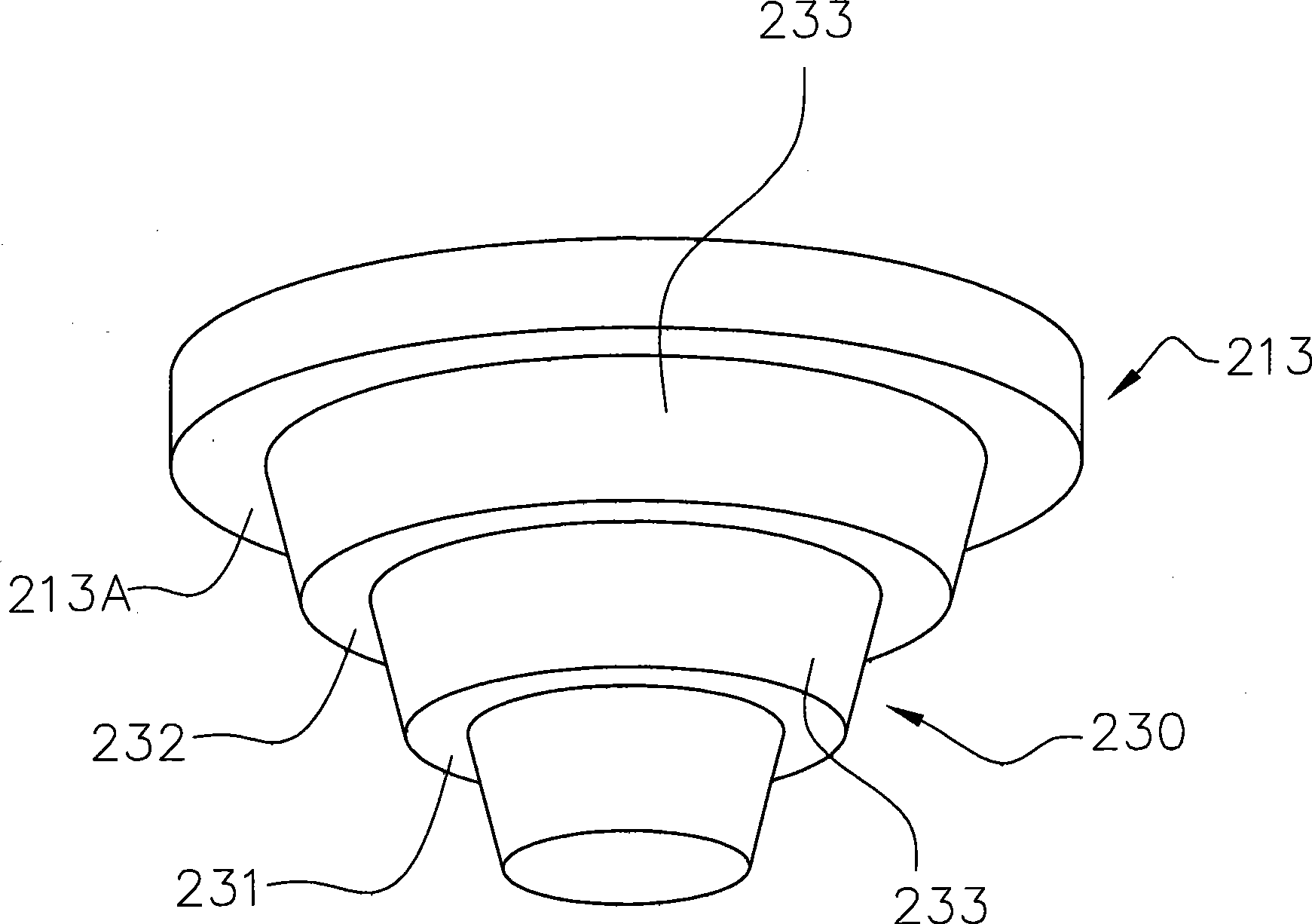

[0071] The lower surface 212 is provided with a plurality of first conductive pads 213 , which can be used as external pads of the chip carrier 210 . In this embodiment, the semiconductor package structure 200 is suitable for packa...

no. 2 Embodiment

[0086] see Figure 5 Shown is a schematic perspective view of another tower-shaped bump shape of the semiconductor package structure according to the second embodiment of the present invention. The other shape of the tower-shaped protrusion is to replace the tower-shaped protrusions 330 with another tower-shaped protrusion 330A with a change in shape. The tower-shaped protrusion 330A is composed of multi-segmented cones. There is a first crack suppression ring 331A and at least one second crack suppression ring 332A. Wherein, the first crack suppression ring 331A and the second crack suppression ring 332A are roughly parallel to the first conductive pads 313 to suppress the diffusion of welding cracks. The second crack suppression ring 332A is located between the first crack suppression ring 331A and the corresponding first contact pad 313 , and is parallel to but not coplanar with the first crack suppression ring 331A. In this embodiment, the inner diameter of the second cr...

PUM

Login to View More

Login to View More Abstract

Description

Claims

Application Information

Login to View More

Login to View More