Chip electro-static discharge test device

An electrostatic discharge test and chip technology, applied in the direction of measuring devices, measuring electricity, measuring electrical variables, etc., can solve the problems of ESD equipment without test board, long test board cycle, high cost, etc., to achieve short cycle, low production cost, cost reduction effect

- Summary

- Abstract

- Description

- Claims

- Application Information

AI Technical Summary

Problems solved by technology

Method used

Image

Examples

Embodiment 1

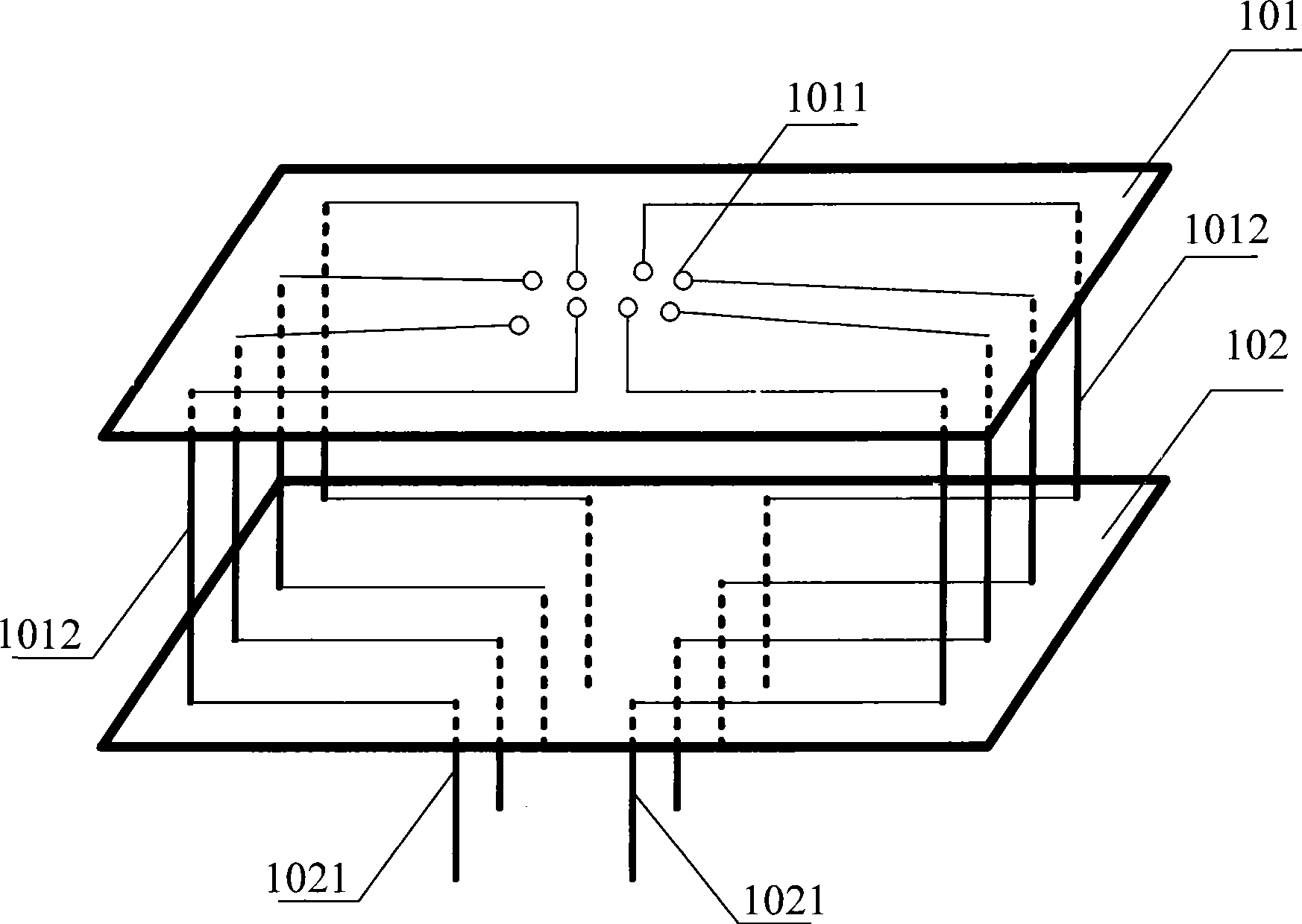

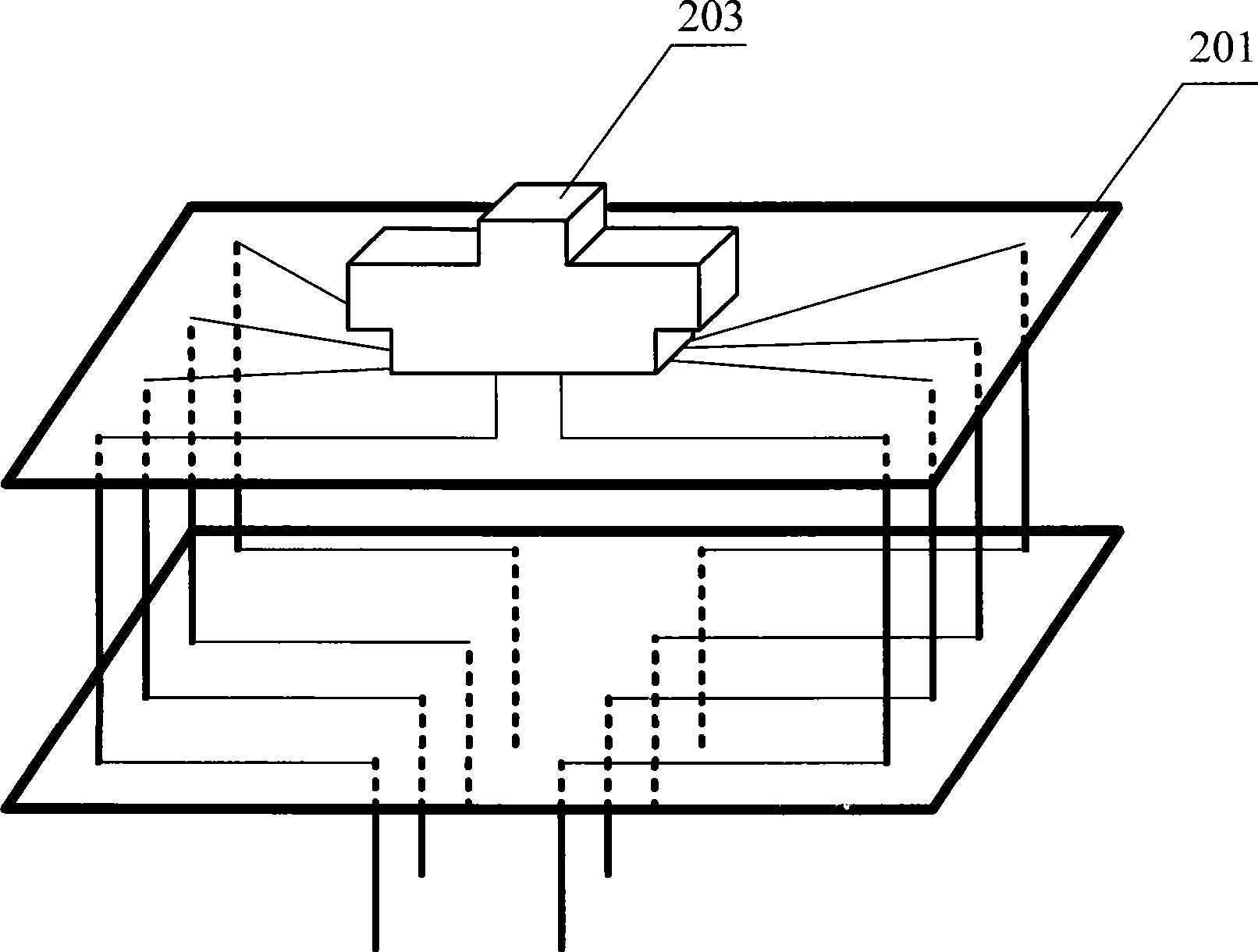

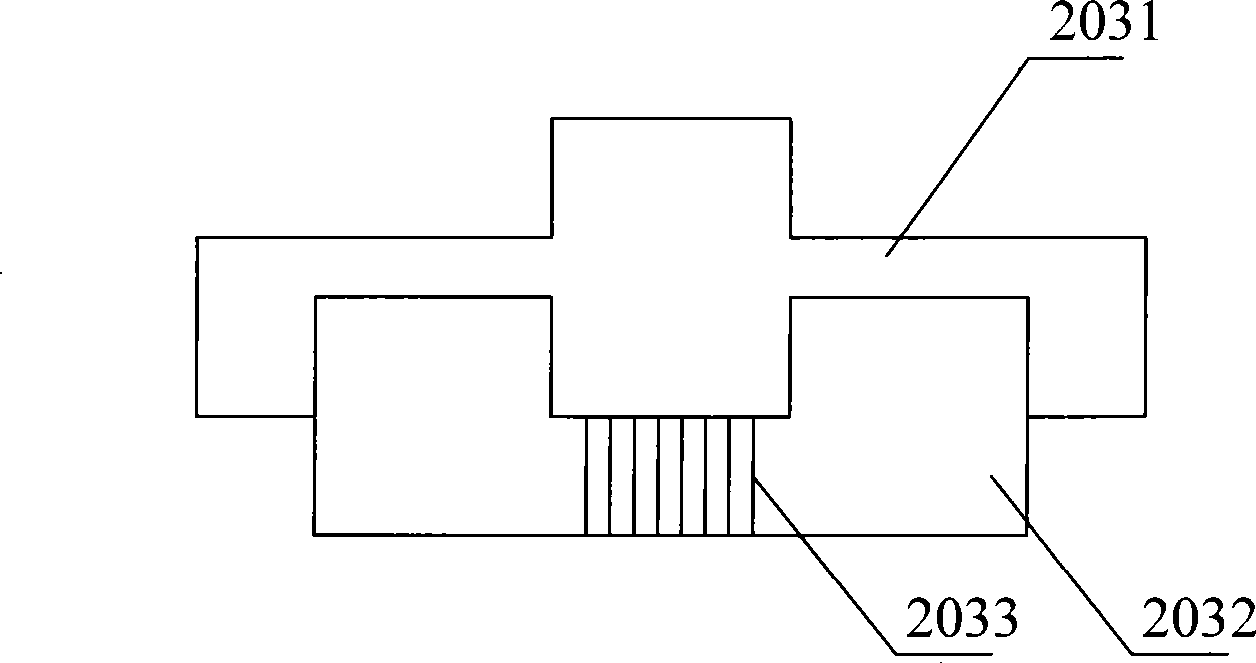

[0027] refer to figure 1 , which shows Embodiment 1 of the chip ESD testing device of the present invention, which may specifically include:

[0028] Circuit board 101 and circuit board 102;

[0029] The upper surface of the circuit board 101 is provided with welding pads 1011 corresponding to the positions of the respective pins of the chip to be tested; the soldering pads 1011 are used for electrical connection with each pin of the chip to be tested during testing.

[0030] Both sides of the circuit board 101 are provided with pin headers 1012 that are electrically connected one-to-one with the solder pads 1011; wherein, the electrical connection between the solder pads 1011 and the pin headers 1012 is realized through the wiring on the circuit board 101, and the circuit board 101 may be a PCB (Print circuit board, printed circuit board) board.

[0031] The other end of the pin header 1012 is electrically connected to the circuit board 102, and the lower surface of the cir...

Embodiment 3

[0038] refer to Figure 4 , showing another chip ESD testing device embodiment 3, specifically may include:

[0039] A circuit board 401, the upper surface of the circuit board 401 is provided with a welding pad 4011 corresponding to each pin position of the chip to be tested; the welding pad 4011 is used for electrical connection with each pin of the chip to be tested during testing;

[0040] The lower surface of the circuit board 401 is provided with a pin header 4012 corresponding to a chip-on-board (COB, Chip on Board) test board; the welding pad 4011 is electrically connected to the pin header 4012 one-to-one. The circuit board 401 may be a PCB board. Among them, the COB test board can be used for ESD testing on chips with 256 pins at most.

[0041]When testing, the chip to be tested is directly welded on the circuit board 401 , so that each pin of the chip is electrically connected to the pad 4011 .

[0042] The device can also have the following purposes: when ESD fa...

PUM

| Property | Measurement | Unit |

|---|---|---|

| Resistance | aaaaa | aaaaa |

Abstract

Description

Claims

Application Information

Login to View More

Login to View More - Generate Ideas

- Intellectual Property

- Life Sciences

- Materials

- Tech Scout

- Unparalleled Data Quality

- Higher Quality Content

- 60% Fewer Hallucinations

Browse by: Latest US Patents, China's latest patents, Technical Efficacy Thesaurus, Application Domain, Technology Topic, Popular Technical Reports.

© 2025 PatSnap. All rights reserved.Legal|Privacy policy|Modern Slavery Act Transparency Statement|Sitemap|About US| Contact US: help@patsnap.com