Technique allowance-increasing contact hole layer layout method

A technology of process margin and contact hole, which is applied in special data processing applications, instruments, electrical digital data processing, etc., can solve the problems of reducing the photolithographic quality of the contact hole layer, reducing the process margin of the contact hole layer, and increasing the difficulty of the process, etc. , to achieve the effect of improving the process margin, increasing the process margin, and increasing the process window

- Summary

- Abstract

- Description

- Claims

- Application Information

AI Technical Summary

Problems solved by technology

Method used

Image

Examples

Embodiment Construction

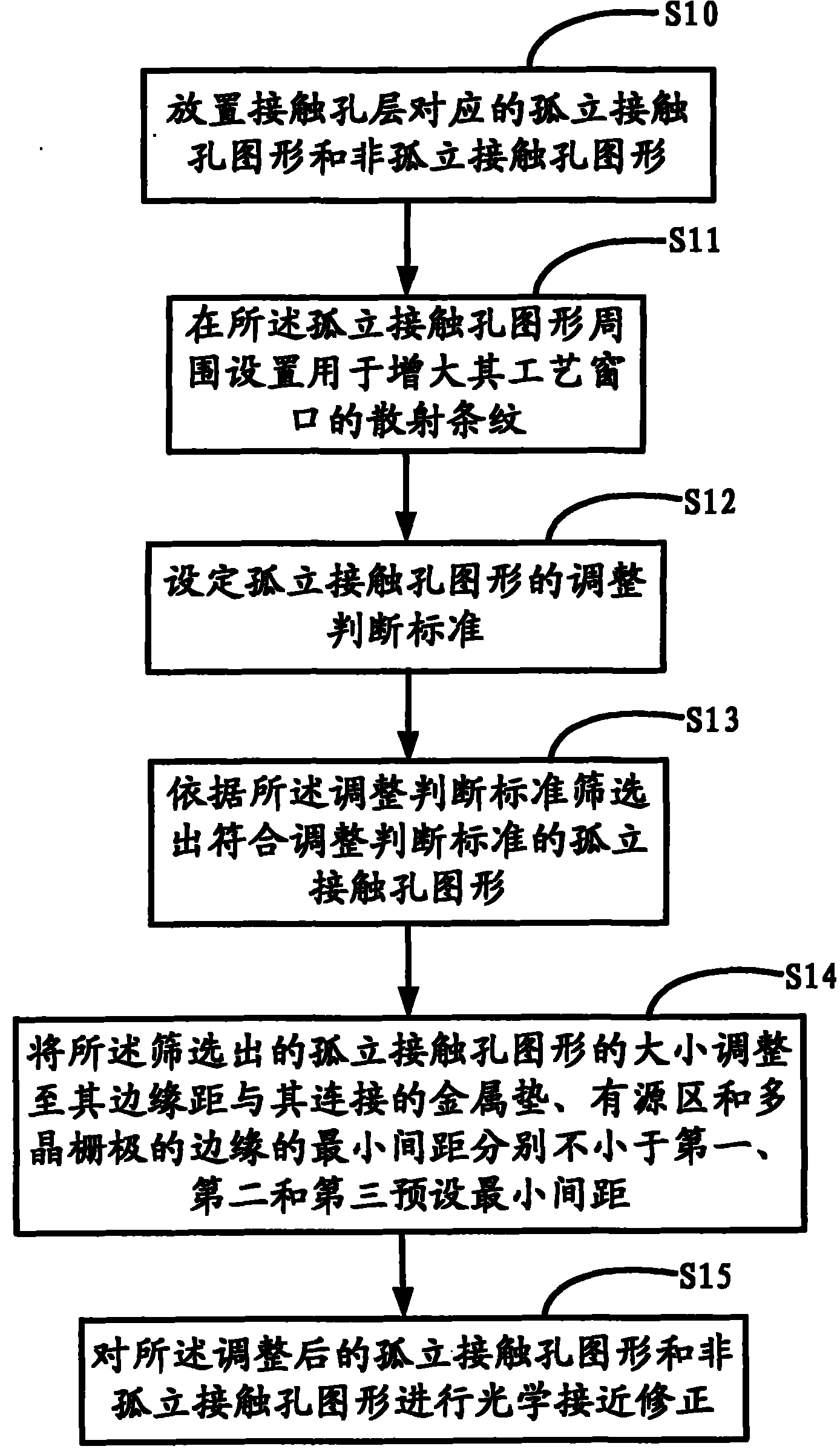

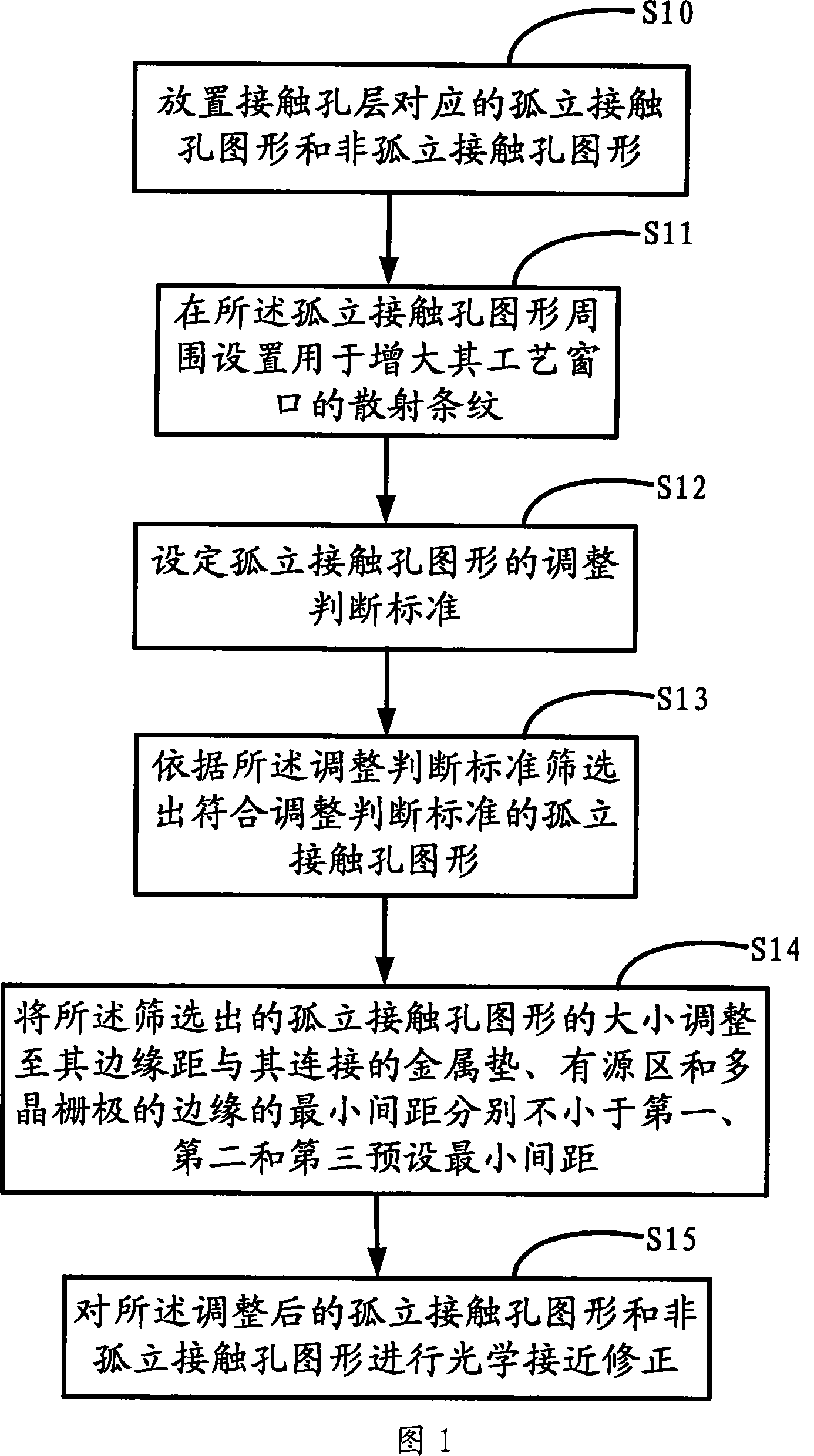

[0020] The contact hole layer patterning method that can increase the process margin of the present invention will be further described in detail below.

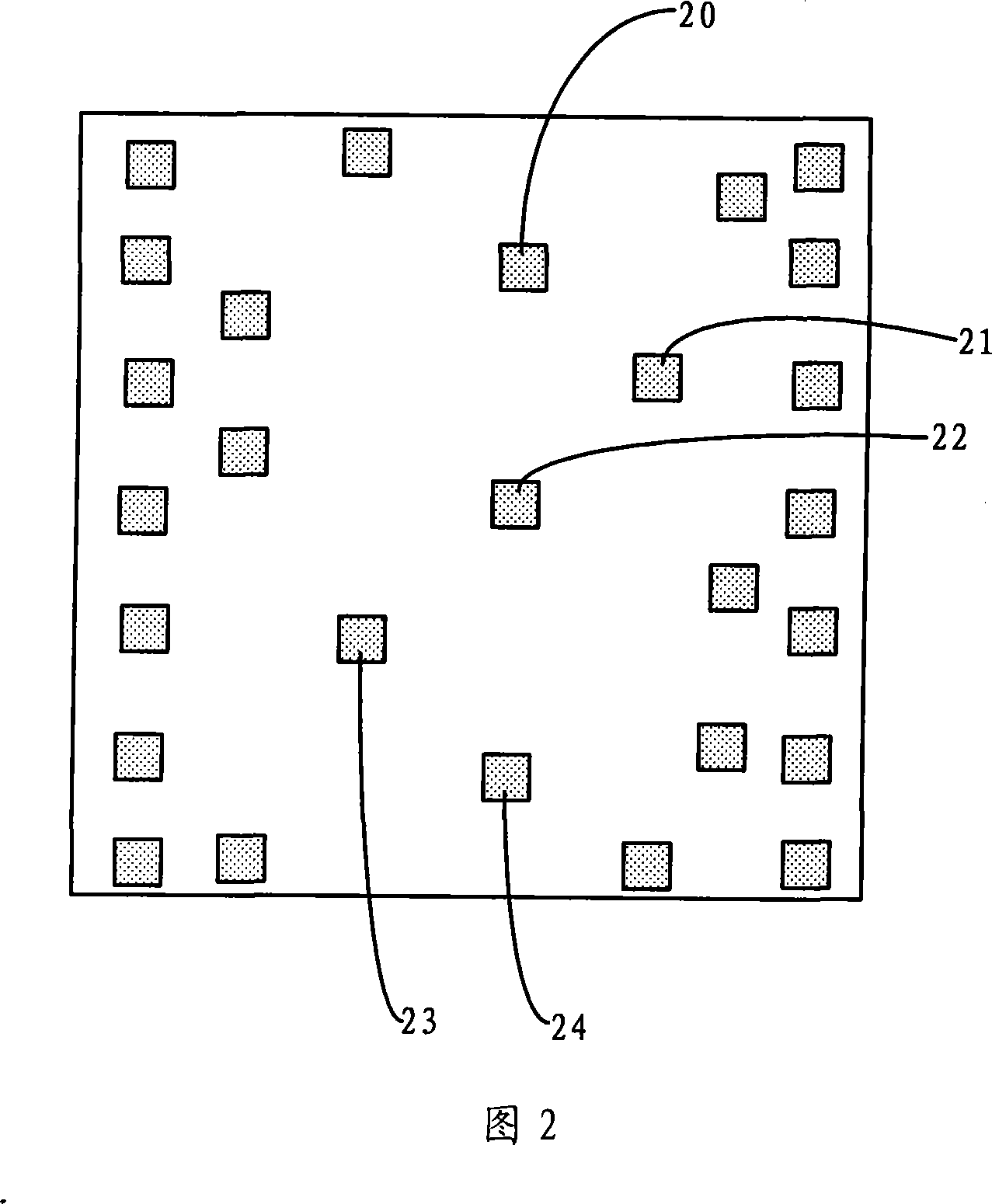

[0021] The contact hole layer layout method that can increase the process margin of the present invention is used for the layout layout of the contact hole layer by the user using the layout layout software. The contact hole layer has a plurality of metal pads, active An isolated contact hole and a non-isolated contact hole connecting the region and the polysilicon gate, the edge of the isolated contact hole is at least the first, the second and the second distance from the edge of the metal pad connected thereto, the active region and the polysilicon gate Three preset minimum spacing. In this embodiment, the layout software is L-Edit or Cadence layout software, the first, second and third preset minimum spacings are 50, 40 and 40 nanometers respectively, and the isolated contact Both the hole and the non-isolated contact h...

PUM

Login to View More

Login to View More Abstract

Description

Claims

Application Information

Login to View More

Login to View More