Hardware architecture for decoding FEC of DMB-T demodulation chip and decoding method

A forward error correction decoding and DMB-T technology, which is applied in the field of digital TV terrestrial broadcasting transmission system, can solve the problems of high design complexity and high hardware cost, and achieve the goal of increasing the number of iterations, reducing design costs, and reducing control logic Effect

- Summary

- Abstract

- Description

- Claims

- Application Information

AI Technical Summary

Problems solved by technology

Method used

Image

Examples

Embodiment Construction

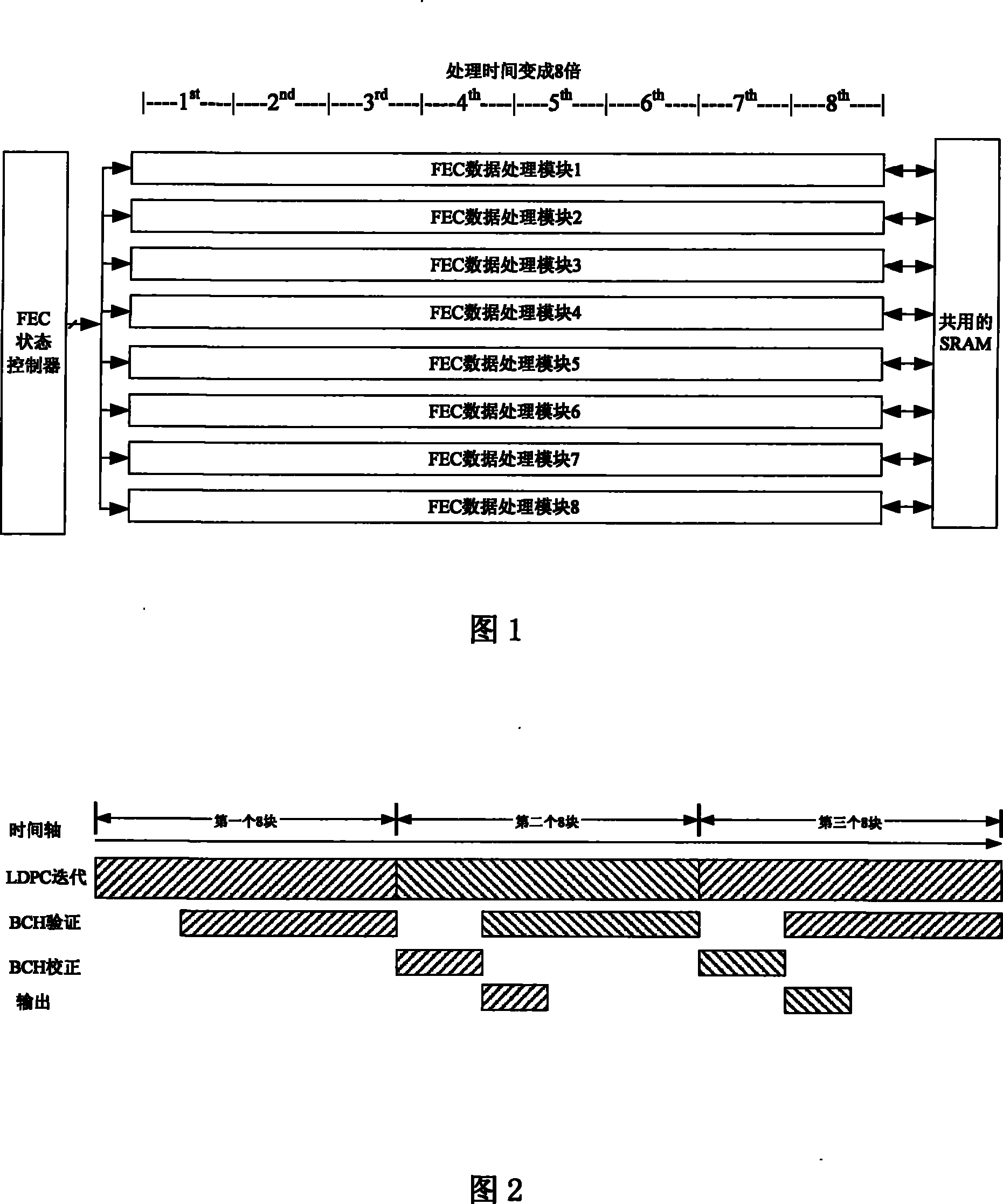

[0034] Since the error correction performance of FEC is proportional to the number of iterations of LDPC, the maximum number of iterations of LDPC that can be realized by the hardware structure determines the performance characteristics of the hardware structure. Under the performance requirements of DMB-T, the present invention selects SPA algorithm to perform LDPC iteration, and adopts the structure of 8 FEC data processing modules to process data in parallel. Because BCH verification and BCH correction are carried out in the process of LDPC iteration, LDPC The parallel structure of BCH determines the parallel structure of BCH.

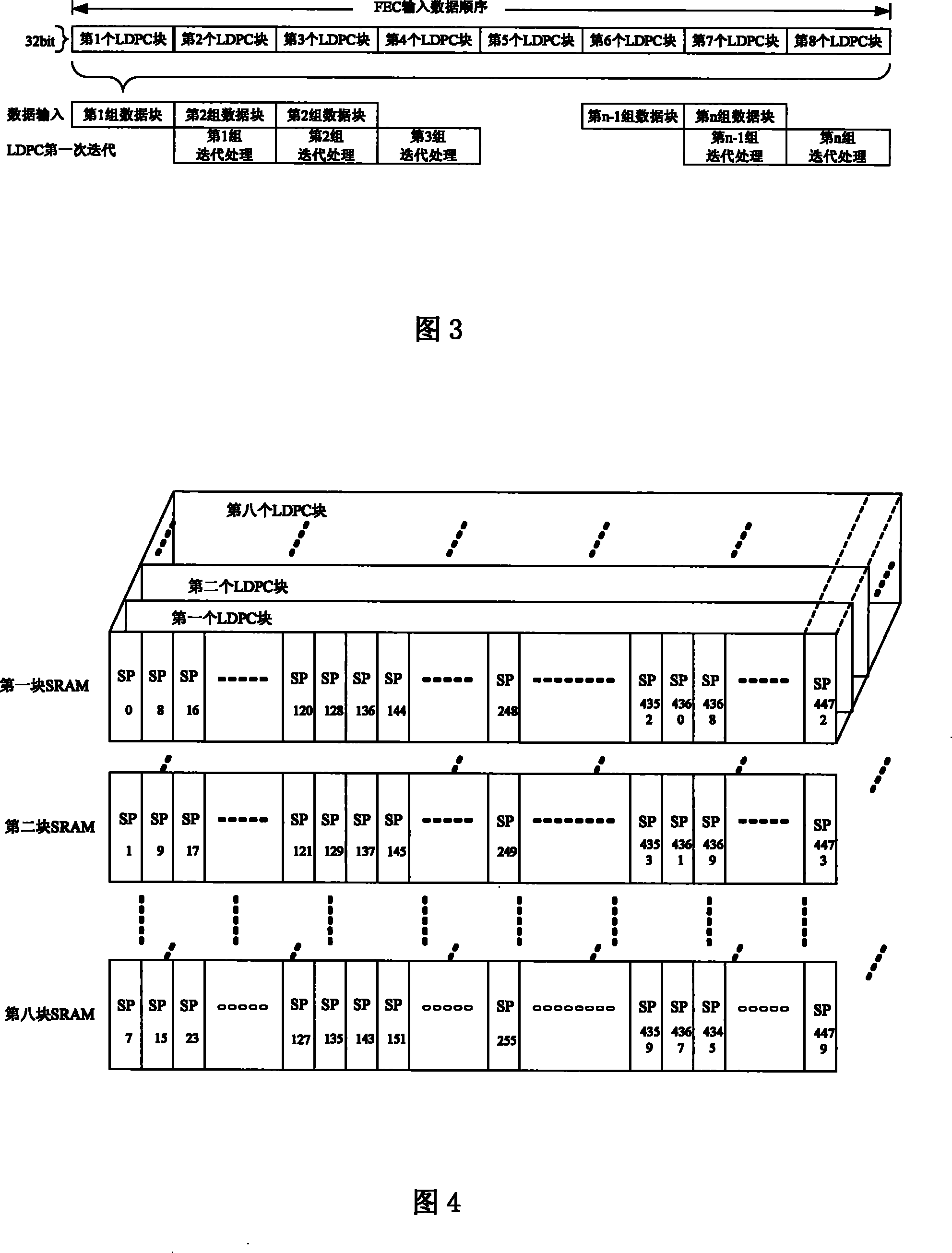

[0035] In order to save the LDPC iteration time occupied by BCH verification and BCH correction, in each FEC data processing module, a pipeline structure of LDPC iteration, BCH verification, BCH correction and forward error correction data output is used (see figure 2). Therefore, the entire time of the frame interval can be fully used for the LDP...

PUM

Login to View More

Login to View More Abstract

Description

Claims

Application Information

Login to View More

Login to View More - R&D

- Intellectual Property

- Life Sciences

- Materials

- Tech Scout

- Unparalleled Data Quality

- Higher Quality Content

- 60% Fewer Hallucinations

Browse by: Latest US Patents, China's latest patents, Technical Efficacy Thesaurus, Application Domain, Technology Topic, Popular Technical Reports.

© 2025 PatSnap. All rights reserved.Legal|Privacy policy|Modern Slavery Act Transparency Statement|Sitemap|About US| Contact US: help@patsnap.com