Method, system and apparatus for fault detection of tested device

A fault detection and tested technology, applied in the communication field, to achieve the effect of improving fault isolation rate, increasing bus speed, and facilitating maintenance

- Summary

- Abstract

- Description

- Claims

- Application Information

AI Technical Summary

Problems solved by technology

Method used

Image

Examples

Embodiment Construction

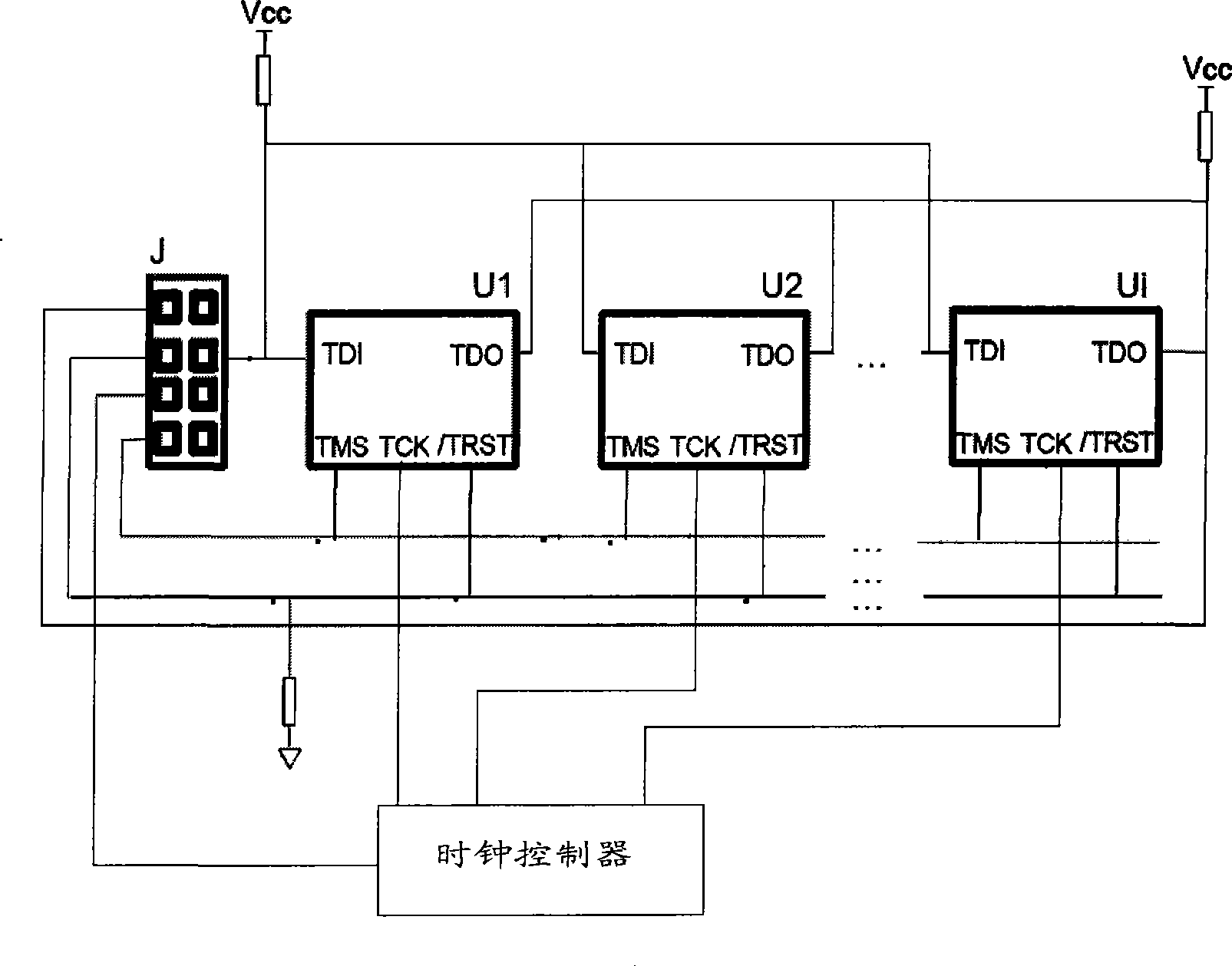

[0034] The embodiments of the present invention will be further described below in conjunction with the drawings and examples.

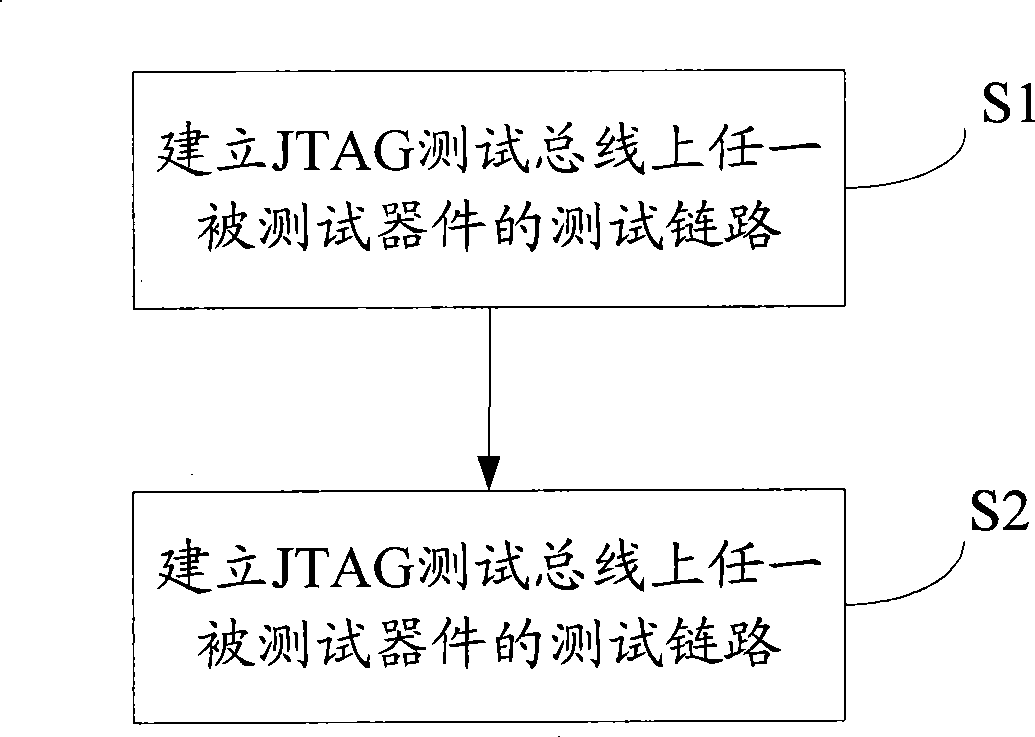

[0035] Embodiment 1 of the present invention provides a method for fault detection of a device under test, such as figure 2 shown, including:

[0036] S1, establishing a test link of any device under test on the JTAG test bus.

[0037] In S1: the JTAG controller controls the clock controller to gate the device under test, the JTAG controller and the clock controller, and the device under test establish a point-to-point drive simultaneously, and establish any device under test and JTAG test Bus test link, output clock. Wherein, the device under test is connected to the JTAG test bus in parallel. Wherein the clock controller performs timing analysis on the JTAG test bus through programmable logic analysis to accurately estimate the clock delay.

[0038] S2. Test the device under test, and if the data returned to the JTAG controller is abnormal or ...

PUM

Login to View More

Login to View More Abstract

Description

Claims

Application Information

Login to View More

Login to View More