Heterogeneous processors sharing a common cache

A heterogeneous processor, cache technology, applied in the field of processors

- Summary

- Abstract

- Description

- Claims

- Application Information

AI Technical Summary

Problems solved by technology

Method used

Image

Examples

Embodiment Construction

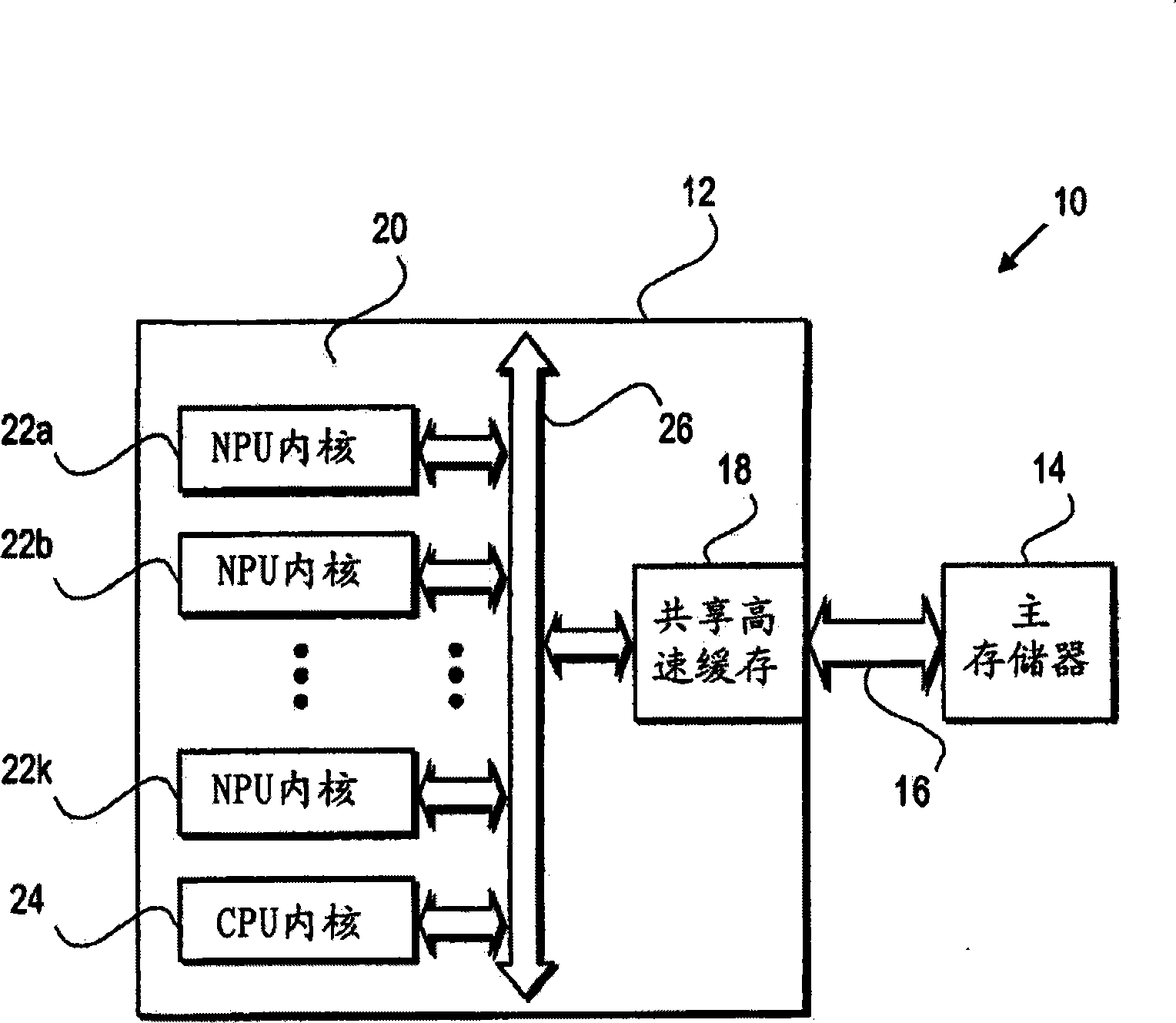

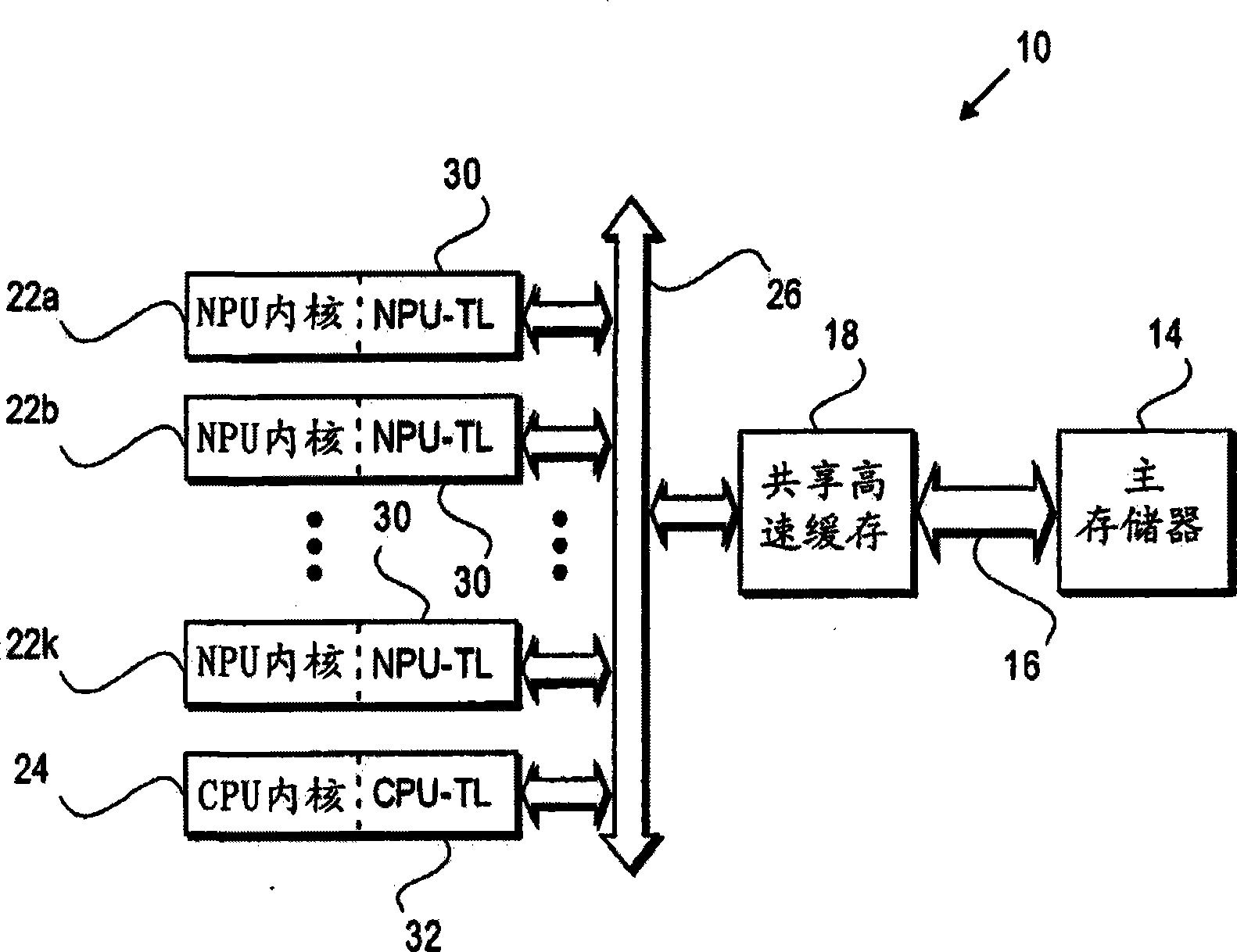

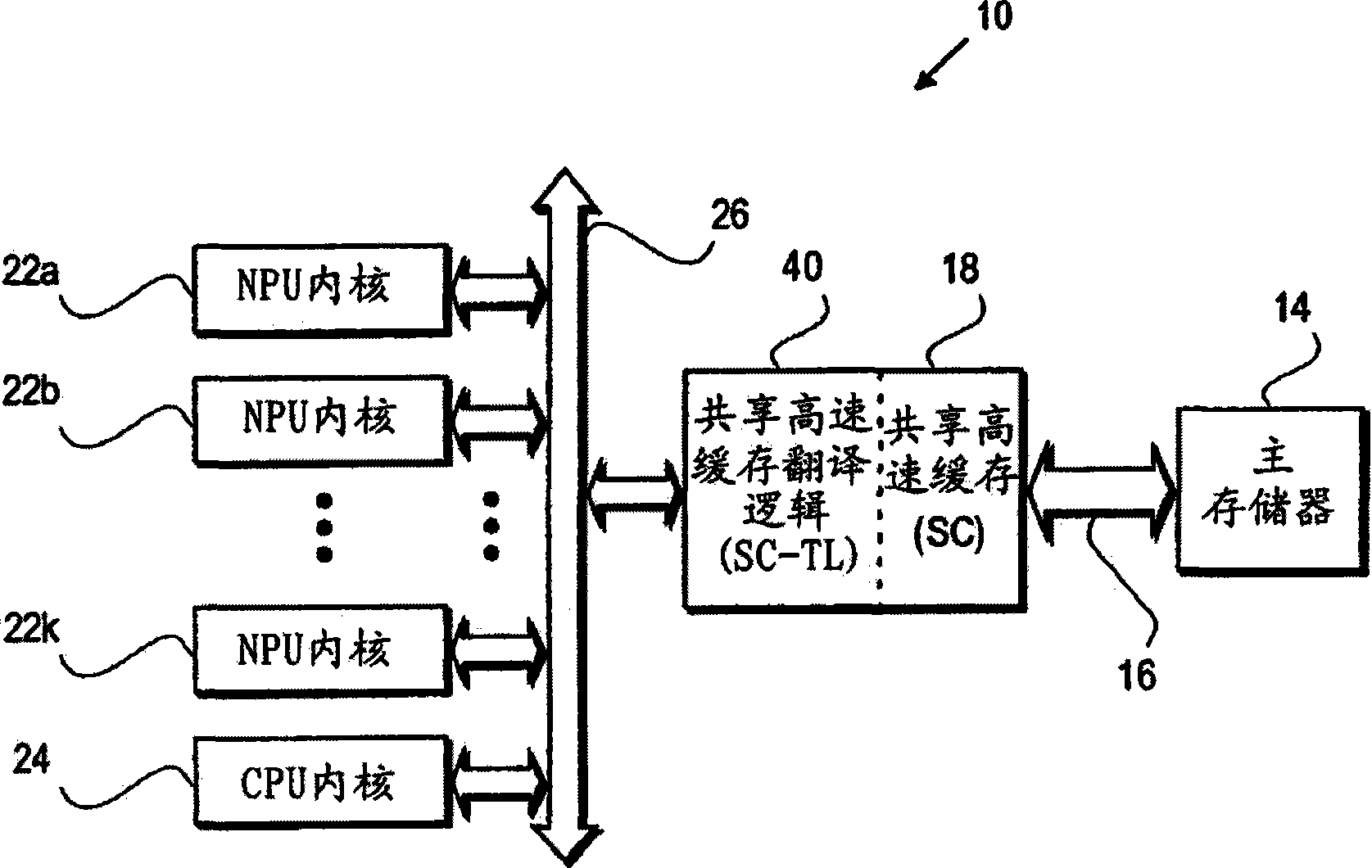

[0029] Figures 1A-1C A multiprocessor system 10 is shown including a multiprocessor 12 coupled to main memory 14 by a memory bus 16 . The multiprocessor 12 includes a cache (“shared cache”) 18 and a plurality of processor “cores” (collectively, processor cores 20 ) that are connected to and share the cache 18 . Shared cache 18 in this figure is intended to represent a unit comprising cache memory and associated control logic. Cache control logic includes logic for mapping memory addresses ("cache tags") that are currently cached with their associated cache lines.

[0030] The processor core 20 includes heterogeneous cores, that is, processor cores (or types of processor cores) with different structures. For example, processor core 20 may include one or more special purpose processor cores and / or at least one central processing unit (CPU) core.

[0031] Special purpose processor cores may include, for example, at least one network processor unit (NPU) core and / or a graphics ...

PUM

Login to View More

Login to View More Abstract

Description

Claims

Application Information

Login to View More

Login to View More - R&D Engineer

- R&D Manager

- IP Professional

- Industry Leading Data Capabilities

- Powerful AI technology

- Patent DNA Extraction

Browse by: Latest US Patents, China's latest patents, Technical Efficacy Thesaurus, Application Domain, Technology Topic, Popular Technical Reports.

© 2024 PatSnap. All rights reserved.Legal|Privacy policy|Modern Slavery Act Transparency Statement|Sitemap|About US| Contact US: help@patsnap.com