On-site programmable device FPGA logic unit model and general bin packing algorithm thereof

A technology of logic unit and box packing algorithm, which is applied in the direction of instruments, calculations, and special data processing applications, etc., and can solve problems such as too simple connections, too simple functions, and inapplicability

- Summary

- Abstract

- Description

- Claims

- Application Information

AI Technical Summary

Problems solved by technology

Method used

Image

Examples

Embodiment Construction

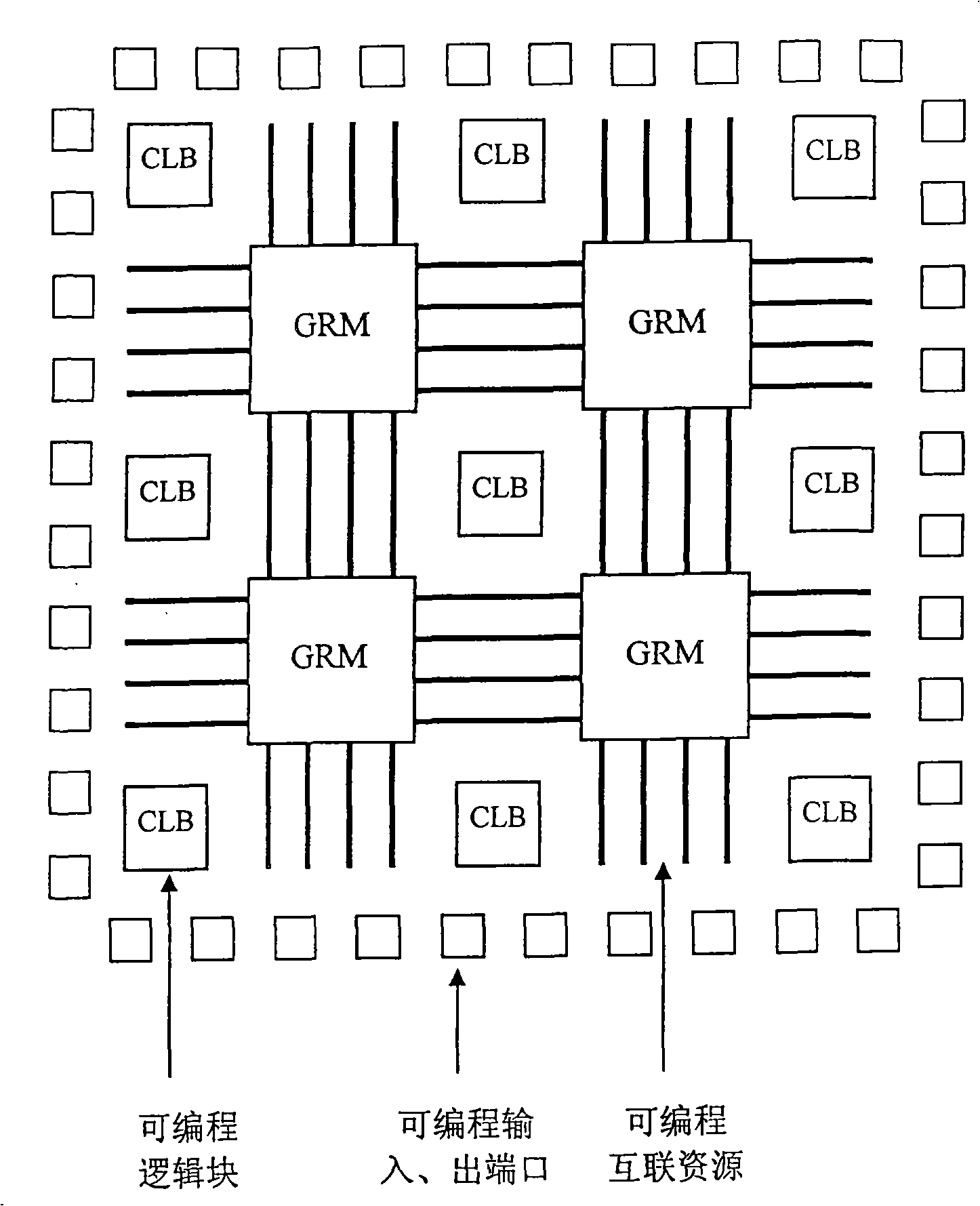

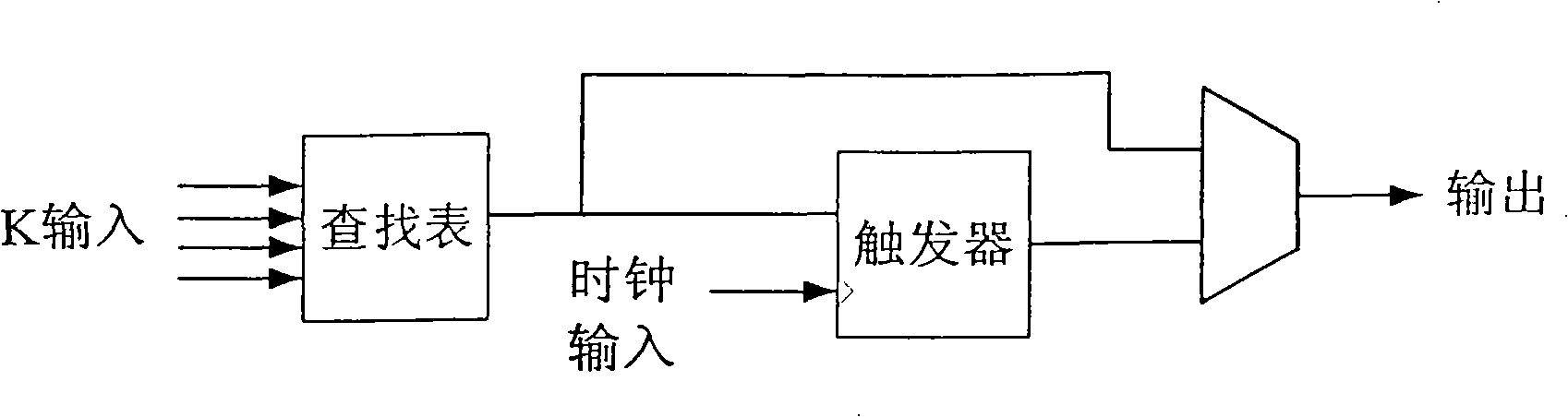

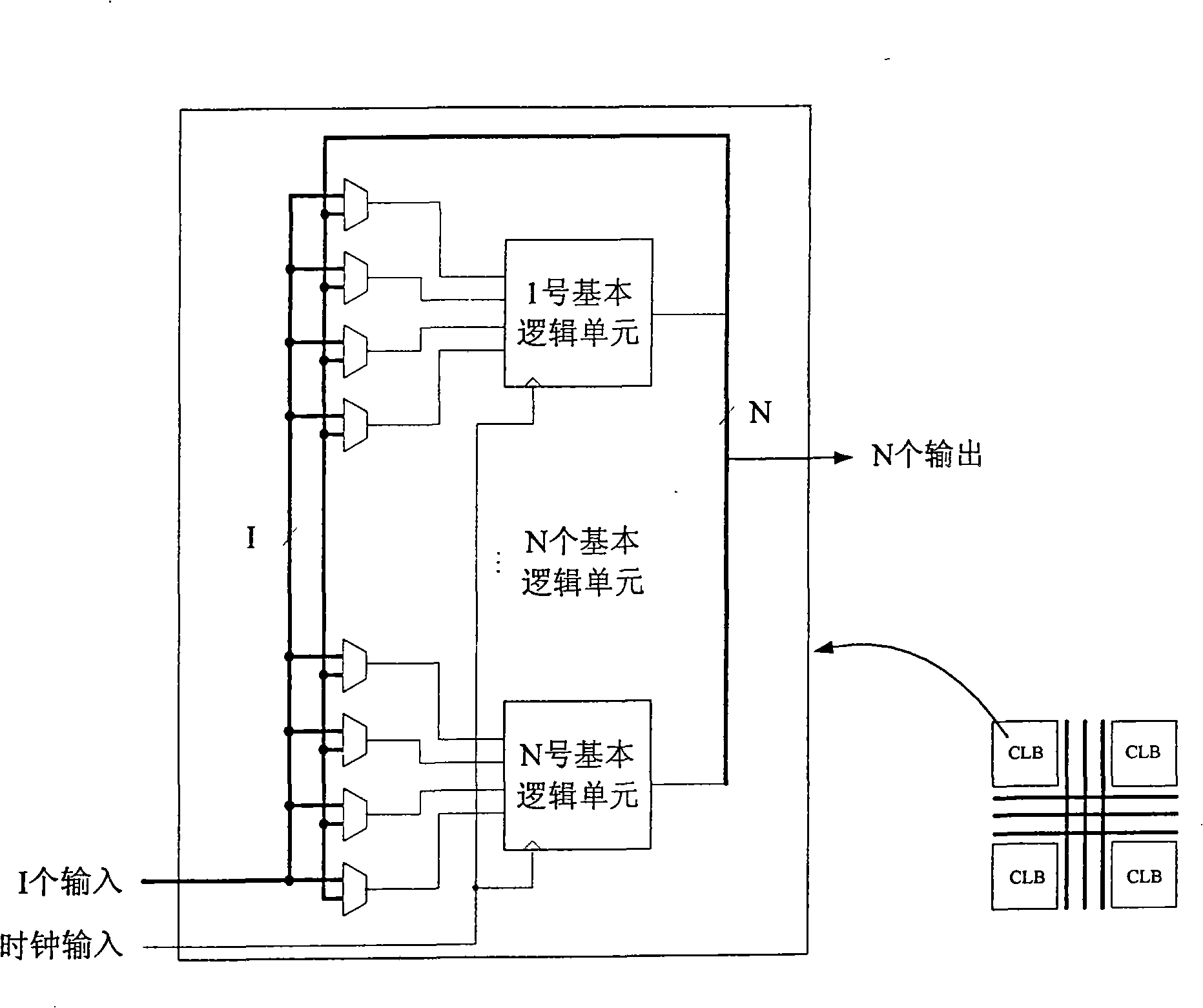

[0126] attached Figure 4 , attached Figure 5 And attached Image 6 It is the logic unit structure diagram of three series FPGAs of Xilinx Company. According to the functions of user circuits that FPGA can realize, the circuits can be divided into three categories: 1) Logic functions composed of special devices; 2) Logic functions composed of look-up tables and flip-flops Logical functions composed of special devices; 3) Logical functions composed of IP cores such as CPU, RAM blocks, and DSP cores. Among them, the user circuits completed by the logic unit are only 1) and 2). The present invention simplifies the logical units realizing the user circuit 1) and 2) into a three-level model according to the mutual driving conditions of various devices: the first level is a lookup table, the second level is a special device, and the third level is a sequential device ,Such as Figure 7shown. The lookup table is used to map the combinational logic of any K input, and at the sam...

PUM

Login to View More

Login to View More Abstract

Description

Claims

Application Information

Login to View More

Login to View More