Semiconductor device and manufacturing method of same

A technology of semiconductors and devices, applied in the field of semiconductor devices and their manufacturing, capable of solving problems such as SMT without giving any clear guidance, without establishing FinFET or nanowire transistors

- Summary

- Abstract

- Description

- Claims

- Application Information

AI Technical Summary

Problems solved by technology

Method used

Image

Examples

no. 1 example

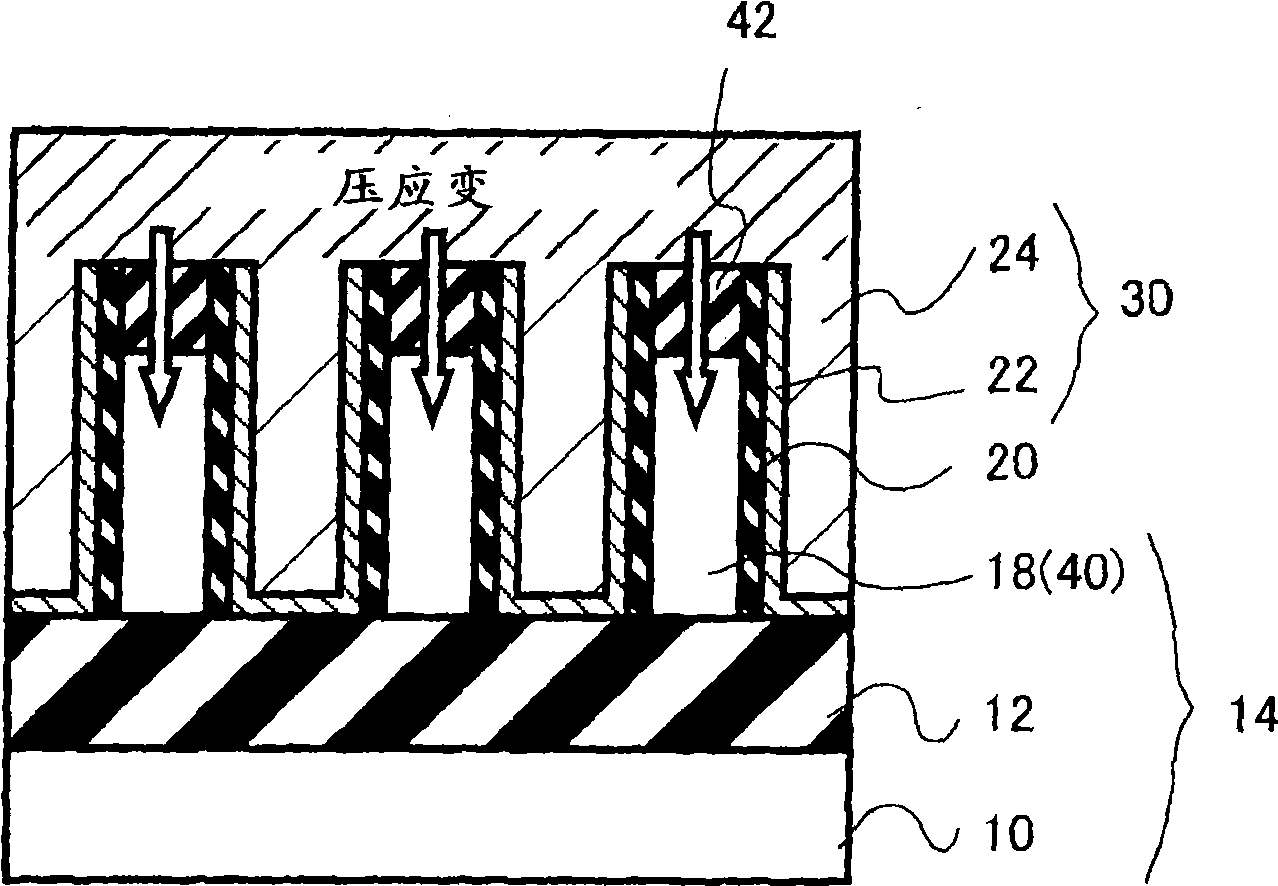

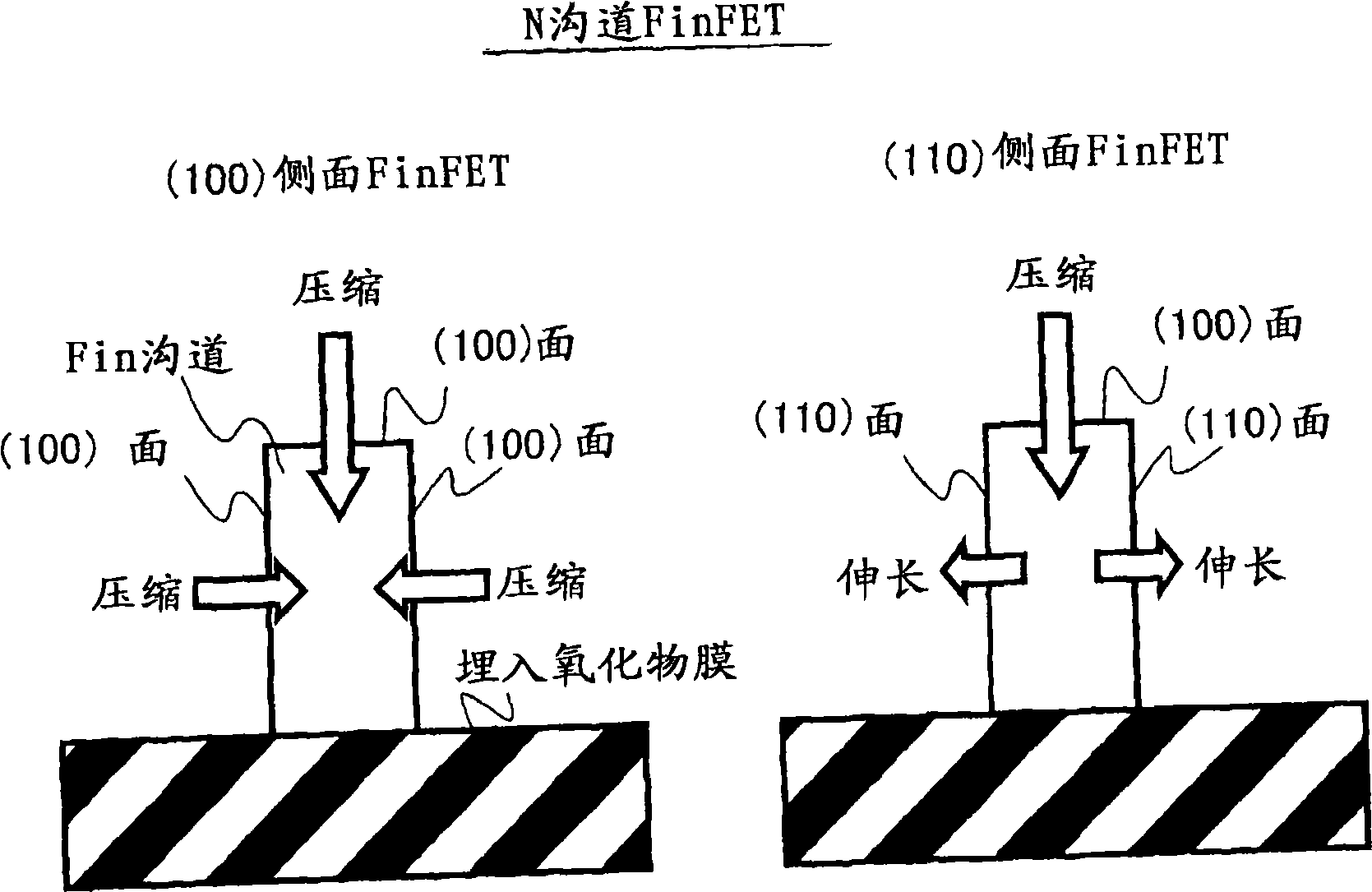

[0048] The semiconductor device according to the present embodiment is configured to include: a semiconductor substrate; a cuboid-shaped semiconductor layer formed on the upper portion of the semiconductor substrate and having a top surface parallel to the main surface of the semiconductor substrate and a surface perpendicular to the semiconductor substrate. (100) plane oriented sides of the main surface of the bottom; and a p-channel Metal Insulator Semiconductor Field Effect Transistor (pMISFET). The pMISFET has: a channel region formed at least at the side surfaces of the cuboid-shaped semiconductor layer; a gate dielectric film formed at least at the side surfaces of the cuboid-shaped semiconductor layer; a gate electrode covering the channel region, the gate a dielectric film sandwiched between the gate electrode and the channel region; and a pair of source / drain regions formed in the rectangular parallelepiped-shaped semiconductor layer in such a manner that the channel r...

no. 2 example

[0072] The semiconductor device of the present embodiment is a p-channel nanowire transistor, which is compatible with figure 1 Similar to the semiconductor device of the first embodiment shown in , in which the hard mask layer 42 is removed and is also formed on the top surface of the rectangular semiconductor layer 40, that is, on the upper surface of the channel region 18 by interposing the gate insulating film A gate electrode is provided. The present embodiment is similar to the first embodiment except that the structure of a FinFET is used as the nanowire transistor structure; therefore, descriptions thereof will be omitted.

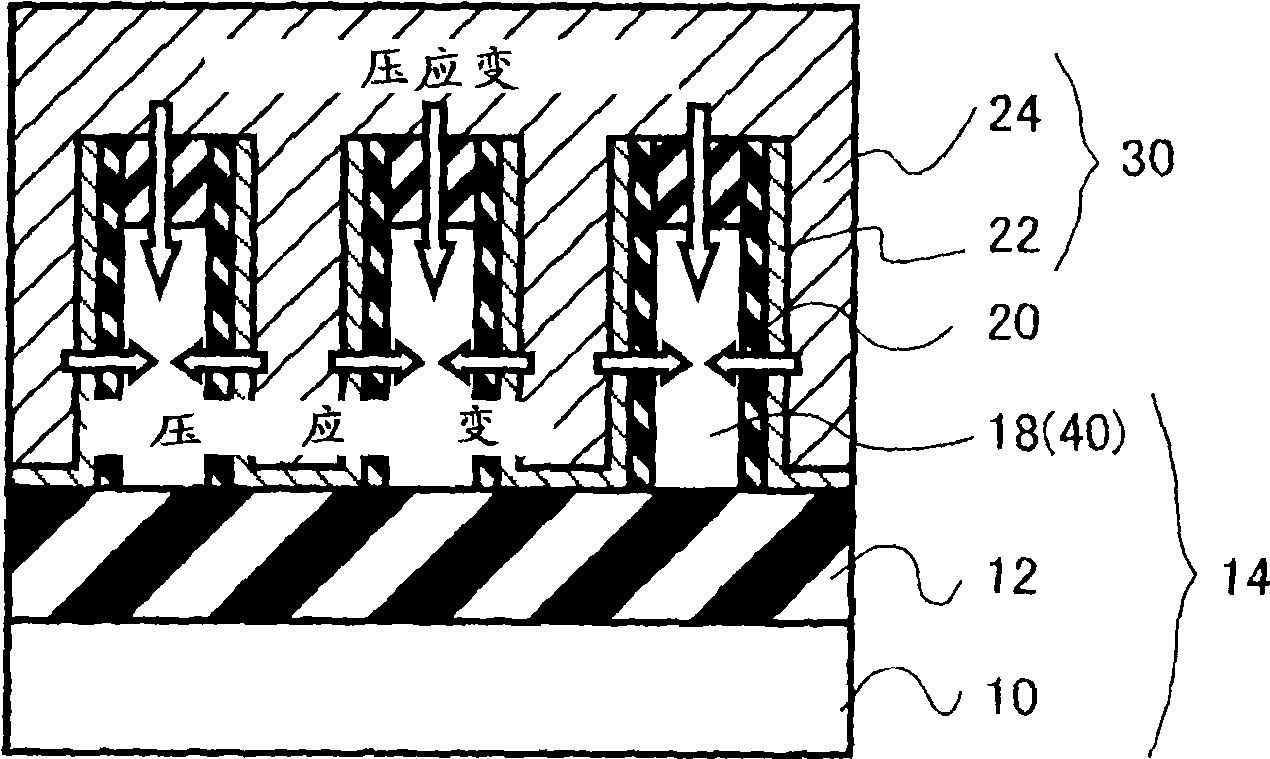

[0073] Figure 15 is a schematic cross-sectional view of the semiconductor device of this embodiment in a direction at right angles to its gate length direction. Such as Figure 15 As shown in , the gate insulating film 20 is also formed on the upper surface of the channel region 18 formed at the cuboid-shaped semiconductor layer 40 having the (...

no. 3 example

[0086] The semiconductor device of this embodiment is a p-channel FinFET, and figure 1 Similar to the semiconductor device of the first embodiment shown in , in which the semiconductor film of the gate electrode is modified such that its lowermost surface is above the top surface of the cuboid-shaped semiconductor layer. Except for this structural difference, the device is the same as the first embodiment; therefore, repeated description will be omitted here.

[0087] Figure 22 is a schematic cross-sectional view of the semiconductor device of this embodiment in a direction at right angles to its gate length direction. like Figure 22 As shown in , the lowermost surface of the polysilicon film 24 of the gate electrode 30 is provided to cover the upper surface of the channel region 18 , that is, the top surface of the rectangular semiconductor layer 40 . In other words, it becomes a structure in which the space between adjacent channel regions 18 (rectangular semiconductor ...

PUM

| Property | Measurement | Unit |

|---|---|---|

| Height | aaaaa | aaaaa |

Abstract

Description

Claims

Application Information

Login to View More

Login to View More