Memory access dispatching device, dispatching method and memory access control system

A memory access and scheduling device technology, applied in the direction of instruments, televisions, electrical digital data processing, etc., can solve problems such as failure to achieve scheduling, achieve the effect of reducing delay, high access efficiency, and reducing the probability of pre-charging

- Summary

- Abstract

- Description

- Claims

- Application Information

AI Technical Summary

Problems solved by technology

Method used

Image

Examples

Embodiment Construction

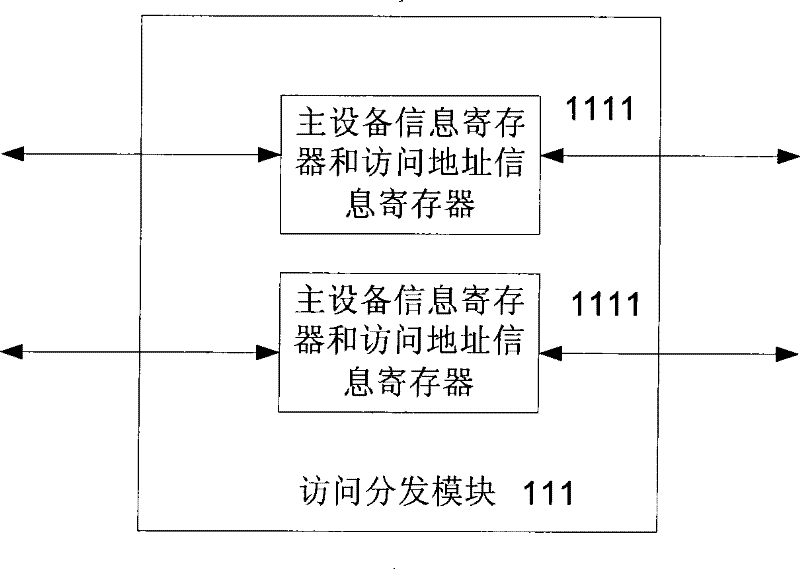

[0042] For ease of description, according to an exemplary embodiment of the present invention, the memory to be accessed includes, for example, four storage banks (Banks), and the regions are divided according to different master devices, and the memory here is, for example, a DRAM. The first storage group B0 and the second storage group B1 are mainly allocated to the CPU, referred to as the CPU storage area; the third storage group B2 and the fourth storage group B3 are mainly allocated to the video processing unit, referred to as the video storage area. To meet certain storage requirements, the CPU also allows access to video storage areas assigned to the video processing unit, namely the third storage group B2 and the fourth storage group B3. It can be understood that in other embodiments, the DRAM can be allocated in other forms. For example, the DRAM can also be divided into more areas and allocated to more master devices, a part of the storage group is allocated to the CP...

PUM

Login to View More

Login to View More Abstract

Description

Claims

Application Information

Login to View More

Login to View More