Method and system for detecting defects in manufacture of integrated circuit

一种集成电路、缺陷的技术,应用在集成电路制造的自动缺陷检测领域,能够解决技术不充分等问题

- Summary

- Abstract

- Description

- Claims

- Application Information

AI Technical Summary

Problems solved by technology

Method used

Image

Examples

Embodiment Construction

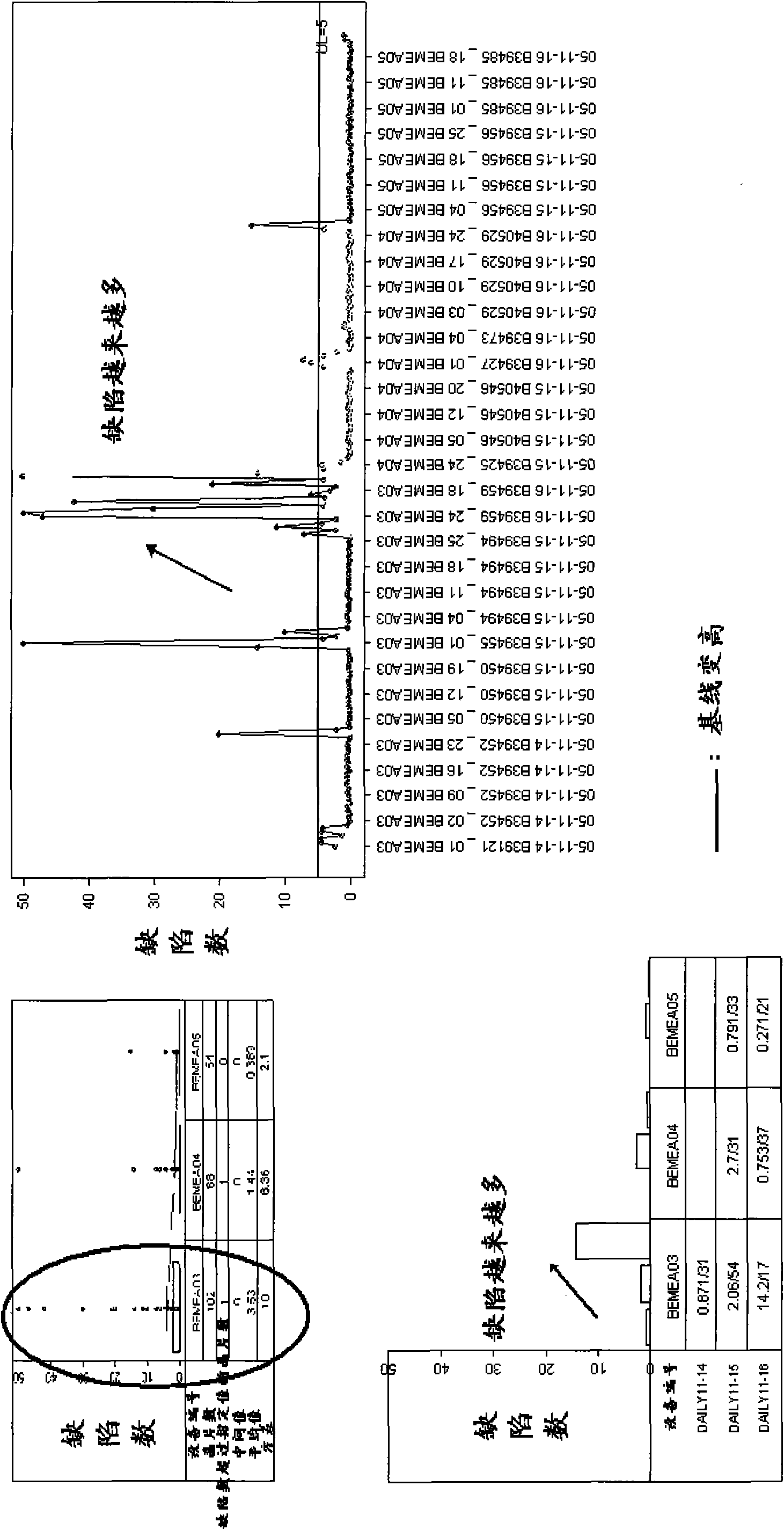

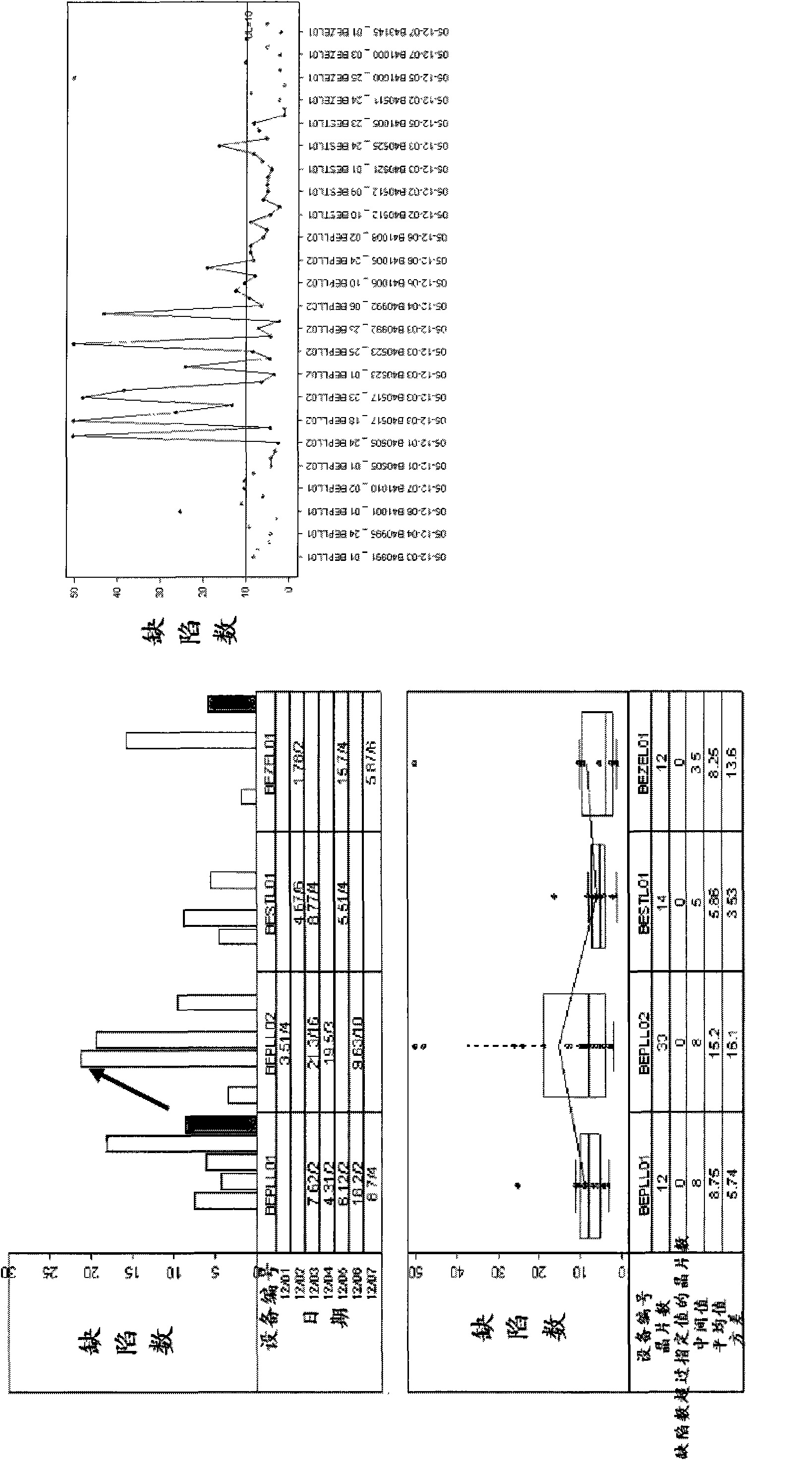

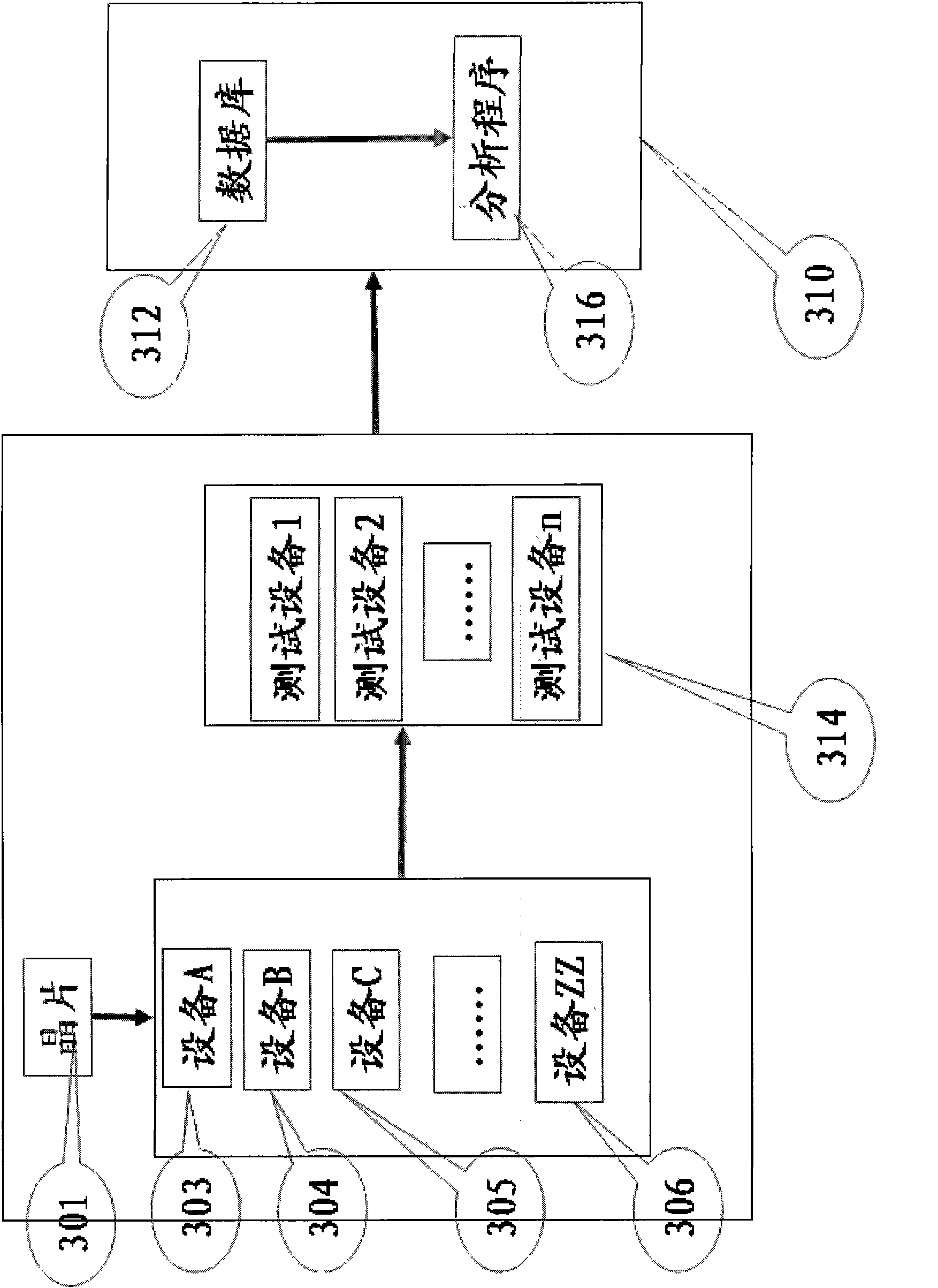

[0019] The present invention relates to integrated circuits and methods of fabricating semiconductor devices. More specifically, the present invention provides methods and systems for automated defect detection in integrated circuit fabrication. By way of example only, the invention has been applied to the detection of defects in the manufacture of integrated circuits using non-parametric statistical tools. However, it should be recognized that the present invention has broader applicability. For example, the invention can be applied to detecting defects in other manufacturing processes.

[0020] As mentioned above, for the manufacture of semiconductor wafers, it is important to detect manufacturing defects and identify possible sources of manufacturing defects. Previously, various conventional methods have been developed. Unfortunately, conventional methods are often insufficient.

[0021] For example, one of the methods for identifying the source of defects has been test...

PUM

Login to View More

Login to View More Abstract

Description

Claims

Application Information

Login to View More

Login to View More