Front-end processed wafer having through-chip connections

A front-end processing and back-end processing technology, applied in the field of electrical connection, can solve problems such as useless chips, failure to make connections, discarding, etc., and achieve the effect of reducing cost impact and eliminating the risk of damage to devices

- Summary

- Abstract

- Description

- Claims

- Application Information

AI Technical Summary

Problems solved by technology

Method used

Image

Examples

Embodiment Construction

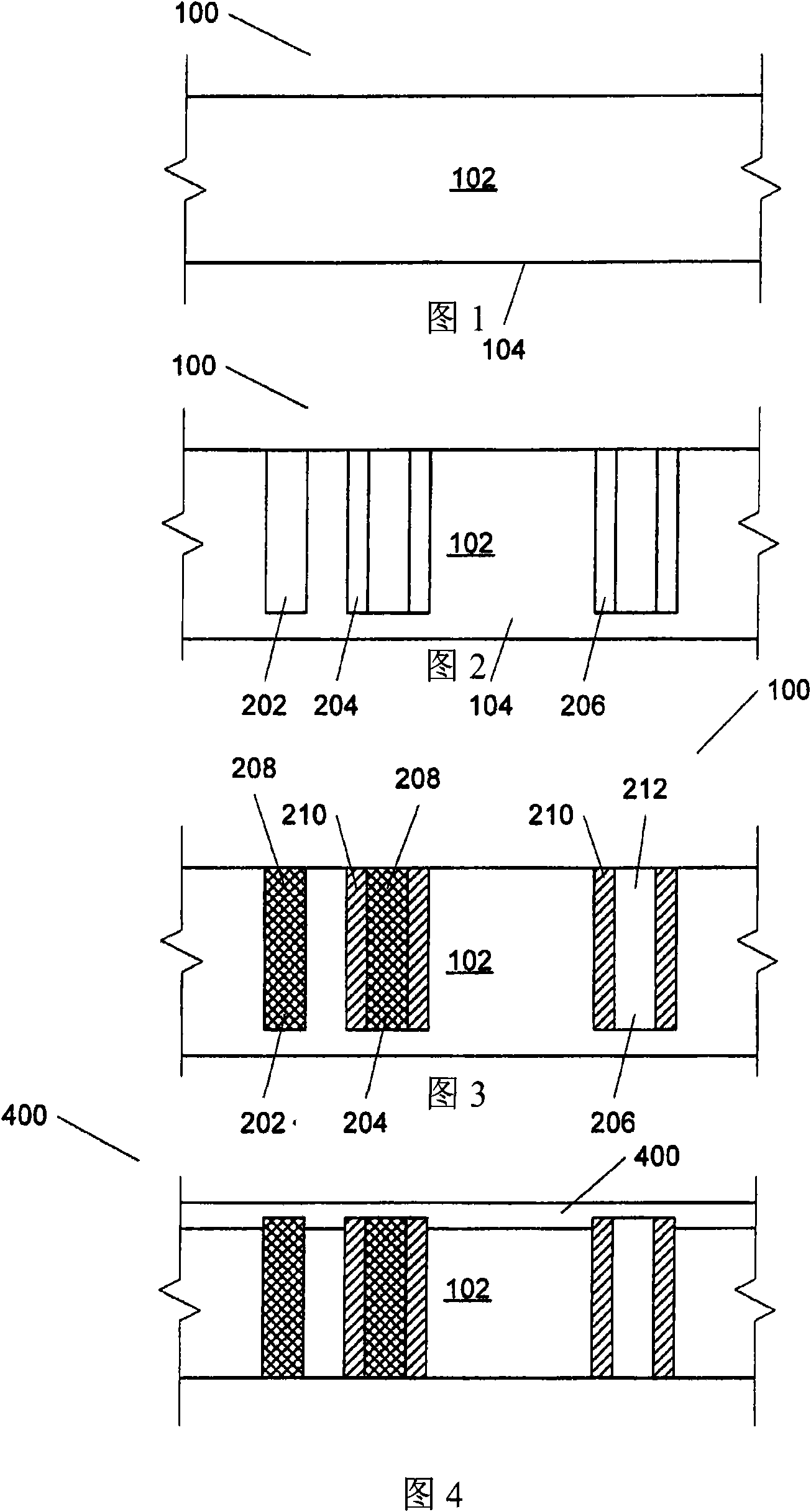

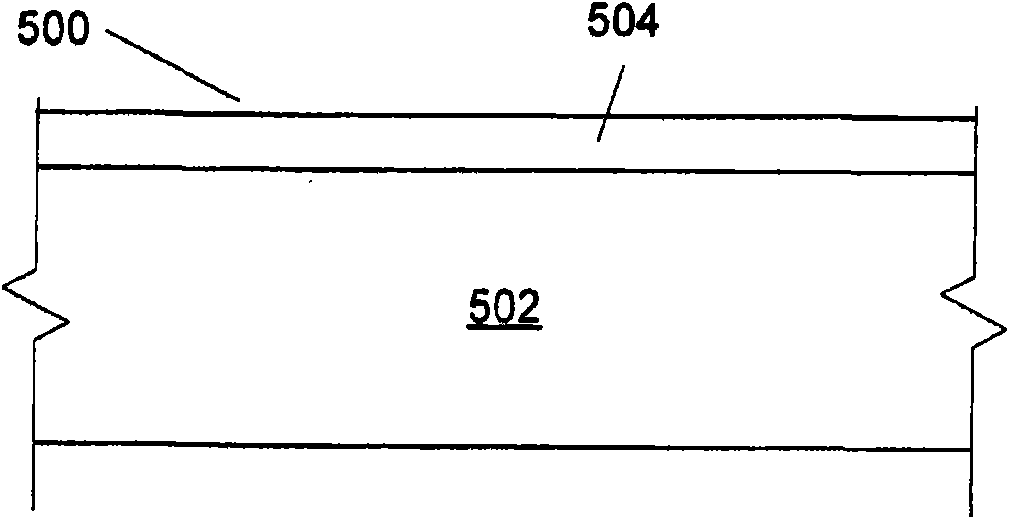

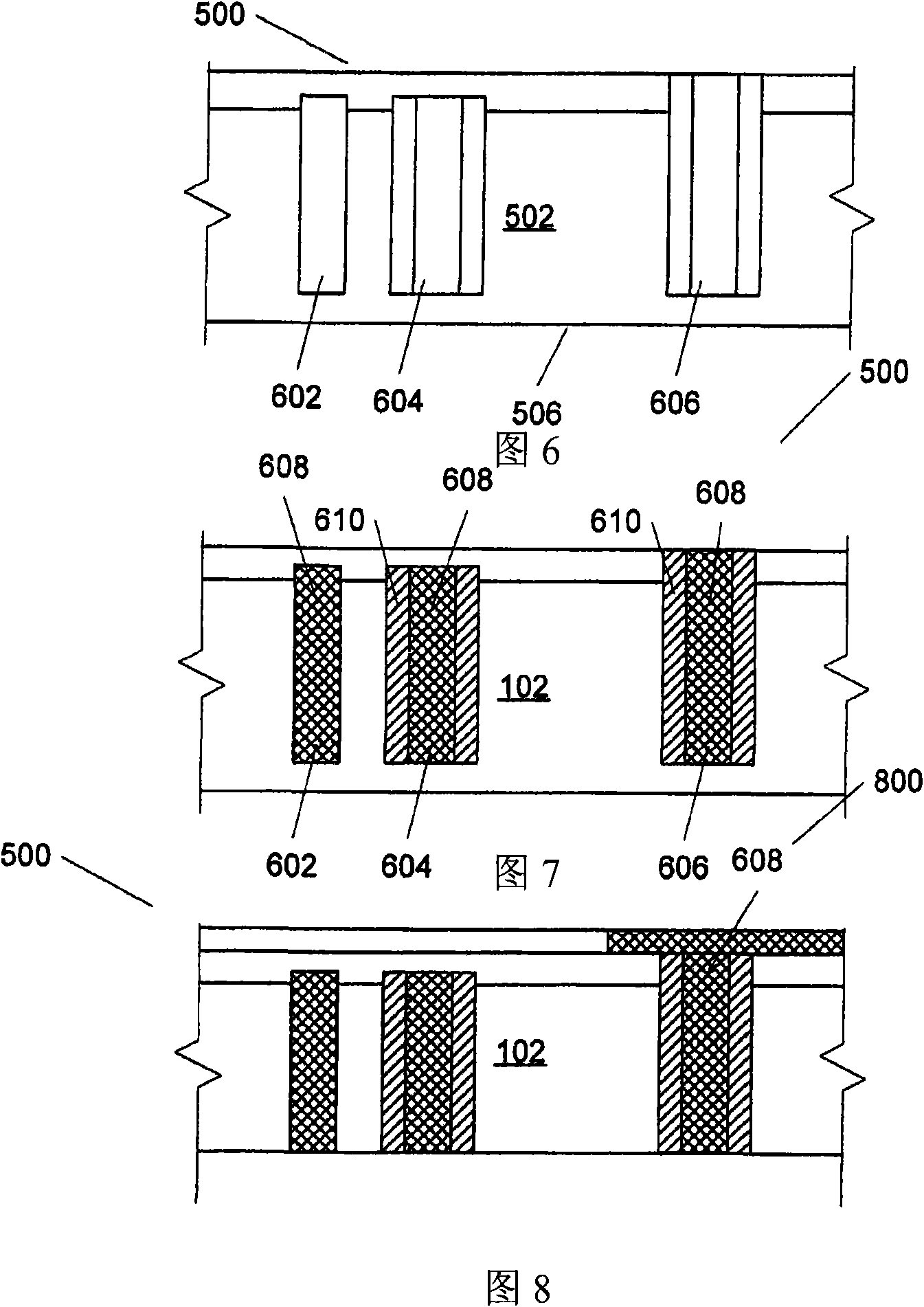

[0019] Serial numbers incorporated herein by reference as 11 / 329,481, 11 / 329,506, 11 / 329,539, 11 / 329,540, 11 / 329,556, 11 / 329,557, 11 / 329,558, 11 / 329,574, 11 / 329,575, 11 / 329,576, 5 US Patent Application 422,551 describes various techniques for forming small, deep vias in semiconductor wafers and electrical contacts for semiconductor wafers. Our technology allows for previously unavailable via densities and locations, and can be performed at chip or wafer scale.

[0020] If it is desired to establish through-chip electrical connections, but minimize the risk involved in fully handling the wafer (ie, the device support wafer), the following approach can be used.

[0021] In summary, the method directly involves forming vias in a blank wafer at the locations where they should be associated with the devices that will be on the wafer once front-end processing is complete, making the vias conductive, and then fabricating the devices on the wafer, thereby utilizing Connections betwe...

PUM

Login to View More

Login to View More Abstract

Description

Claims

Application Information

Login to View More

Login to View More