Manufacture method of wafer level upright type diode packaging structure

A technology of packaging structure and manufacturing method, applied in semiconductor/solid-state device manufacturing, electrical components, electrical solid-state devices, etc., can solve the problems of increased material cost, processing cost, poor electrical conductivity, long electrical path, etc., to reduce material cost, The effect of good electrical conductivity and short electrical path

- Summary

- Abstract

- Description

- Claims

- Application Information

AI Technical Summary

Problems solved by technology

Method used

Image

Examples

Embodiment Construction

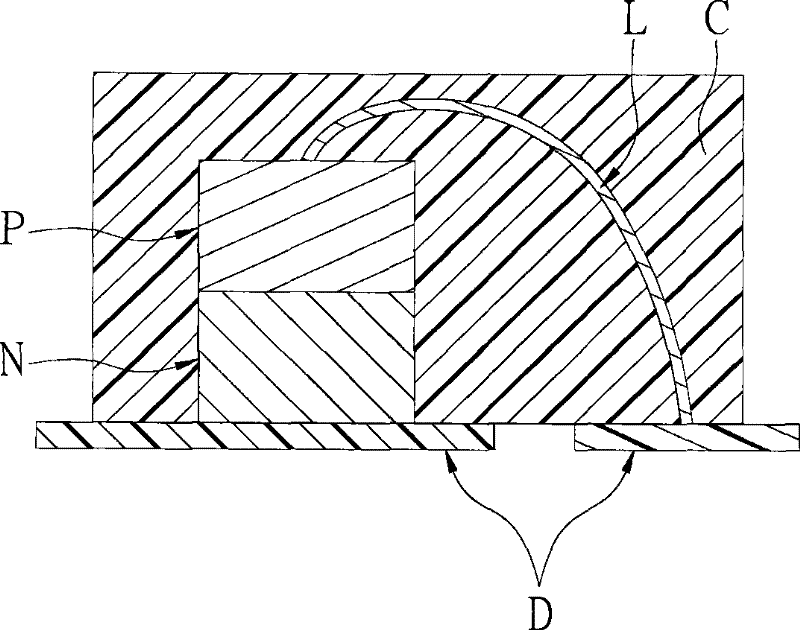

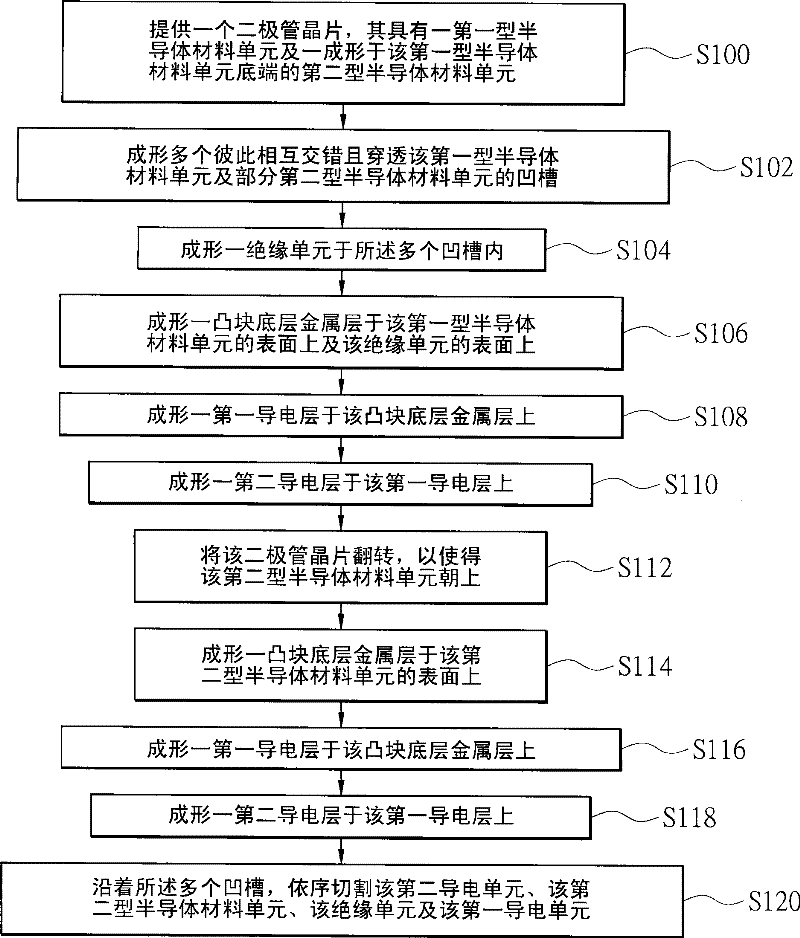

[0104] see figure 2 , Figure 2A1 to Figure 2I1 ,and Figure 2I2 shown, where figure 2 It is a flow chart of the first embodiment of the manufacturing method of the wafer-level vertical diode packaging structure of the present invention; Figure 2A1 to Figure 2I1 It is a schematic cross-sectional view of the manufacturing process of the first embodiment of the manufacturing method of the wafer-level vertical diode packaging structure of the present invention; Figure 2I2 It is a three-dimensional schematic view of the first embodiment of the wafer-level vertical diode packaging structure of the present invention. It can be seen from the above-mentioned figures that the first embodiment of the present invention provides a method for manufacturing a wafer-level vertical diode packaging structure, which includes the following steps:

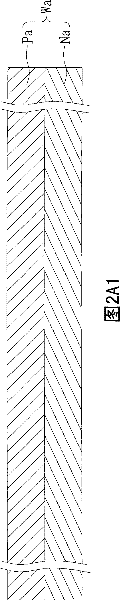

[0105] Step S100 is: first, coordinate figure 2 , Figure 2A1 and Figure 2A2 shown (where Figure 2A1 for Figure 2A2 Partial cross-se...

PUM

Login to View More

Login to View More Abstract

Description

Claims

Application Information

Login to View More

Login to View More