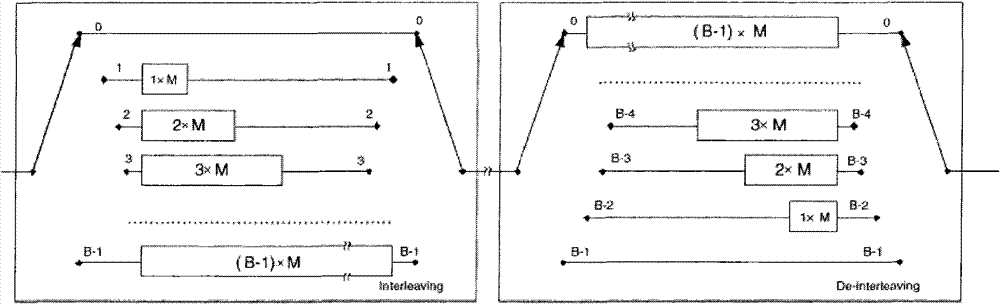

Method for realizing convolution interleaving and de-interleaving of time domain by using SDRAM

A convolutional interleaving and deinterleaving technology, applied in the direction of using convolutional code error correction/error detection, data representation error detection/correction, etc., can solve the problems of SDRAM long time, SDRAM performance degradation, etc.

- Summary

- Abstract

- Description

- Claims

- Application Information

AI Technical Summary

Problems solved by technology

Method used

Image

Examples

Embodiment Construction

[0071] The present invention is applicable to any application scenario requiring convolutional interleaving and deinterleaving techniques.

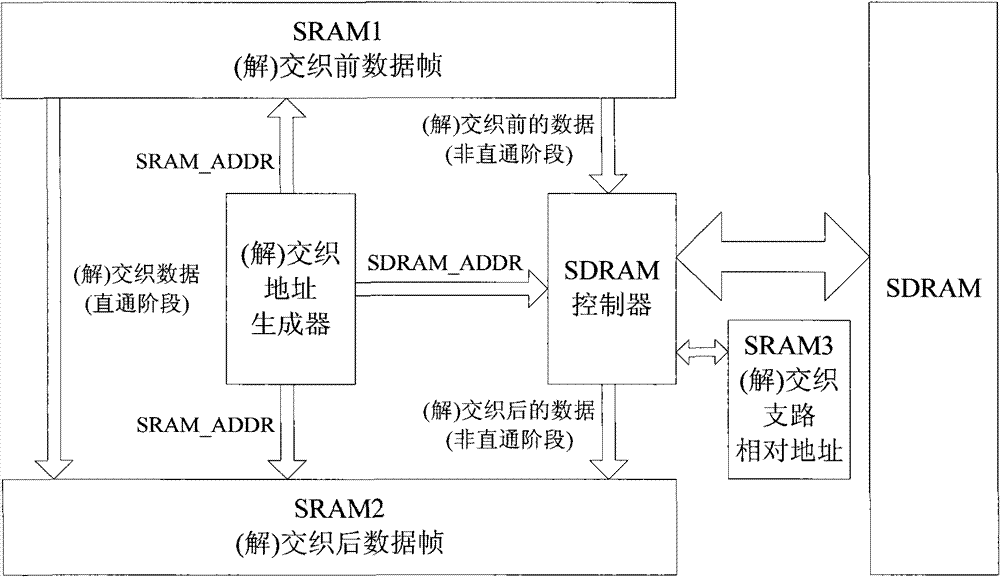

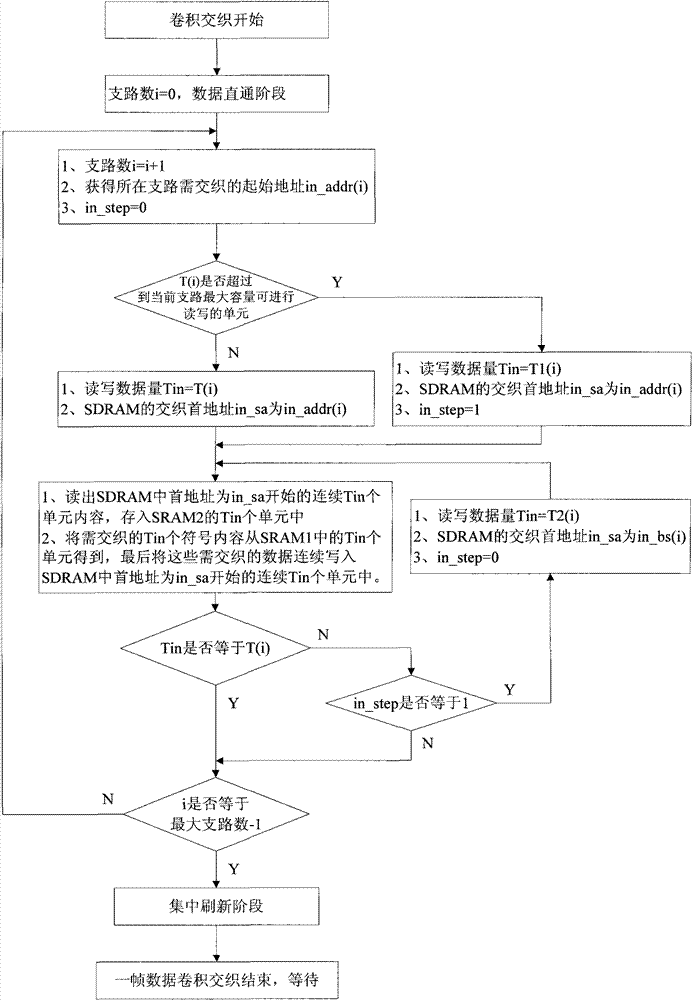

[0072] like figure 2 As shown, the figure illustrates the system block diagram of convolution (de)interleaving in the present invention. The whole system is composed of convolution (de)interleaving address generator, (de)interleaving and before and after data frame SRAM units (SRAM1 and SRAM2), SDRAM controller and (de)interleaver storage unit SDRAM. The address generator generates the address SDRAM_ADDR in the SDRAM and the address SRAM_ADDR of the (de)interleaved data in the data frame SRAM unit when each branch is (de)interleaved. The relative address of the previous frame interleaved data in each branch is stored in a SRAM unit (SRAM3). In the no-delay branch, the corresponding (de)interleaved data is directly written from the unit of SRAM1 whose address is SRAM_ADDR to the corresponding unit of SRAM2. In the branch with delay, th...

PUM

Login to View More

Login to View More Abstract

Description

Claims

Application Information

Login to View More

Login to View More