Interface method of USB 1.1 bus and high-speed intelligent unified bus

A USB1.1 bus technology, applied in the interface field of USB1.1 bus and high-speed intelligent unified bus, can solve the problem of low speed, achieve the effect of increasing reliability, effective and reliable interconnection, and reducing costs

- Summary

- Abstract

- Description

- Claims

- Application Information

AI Technical Summary

Problems solved by technology

Method used

Image

Examples

Embodiment Construction

[0020] refer to Figure 1-6 , to describe the present invention in detail.

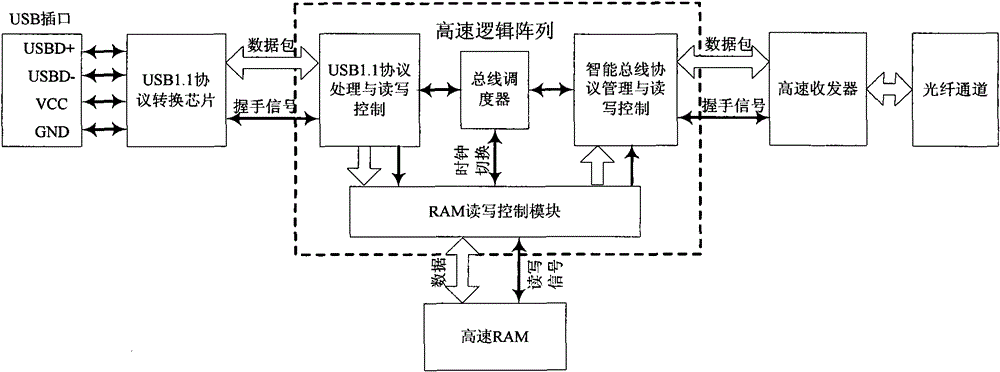

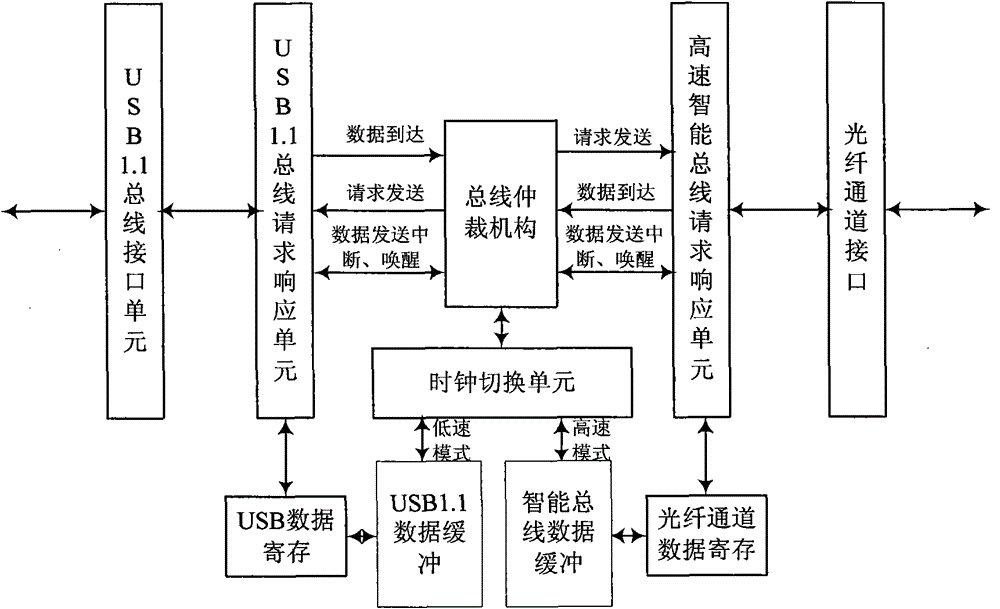

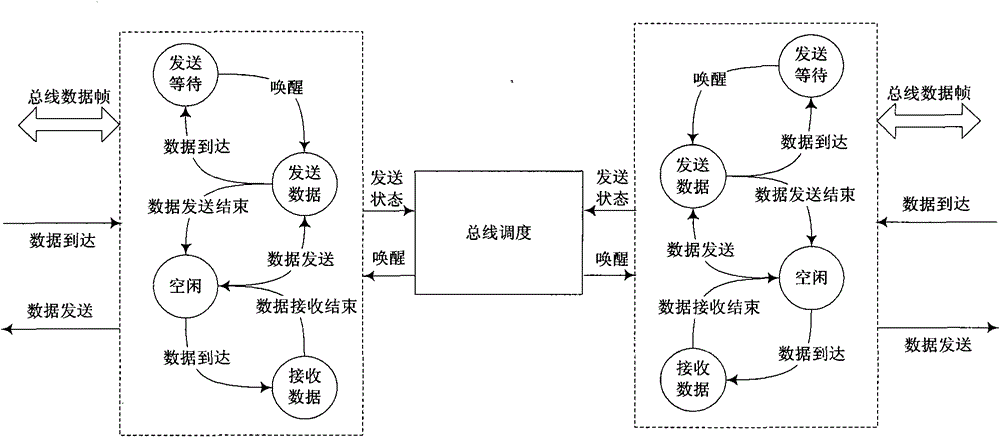

[0021] This embodiment is an interface method between the USB1.1 bus and the smart bus, which realizes the high-speed optical fiber transmission of the USB1.1 device through the high-speed smart bus and the data reception of the high-speed optical fiber data based on the USB1.1 bus. The hardware structure of this embodiment includes a USB1.1 bus controller, an intelligent bus controller, a central bus arbitration controller and a high-speed mass memory.

[0022] In this embodiment, the scheduling and interface control of the two buses are mainly completed in the high-speed logic array FPGA, and the FPGA adopts the EP1C12 chip of the Cyclone series of Altera Corporation of the United States. The chip has a density of 12060 LE units, which can fully meet the needs of image processing algorithms and system logic control; 169 user-available I / O ports meet the system's multi-chip connection requirements f...

PUM

Login to View More

Login to View More Abstract

Description

Claims

Application Information

Login to View More

Login to View More