Underlying hardware mapping method for integrated circuit as well as time sequence constraint method and device for data control flow

An integrated circuit and data control technology, applied in the direction of electrical digital data processing, special data processing applications, instruments, etc., can solve problems such as time differences in realization

- Summary

- Abstract

- Description

- Claims

- Application Information

AI Technical Summary

Problems solved by technology

Method used

Image

Examples

Embodiment Construction

[0063] The present invention will be further described in detail below through specific embodiments in conjunction with the accompanying drawings.

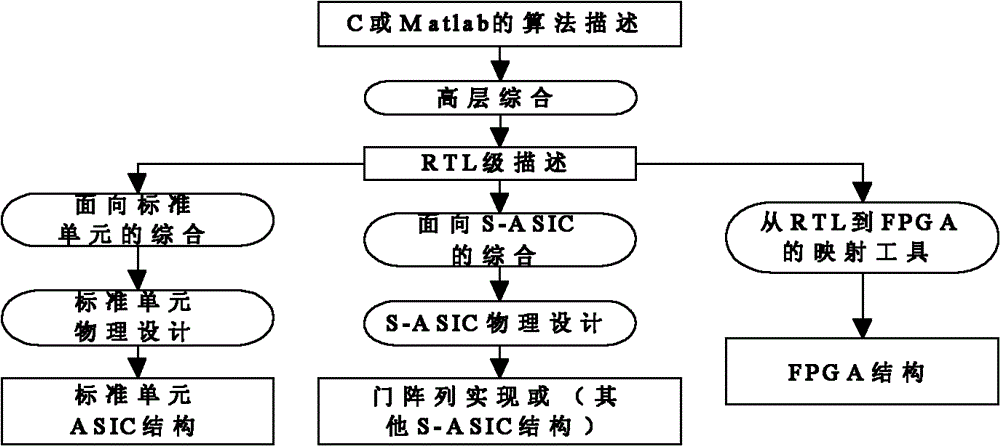

[0064] Looking back at the development of integrated circuit design methodology, we can see that: when the integrated circuit manufacturing process entered the era of 1um, the design method with the gate array as the basic unit appeared; when the integrated circuit manufacturing process entered the era of 0.5um, there appeared the The standard unit is the design method of the basic unit; when the integrated circuit manufacturing process enters the era of 0.18um, the design method with the IP core as the basic unit appears. It can be seen from this that: on the one hand, the design methodology of integrated circuits develops with the development of integrated circuit manufacturing processes; on the other hand, the unit granularity of basic units (gates, standard cells, IP cores) used in integrated circuit design methodology keep gr...

PUM

Login to View More

Login to View More Abstract

Description

Claims

Application Information

Login to View More

Login to View More