Successive approximation analog-digital converter and method thereof

An analog-to-digital, successive approximation technology, applied in analog-to-digital conversion, code conversion, instruments, etc., can solve problems such as the ratio of series capacitors is not an integer multiple, and the problem of capacitor matching is reduced.

- Summary

- Abstract

- Description

- Claims

- Application Information

AI Technical Summary

Problems solved by technology

Method used

Image

Examples

Embodiment Construction

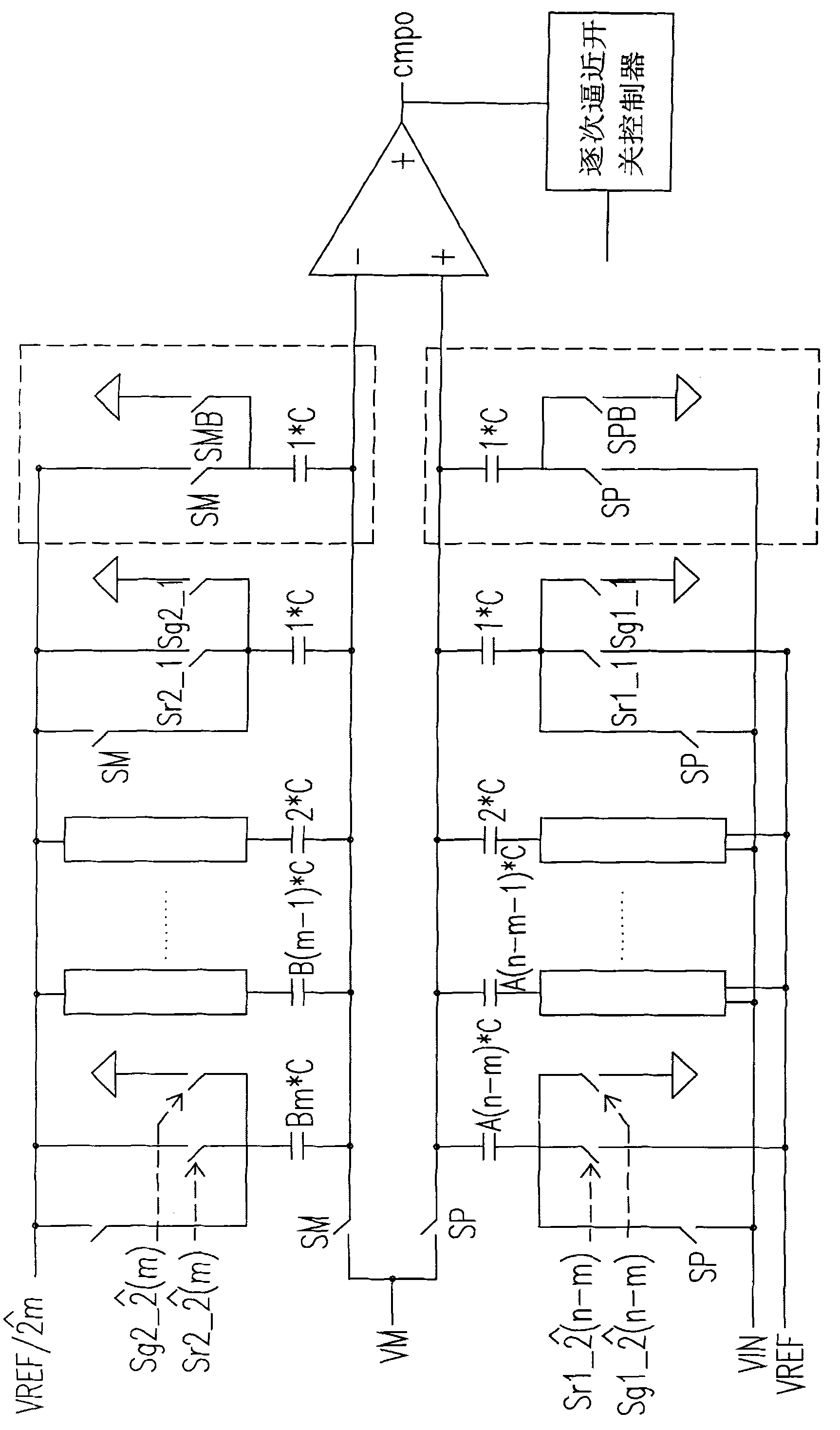

[0031] Please refer to figure 2, is a schematic circuit diagram showing a successive approximation analog-to-digital converter according to a first preferred embodiment of the present invention. The upper half of the figure is the LSB capacitor group, the lower half is the MSB group, the MSB capacitor group has the most significant bit, the LSB capacitor group has the least significant bit, the least significant bit capacitor group contains m bits, and the maximum effective The bit capacitor group includes n-m bits, n is the number of digits of the successive approximation analog-to-digital converter, each of which corresponds to at least one capacitor and at least one switch, and the first conversion refers to n-m of the most effective bit capacitor group Bit conversion, the second conversion is the conversion of m bits of the least significant bit capacitor bank, the successive approximation switch controller is coupled to the first output terminal of the comparator, and ac...

PUM

Login to View More

Login to View More Abstract

Description

Claims

Application Information

Login to View More

Login to View More