On-chip clock uncertainty measurement circuit device and system

A technique for measuring uncertainty and measuring circuits, which is applied in the field of measuring the uncertainty of chip clocks. It can solve the problems of large data volume circuit scale, process dependence, and large noise, and achieve less control data, large measurement range, and high measurement accuracy. Effect

- Summary

- Abstract

- Description

- Claims

- Application Information

AI Technical Summary

Problems solved by technology

Method used

Image

Examples

Embodiment Construction

[0041] In order to make the purpose, technical solution and advantages of the present invention clearer, the measurement circuit device and system with uncertain on-chip clock of the present invention will be further described in detail below in conjunction with the accompanying drawings and embodiments. It should be understood that the specific embodiments described here are only used to explain the present invention, not to limit the present invention.

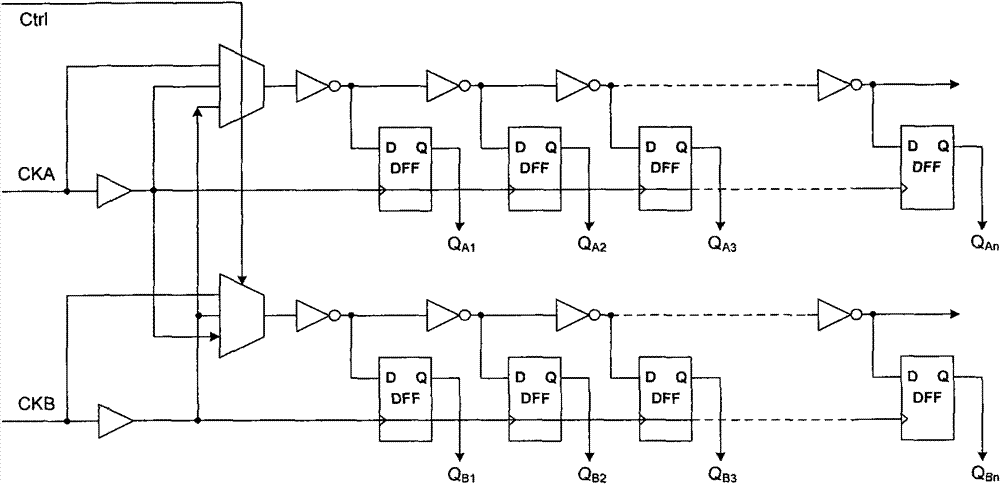

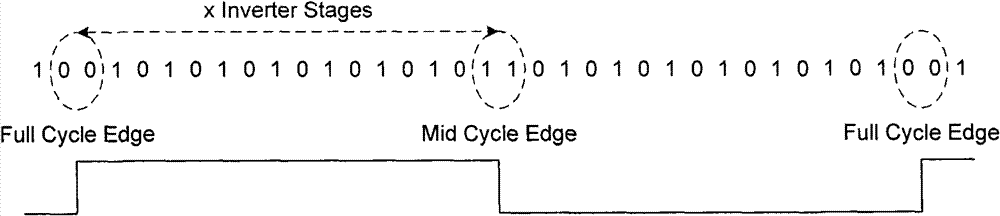

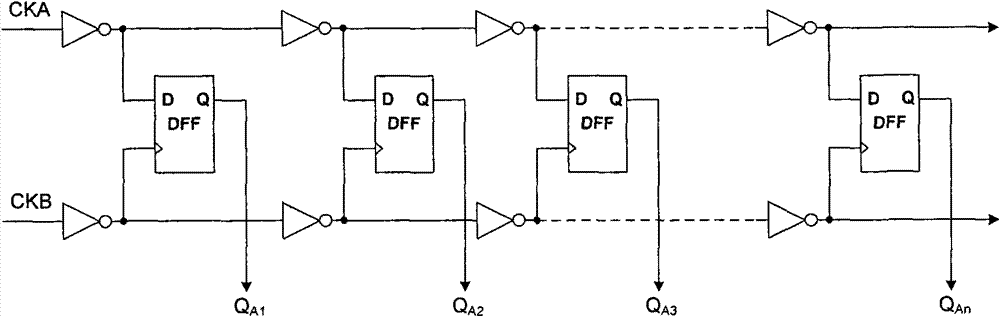

[0042] The on-chip clock uncertainty measurement circuit device and system of the embodiments of the present invention utilize the principle of a delay-locked loop (Delay-Locked Loop). The on-chip clock uncertainty measurement system of the embodiment of the present invention includes two parts: an on-chip clock uncertainty measurement circuit device 1 (Skew and Jitter Measurement, SJM); and a scale circuit (Ring).

[0043] Wherein, the on-chip clock uncertainty measurement circuit device is used to measure the clock skew an...

PUM

Login to View More

Login to View More Abstract

Description

Claims

Application Information

Login to View More

Login to View More