System chip JTAG (Joint Test Action Group) debugging control method based on chip flash memory

A system chip and control method technology, applied in the direction of measuring devices, instruments, measuring electronics, etc., can solve problems such as data security risks and poor security, and achieve the effects of improving security, facilitating debugging, and protecting data security

- Summary

- Abstract

- Description

- Claims

- Application Information

AI Technical Summary

Problems solved by technology

Method used

Image

Examples

Embodiment Construction

[0041] The present invention will be further described below in conjunction with the accompanying drawings.

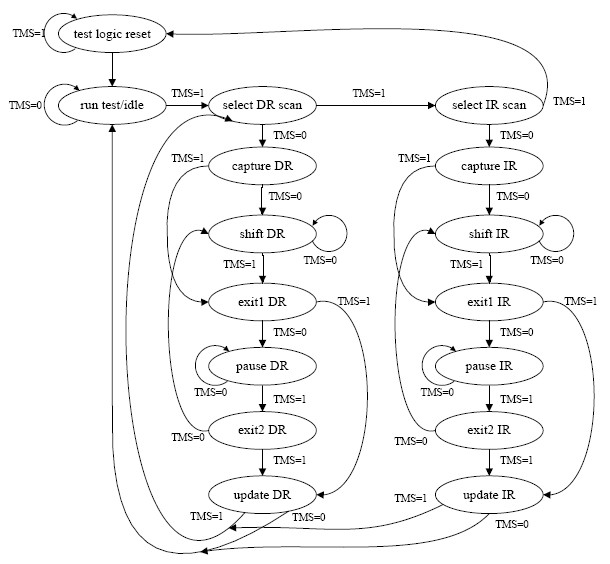

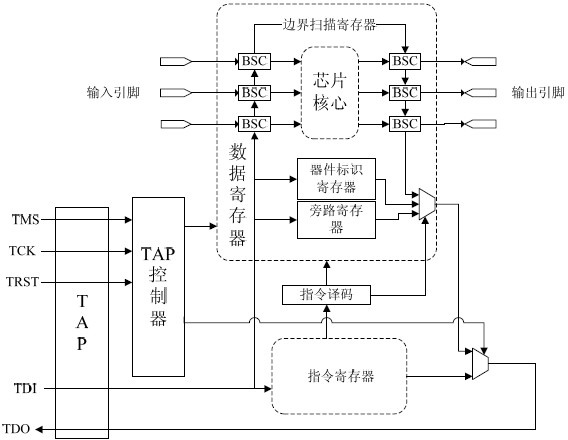

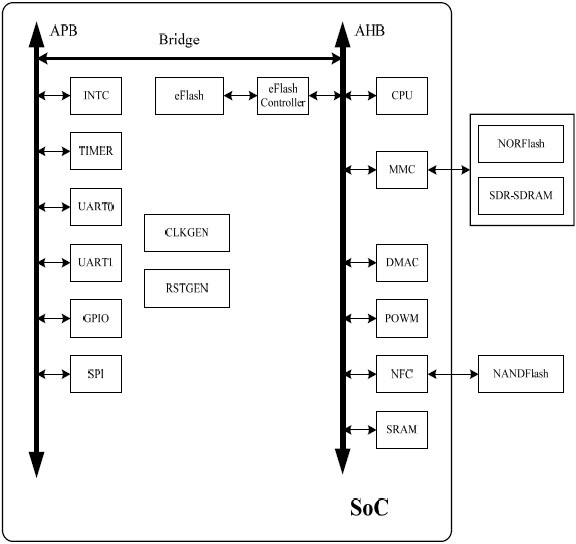

[0042] refer to Figure 3 ~ Figure 5 , a system chip JTAG debugging control method based on on-chip flash memory, the JTAG realizes the control of the boundary scan chain through TAP, and the TAP interface includes a TCK interface, a TMS interface, a TDI interface, a TDO interface and a TRST interface, and the TCK The interface, TMS interface and TDI interface are respectively controlled by a two-choice data selector. The two inputs of the data selector are normal signal and fixed low level or high level respectively, and then through a bit in the system chip The register REG1 with a width of one bit is used to control the data selector. When the value of the register REG1 is one, the low-level signal is connected to the TCK interface, the TMS interface and the TDI interface, and the JTAG interface is shielded; while the value of the register REG1 is zero. , connect t...

PUM

Login to View More

Login to View More Abstract

Description

Claims

Application Information

Login to View More

Login to View More