Domain structure of memory circuit

A technology of memory circuit and layout structure, which is applied to circuits, electrical components, electric solid-state devices, etc., and can solve problems such as time-consuming search and error-prone

- Summary

- Abstract

- Description

- Claims

- Application Information

AI Technical Summary

Problems solved by technology

Method used

Image

Examples

Embodiment Construction

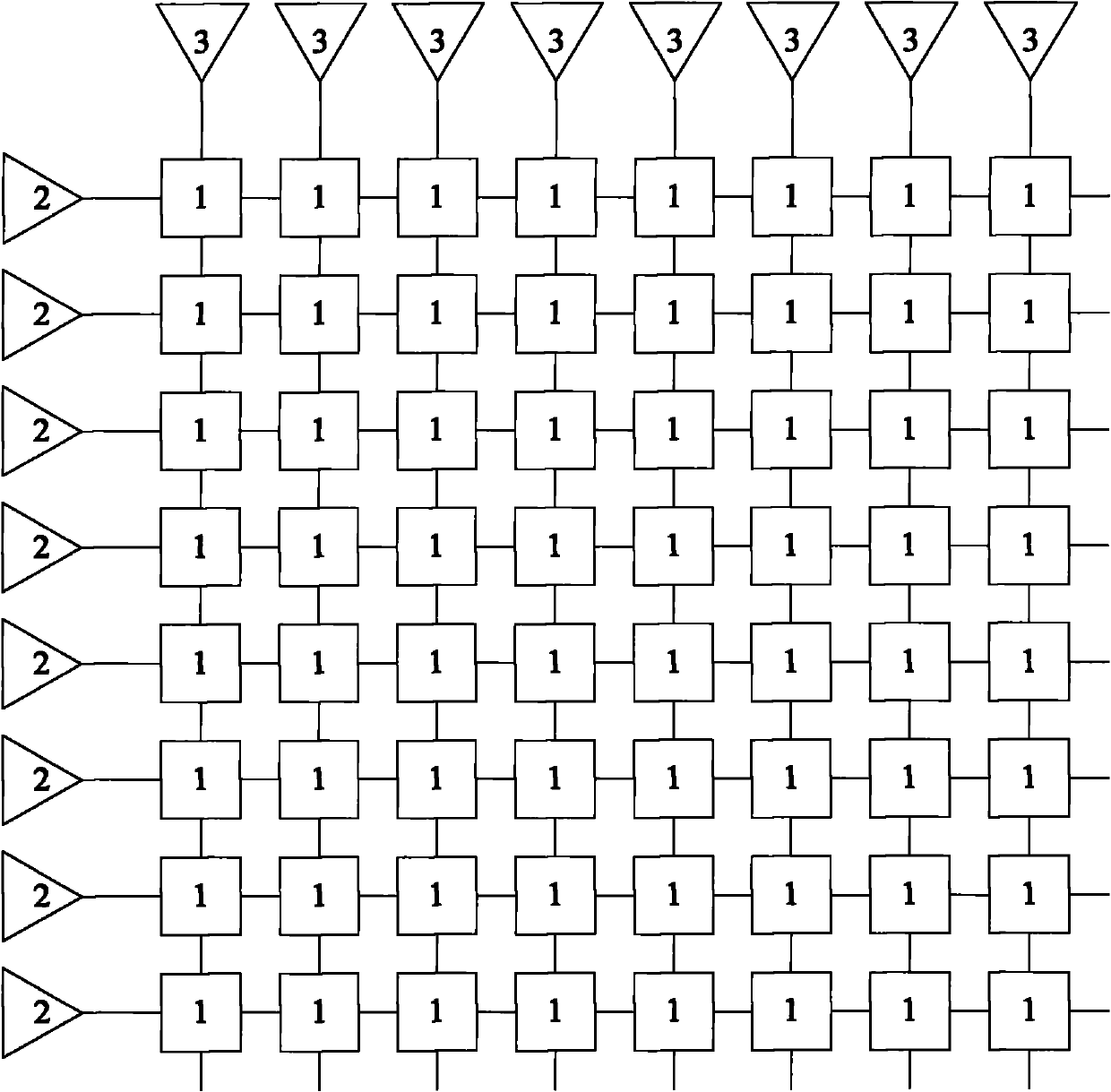

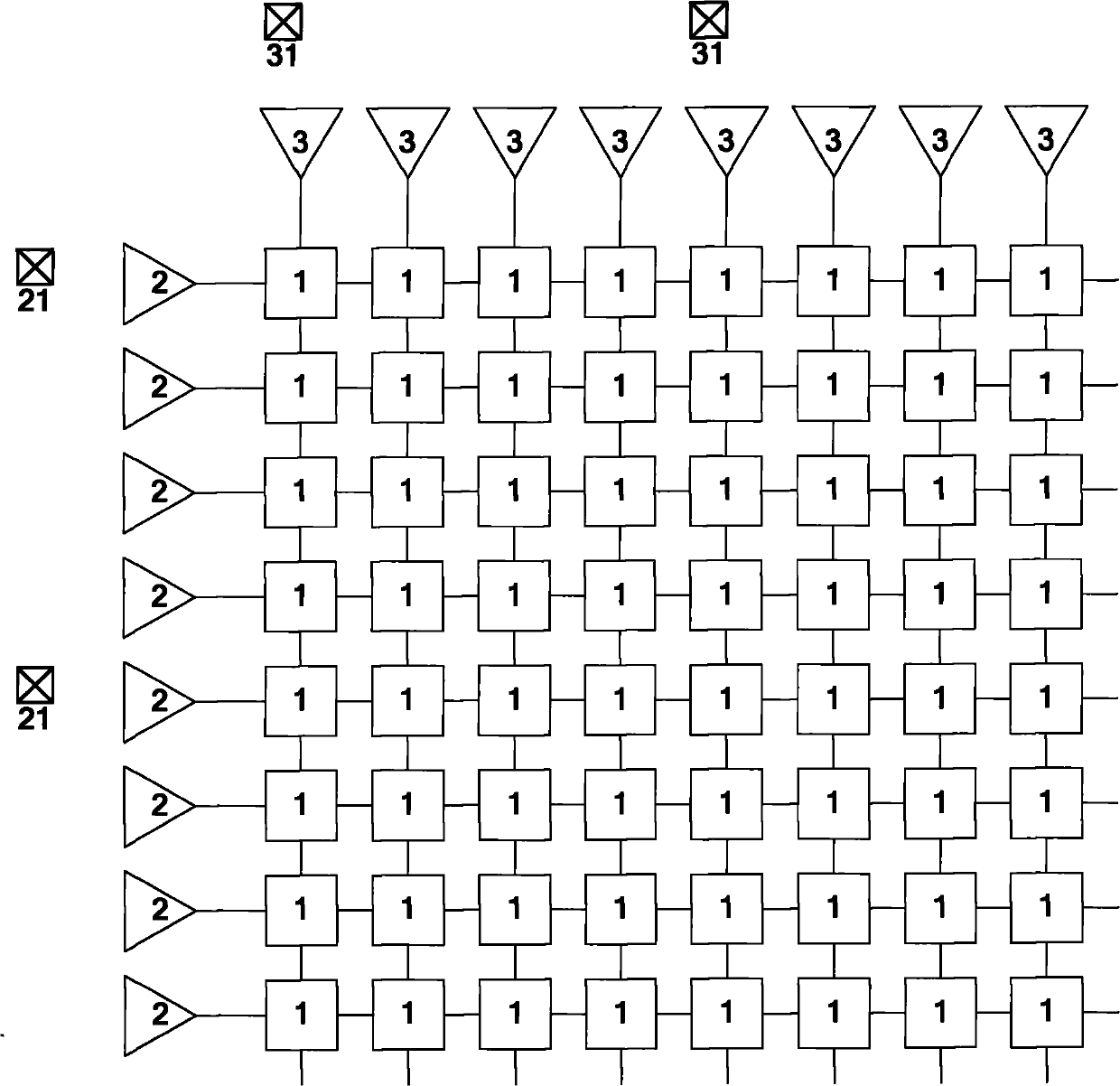

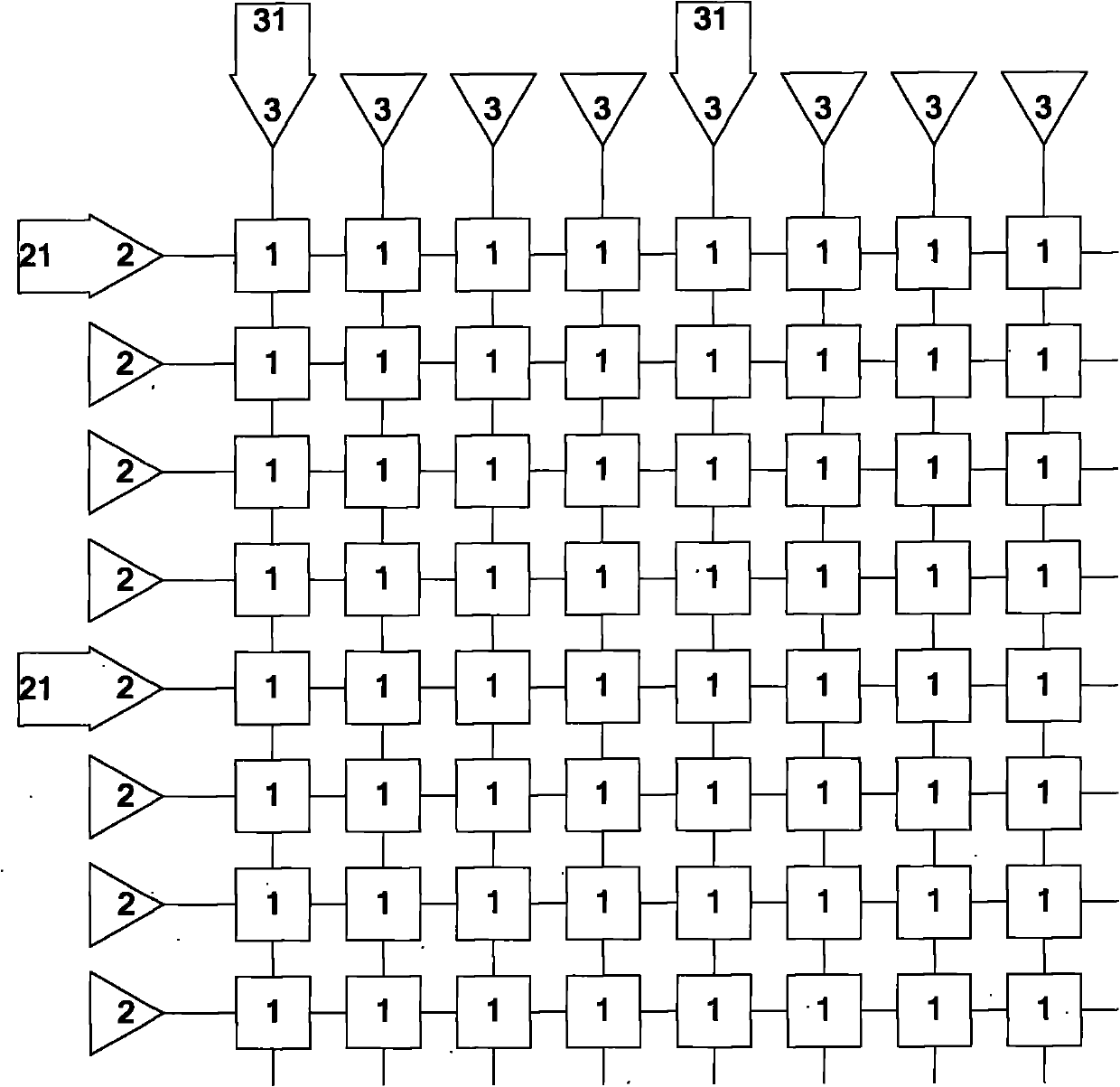

[0014] see figure 2 , which is a schematic diagram of the layout structure of the memory circuit in the present invention. The memory circuit includes a memory array formed by memory cells 1 , a row selection circuit 2 , and a column selection circuit 3 . The innovation of the present invention is that: every equal number of rows, there is a row mark 21 in the open area next to the row of the memory circuit layout; The adjacent clear area has a column marker 31 .

[0015] figure 2 In the middle, a row mark 21 is designed every 4 rows, that is, a row mark 21 is designed in the open area next to the 1st row, the 5th row...; a column mark 31 is designed every 4 columns, that is, it is close to the 1st Column 5... Design column flag 31 for the empty area next to it. The open area refers to a useless area that does not have any impact on the function and use of the circuit. Utilizing these useless areas will not result in an additional increase in the total area of the cir...

PUM

Login to View More

Login to View More Abstract

Description

Claims

Application Information

Login to View More

Login to View More - R&D

- Intellectual Property

- Life Sciences

- Materials

- Tech Scout

- Unparalleled Data Quality

- Higher Quality Content

- 60% Fewer Hallucinations

Browse by: Latest US Patents, China's latest patents, Technical Efficacy Thesaurus, Application Domain, Technology Topic, Popular Technical Reports.

© 2025 PatSnap. All rights reserved.Legal|Privacy policy|Modern Slavery Act Transparency Statement|Sitemap|About US| Contact US: help@patsnap.com