Realization of tile cache strategy in graphics processing unit (GPU) based on tile based rendering

A block rendering and block storage technology, applied in the field of block rendering, can solve the problems of limited performance improvement, increased chip power consumption, etc., and achieve the effects of excellent performance, time saving, and simple logic

- Summary

- Abstract

- Description

- Claims

- Application Information

AI Technical Summary

Problems solved by technology

Method used

Image

Examples

Embodiment Construction

[0009] The present invention will be described in further detail below in conjunction with the accompanying drawings and specific embodiments.

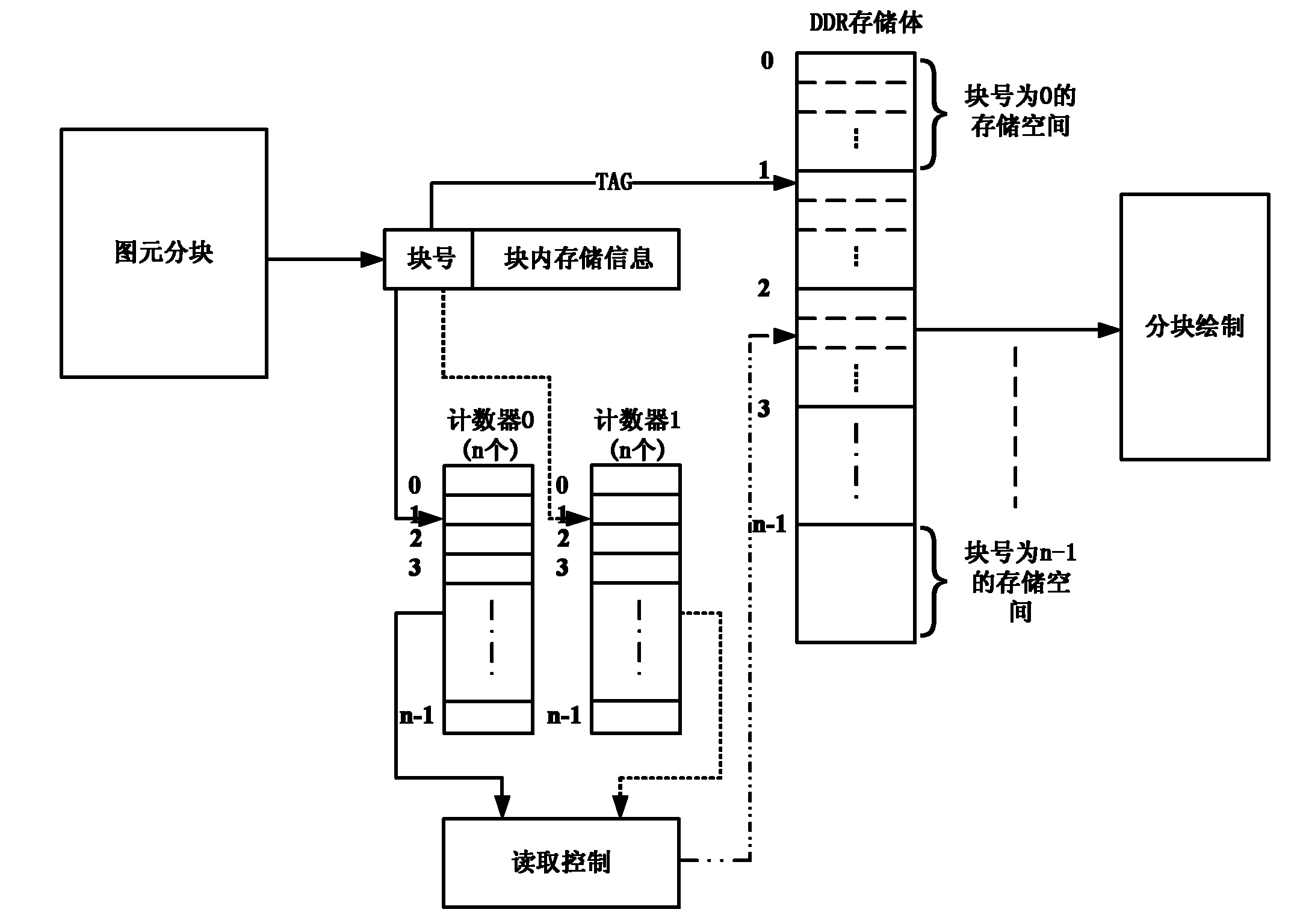

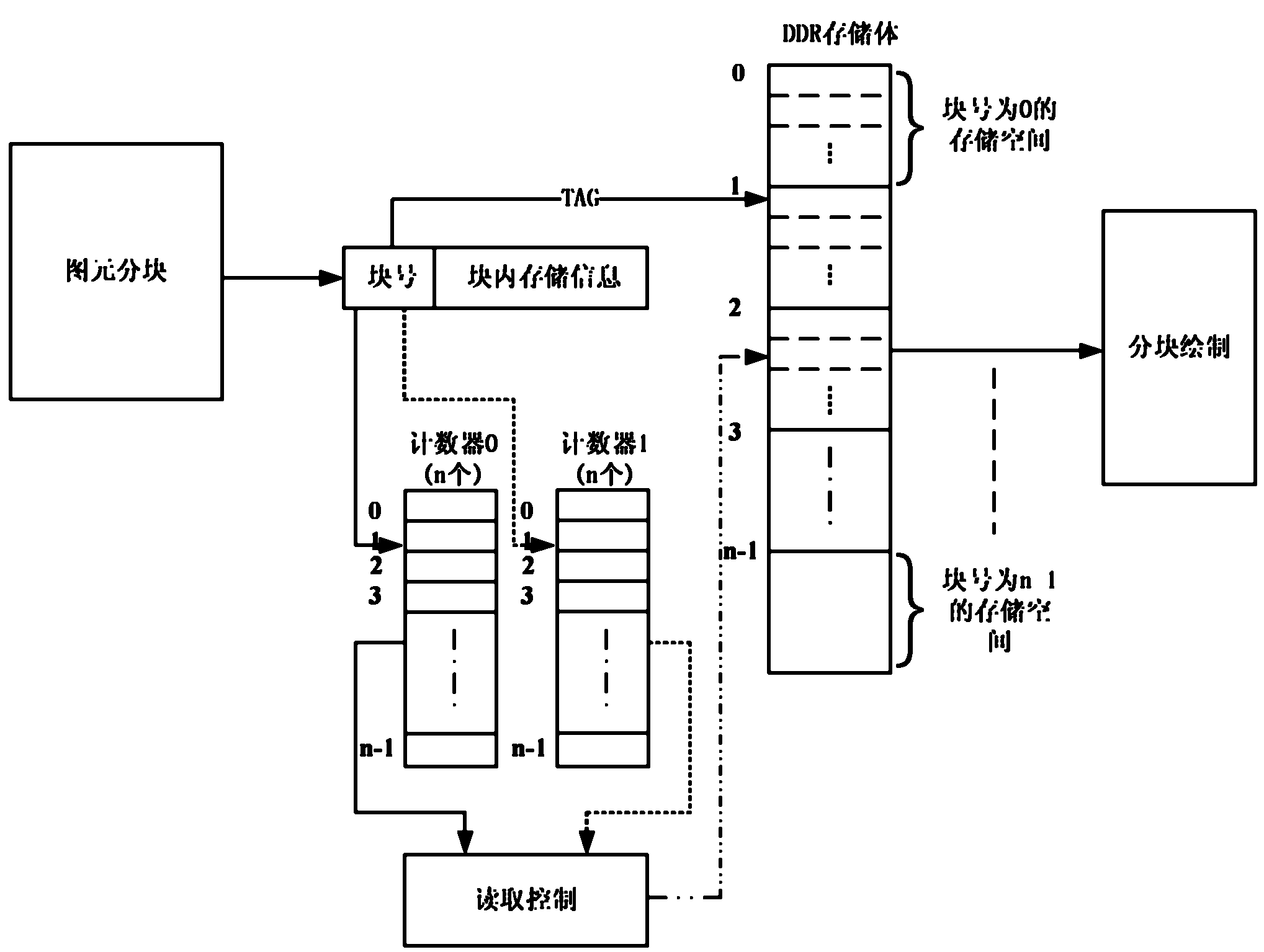

[0010] Such as figure 1 As shown, the implementation of the block storage strategy in the GPU based on block rendering of the present invention includes the determination of the number of blocks that each block contains at most. If the size is a fixed value, the size of the drawing area is different, the number of blocks that can be stored in the storage area is different, and the number of primitives that can be stored in each block is different. According to the block number sent by the primitive in blocks, take out the number of blocks already stored in the current block from the local RAM (internal maintenance counter for each block), if it is the first time to process the block, then the number of blocks is 0 . According to the number of current drawing blocks, the storage space occupied by each block, the current block number ...

PUM

Login to View More

Login to View More Abstract

Description

Claims

Application Information

Login to View More

Login to View More - Generate Ideas

- Intellectual Property

- Life Sciences

- Materials

- Tech Scout

- Unparalleled Data Quality

- Higher Quality Content

- 60% Fewer Hallucinations

Browse by: Latest US Patents, China's latest patents, Technical Efficacy Thesaurus, Application Domain, Technology Topic, Popular Technical Reports.

© 2025 PatSnap. All rights reserved.Legal|Privacy policy|Modern Slavery Act Transparency Statement|Sitemap|About US| Contact US: help@patsnap.com