Multiprocessor system and multiprocessor system interrupt control method

A technology of a multi-processor system and control method, applied in the direction of electrical digital data processing, instruments, etc., can solve the problem of reduced interrupt response ability, and achieve the effect of improving interrupt response ability

- Summary

- Abstract

- Description

- Claims

- Application Information

AI Technical Summary

Problems solved by technology

Method used

Image

Examples

Embodiment 1

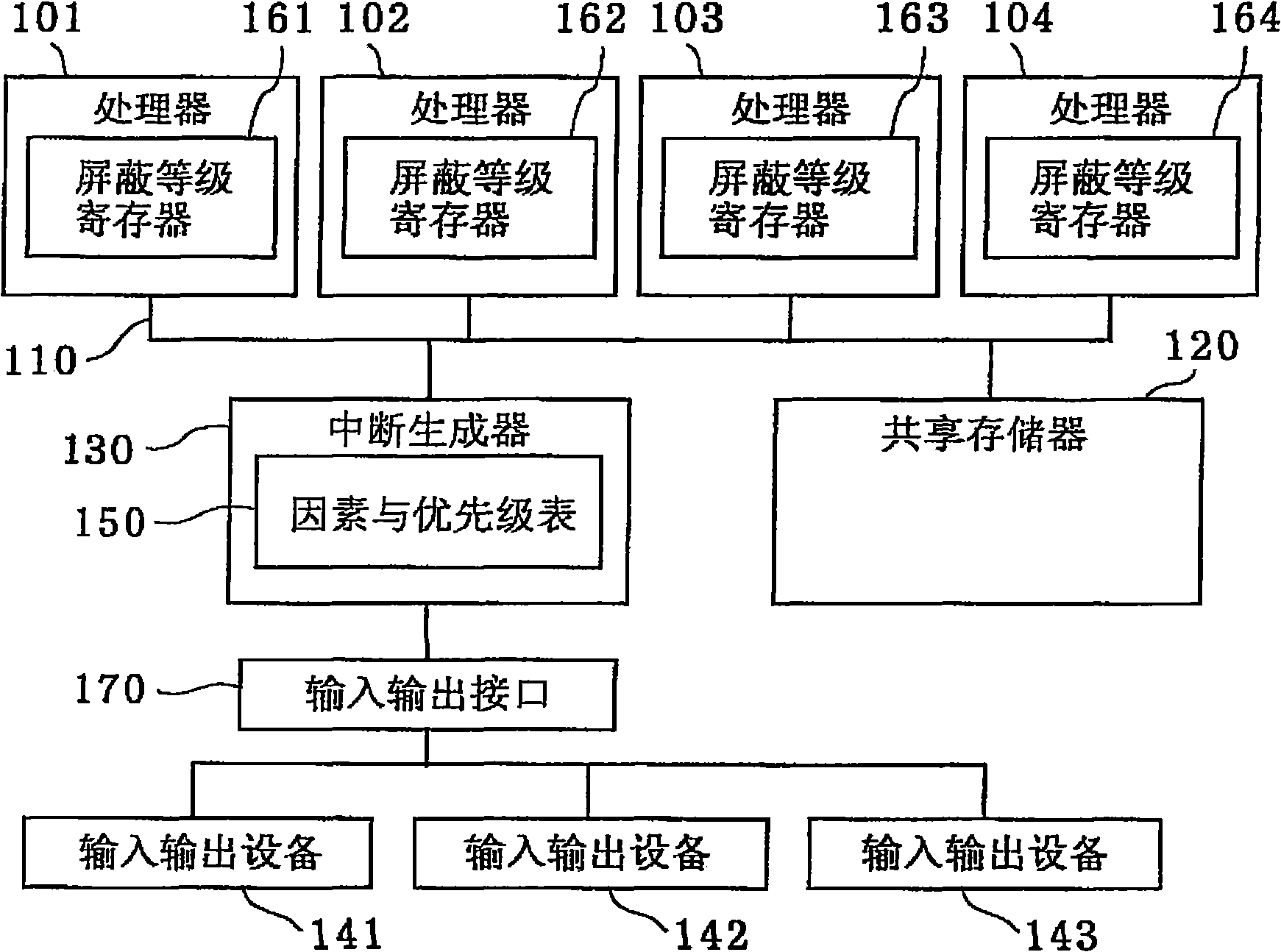

[0070] figure 1 It is a block diagram showing the configuration of the multiprocessor system according to Embodiment 1 of the present invention.

[0071] figure 1 The multiprocessor system shown has: processors 101 , 102 , 103 and 104 ; shared bus 110 ; shared memory 120 ; interrupt generator 130 ; I / O devices 141 , 142 and 143 ;

[0072] The processors 101 , 102 , 103 and 104 are able to communicate with each other via the shared bus 110 . Also, the processors 101 , 102 , 103 and 104 can access the shared memory 120 via the shared bus 110 . Furthermore, the processors 101, 102, 103, and 104 include mask level registers 161, 162, 163, and 164, respectively.

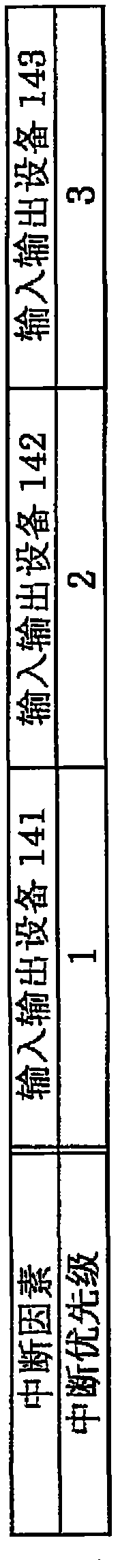

[0073] The interrupt generator 130 has a factor and priority table 150 . Factor and priority table 150 has predefined interrupt priorities for I / O devices 141, 142, and 143, respectively.

[0074] And, the interrupt request of the I / O device 141 , 142 or 143 is notified to the interrupt generator 130 via the I / O in...

Embodiment 2

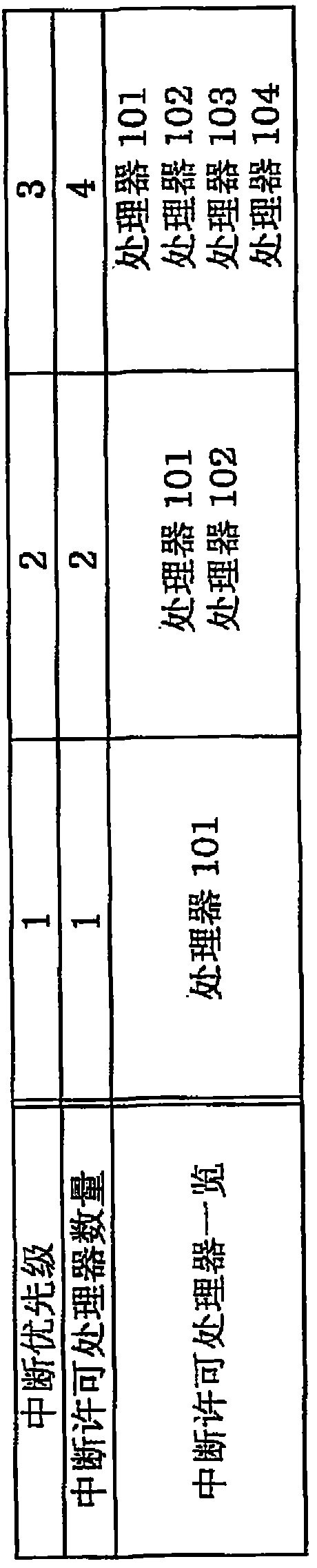

[0101] In the second embodiment, a multiprocessor system in which the allocation of interrupt-permitted processors can be appropriately changed in accordance with the respective interrupt priorities of the I / O devices 141 , 142 , and 143 will be described.

[0102] Figure 7 It is a block diagram showing the configuration of a multiprocessor system according to Embodiment 2 of the present invention. Figure 7 The multiprocessor system shown, with the example 1 of figure 1 Compared with the illustrated multiprocessor system, the difference lies in the configuration of the shared memory 720 , and the difference of the shared memory 720 is that a priority and number of processors table 700 is added. Also for figure 1 The same symbols are assigned to the same elements, and detailed description thereof will be omitted.

[0103] Figure 8 It is a diagram showing the relationship between the interrupt priority and the number of interrupt-permitted processors according to Embodi...

Embodiment 3

[0153] In Embodiment 3, an interrupt control method of such a multiprocessor system is described. On the basis of the interrupt control method of a multiprocessor system in Embodiment 2, the process of selecting and permitting interrupts from all processors is further set. The selection basis of the processor time, so as to achieve the optimization of the whole system.

[0154] In particular, in Embodiment 3, an interrupt control method for a multiprocessor system is described, that is, in an OS (Operating System: processing system) that controls multiple tasks on the multiprocessor system, each processor executes the The task priority of the task is used as a selection basis to effectively execute tasks with high task priority.

[0155] Figure 16 It is a block diagram showing the configuration of a multiprocessor system according to Embodiment 3 of the present invention. Figure 16 The multiprocessor system shown, with the example 2 of Figure 7 Compared with the illustra...

PUM

Login to View More

Login to View More Abstract

Description

Claims

Application Information

Login to View More

Login to View More