Patents

Literature

125 results about "Interrupt priority level" patented technology

Efficacy Topic

Property

Owner

Technical Advancement

Application Domain

Technology Topic

Technology Field Word

Patent Country/Region

Patent Type

Patent Status

Application Year

Inventor

The interrupt priority level (IPL) is a part of the current system interrupt state, which indicates the interrupt requests that will currently be accepted.

Priority bearers in a mobile telecommunication network

ActiveUS8300575B2Predictable Quality of ServiceNetwork traffic/resource managementWireless network protocolsTelecommunications networkNetwork packet

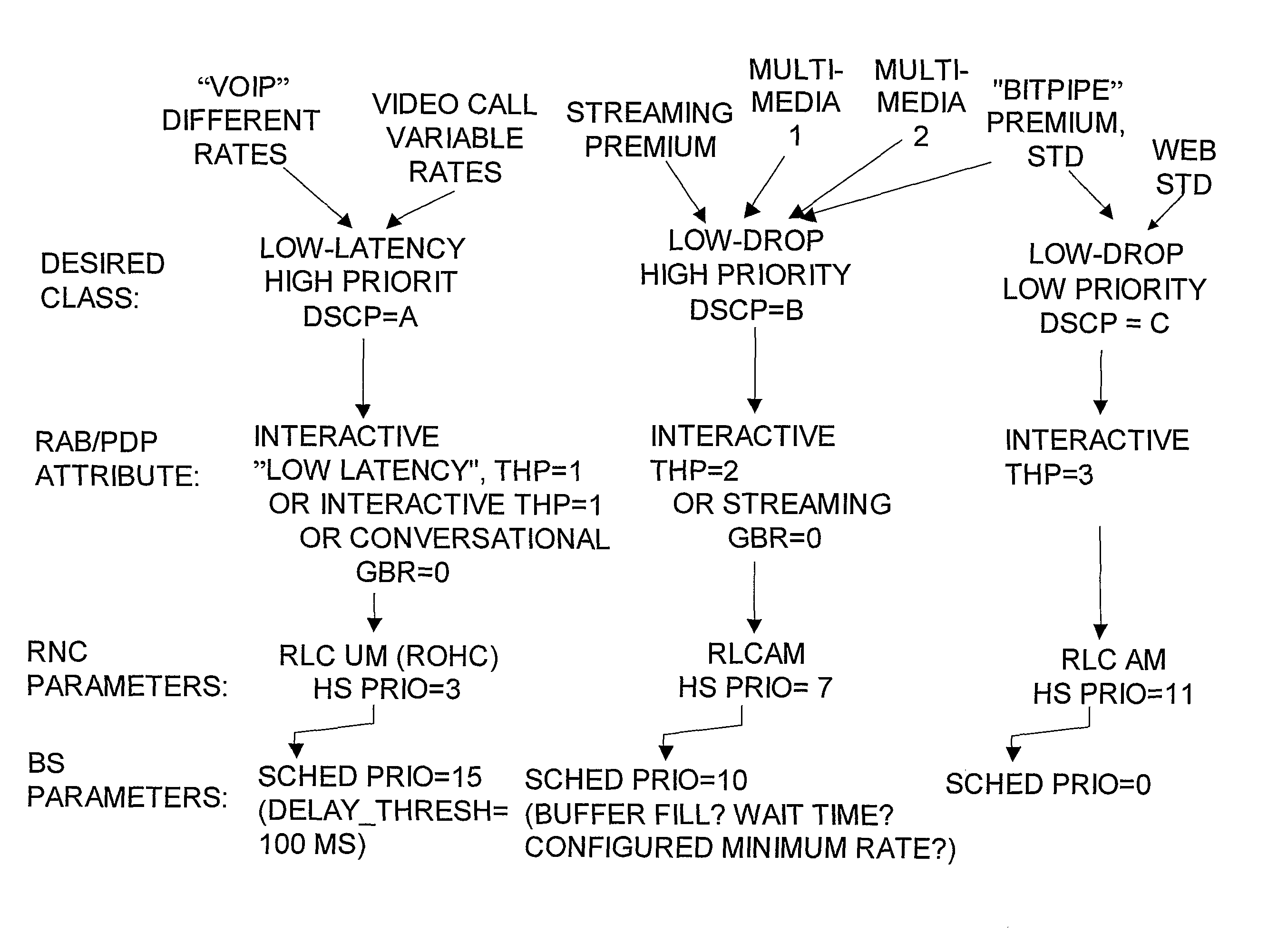

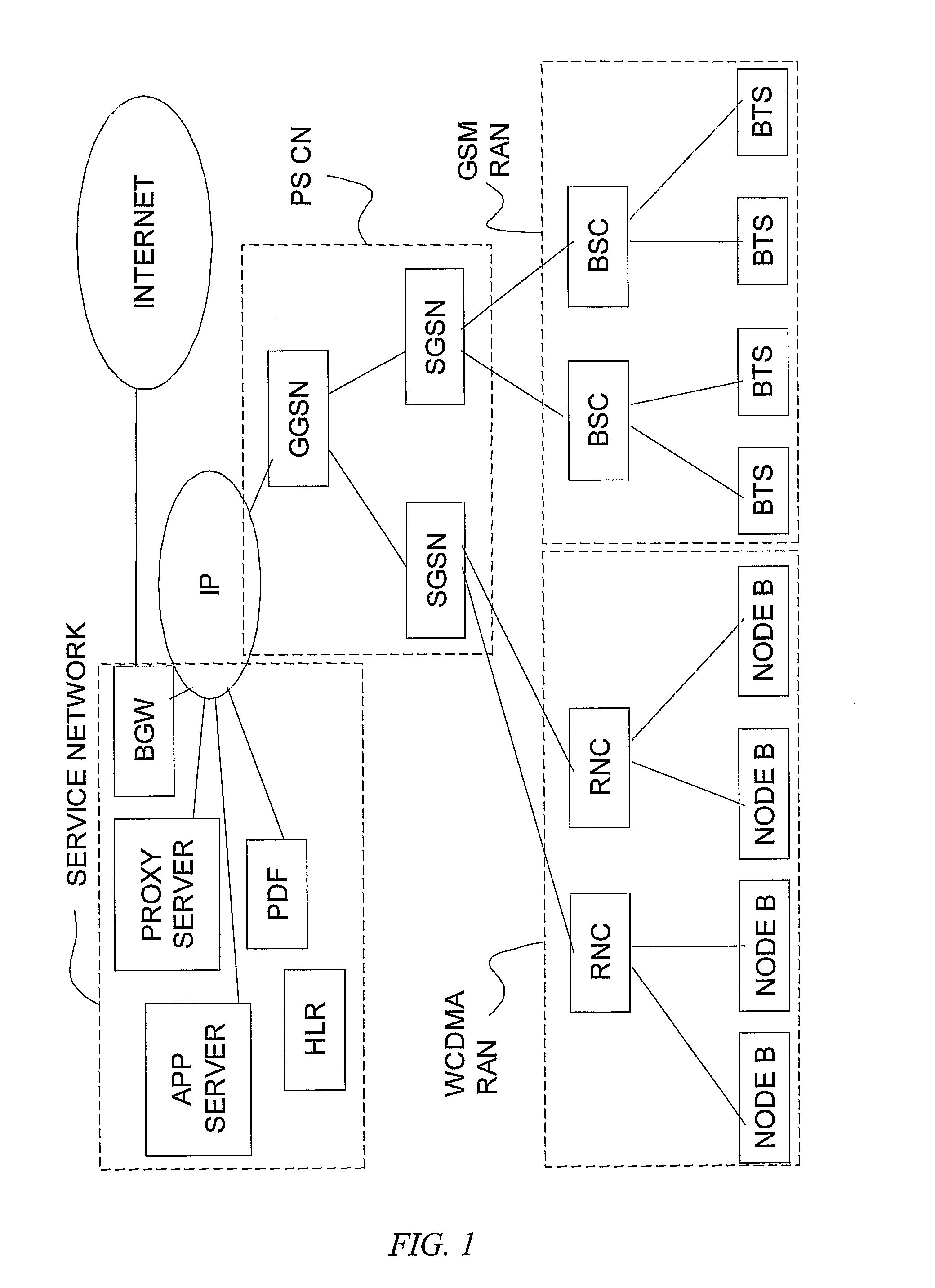

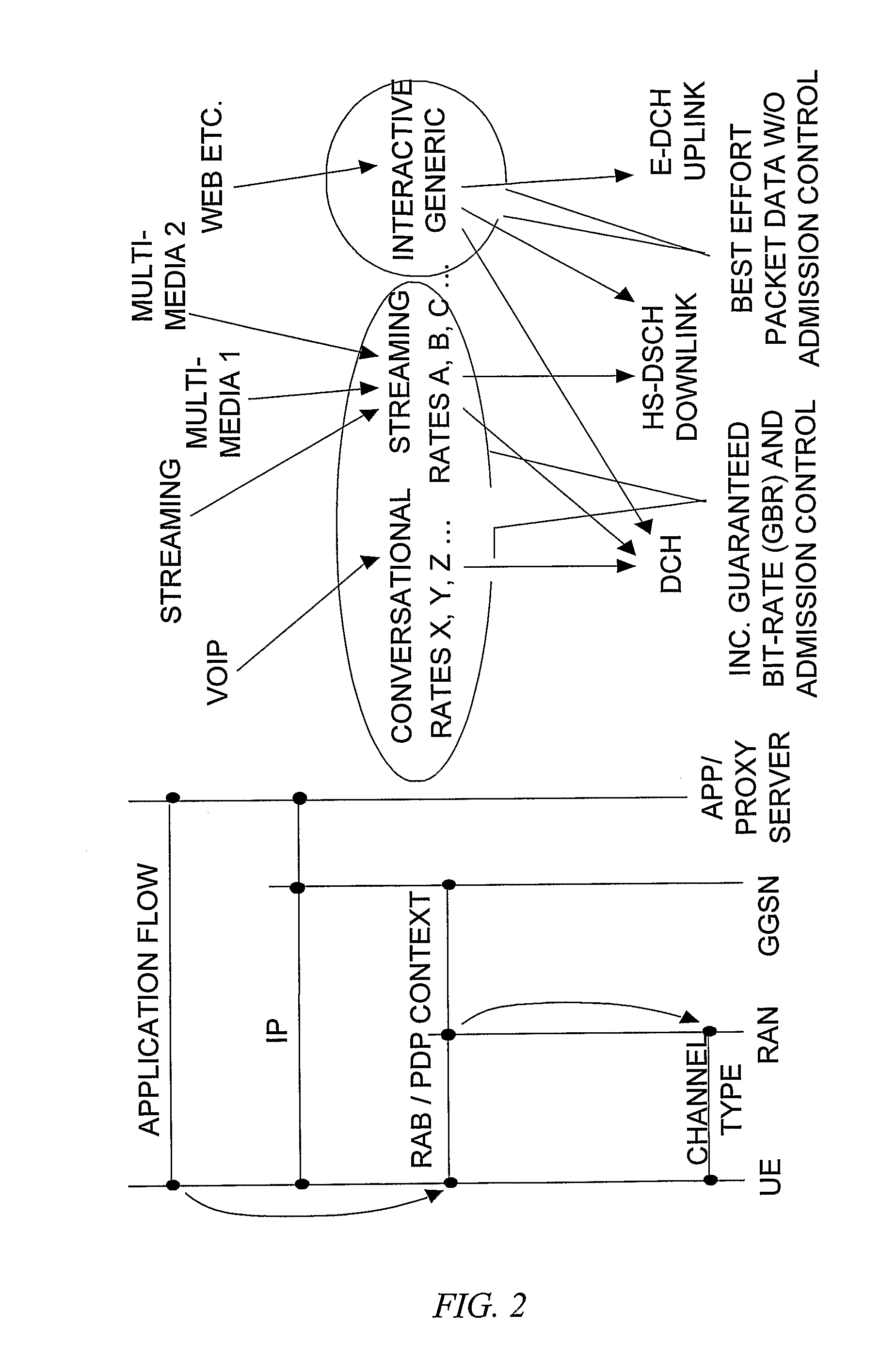

Method for switching a packet to a bearer in a mobile telecommunication network, by setting up multiple parallel bearers for bearing the packet across a radio interface; associating the bearers with a bearer priority level of traffic handling; determining a priority level of the packet; mapping the packet priority level to the bearer priority level; switching the packet to one of the bearers based on the mapping; using the bearer priority level to prioritize the access to the radio resources. A further method for switching a packet by setting up multiple parallel bearers without resource reservation; associating each of the bearers with a bearer priority level; mapping a flow of packets to one of the bearer priority levels, when a service is started; switching each packet to one of the multiple bearers based on the mapping; using the bearer priority level to prioritize the access to the radio resources.

Owner:TELEFON AB LM ERICSSON (PUBL)

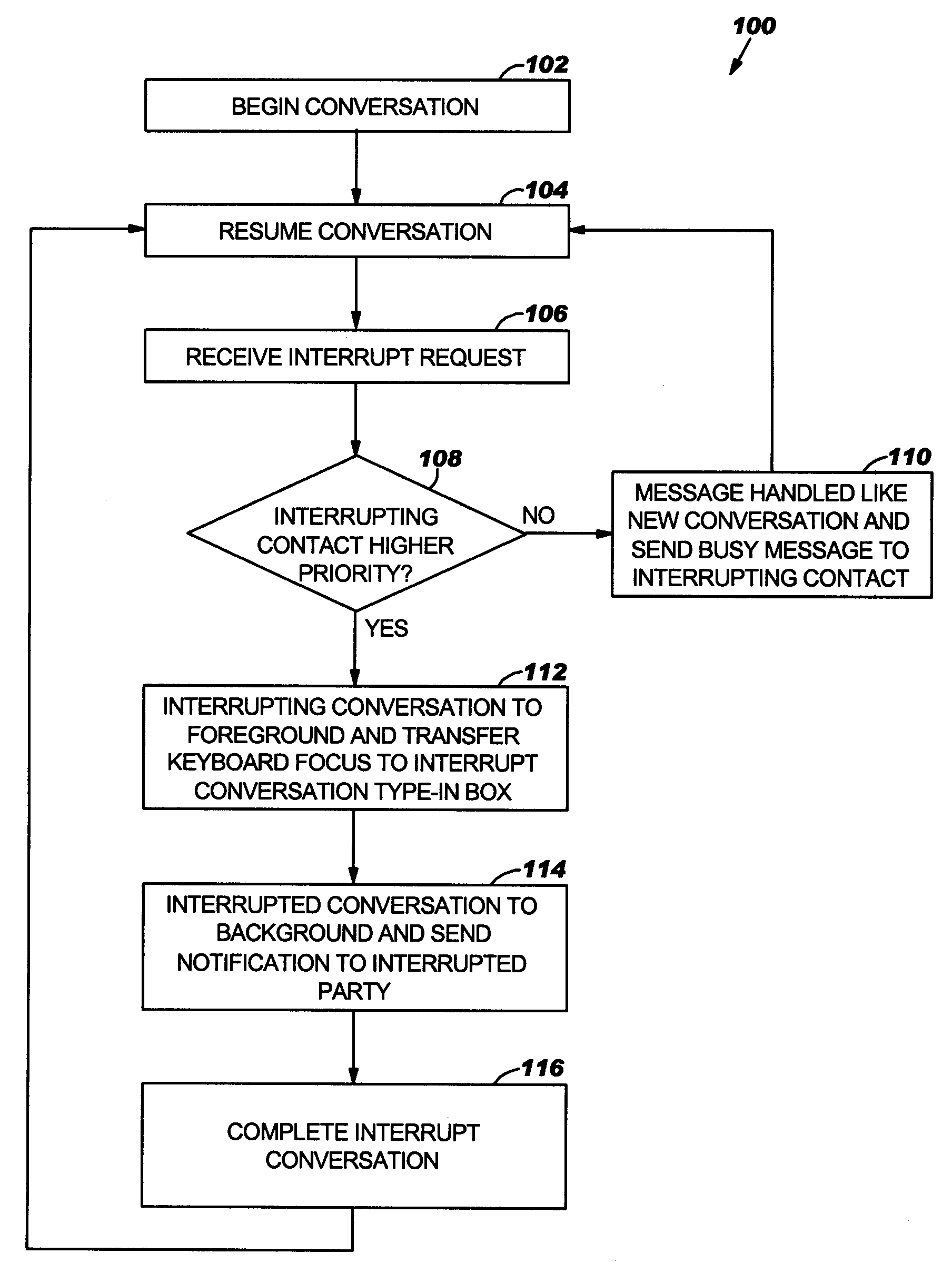

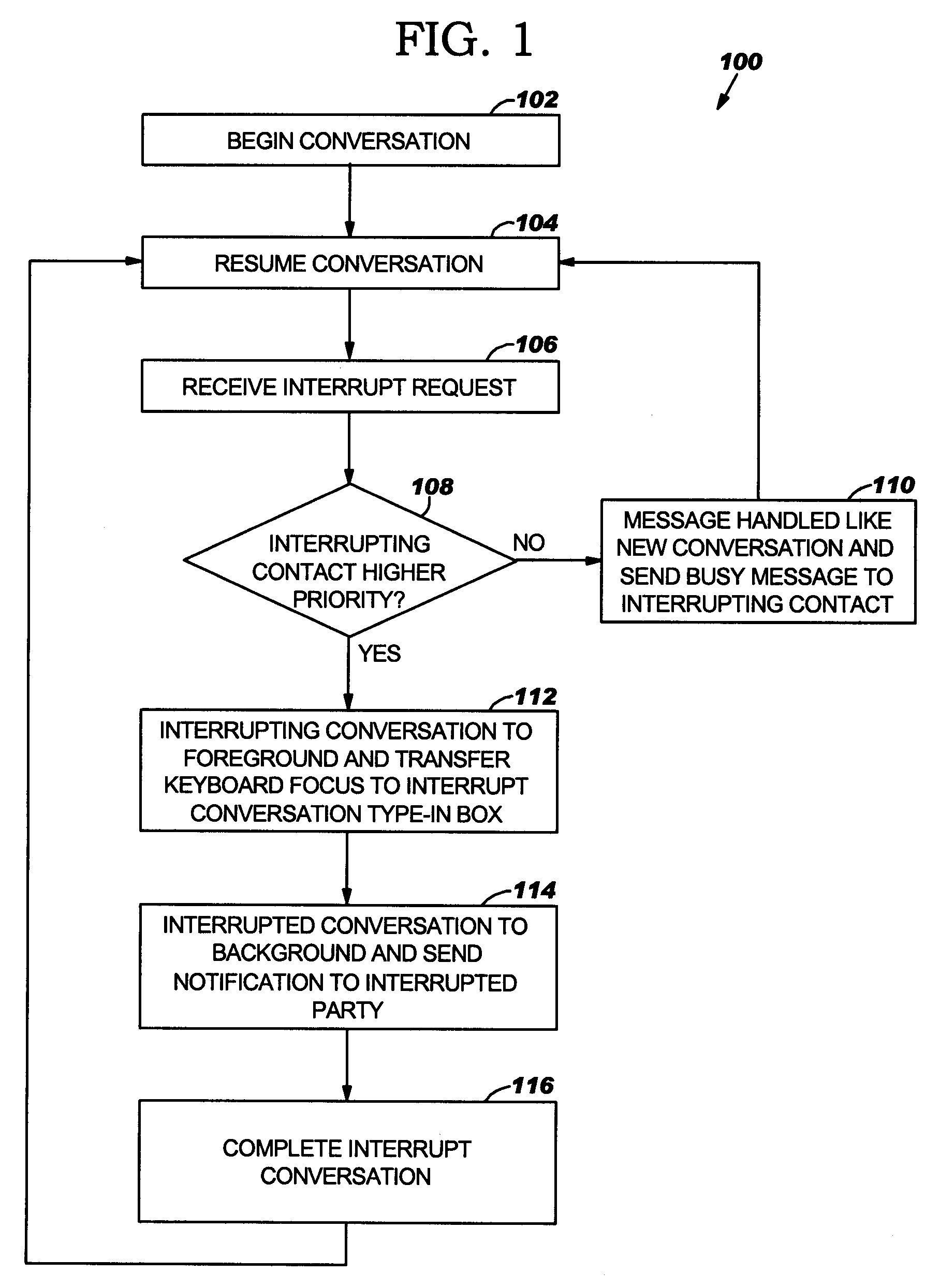

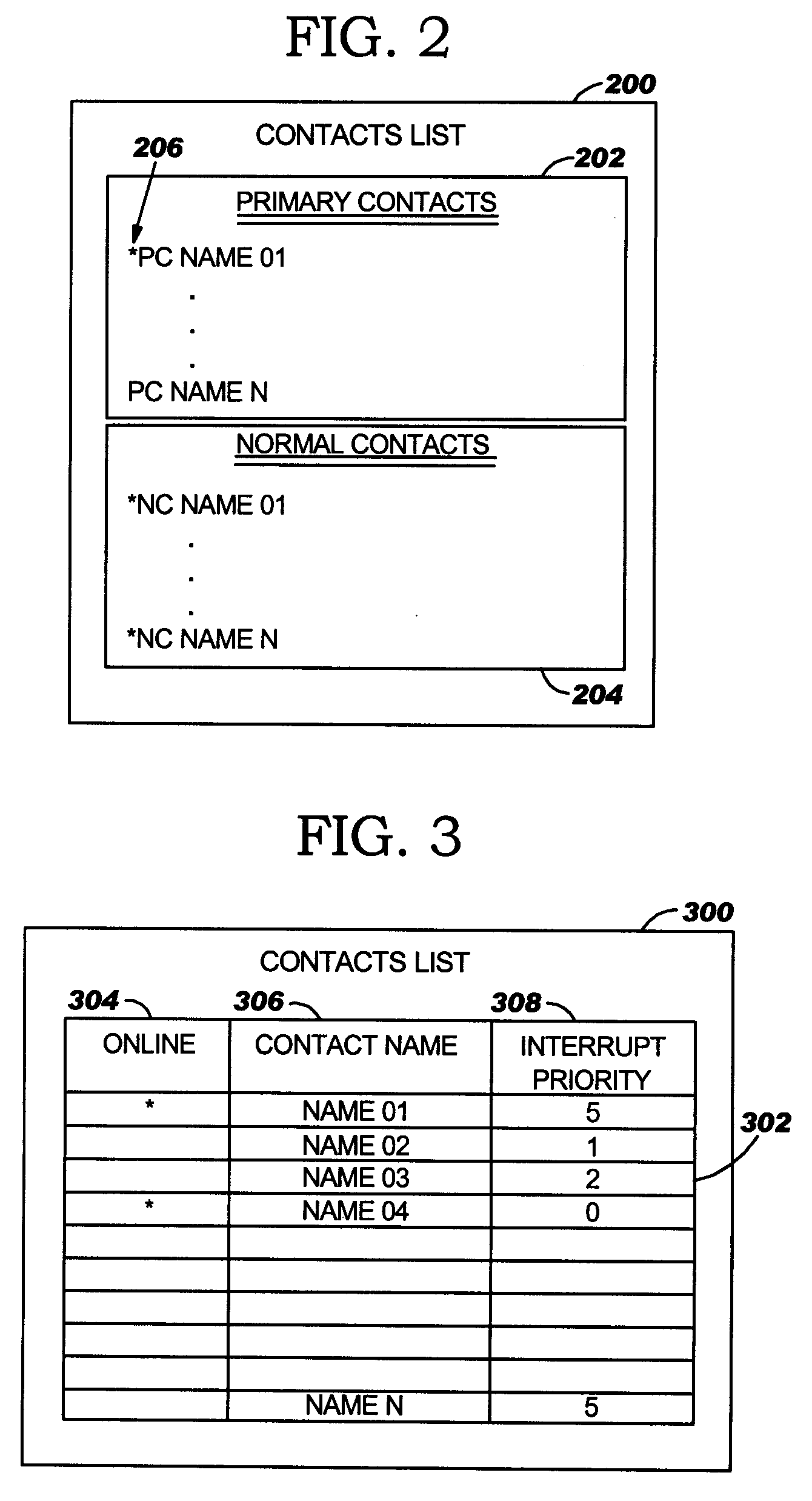

Method and system for managing interrupts in an instant messaging application

A method for managing interrupts in an instant messaging application may include receiving an interrupt request from an interrupting contact during an instant messaging conversation between at least two contacts. The method may also include interrupting the instant messaging conversation in response to a predetermined one of the interrupting contact having a selected interrupt priority ranking relative to an interrupt priority ranking of each of the at least two contacts or an interrupting conversation having a higher interrupt priority ranking compared to an interrupt priority ranking of the instant messaging conversation.

Owner:SNAP INC

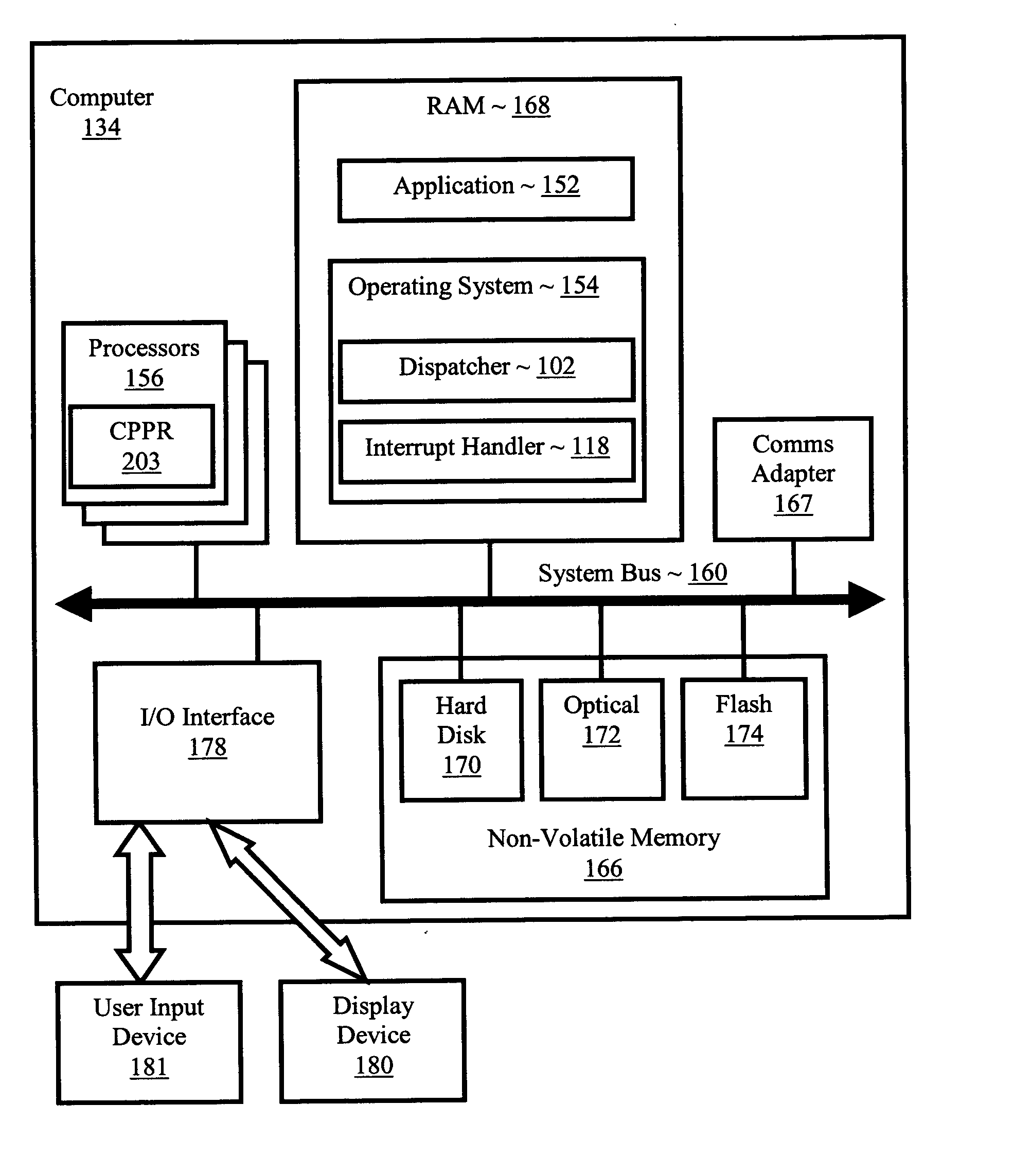

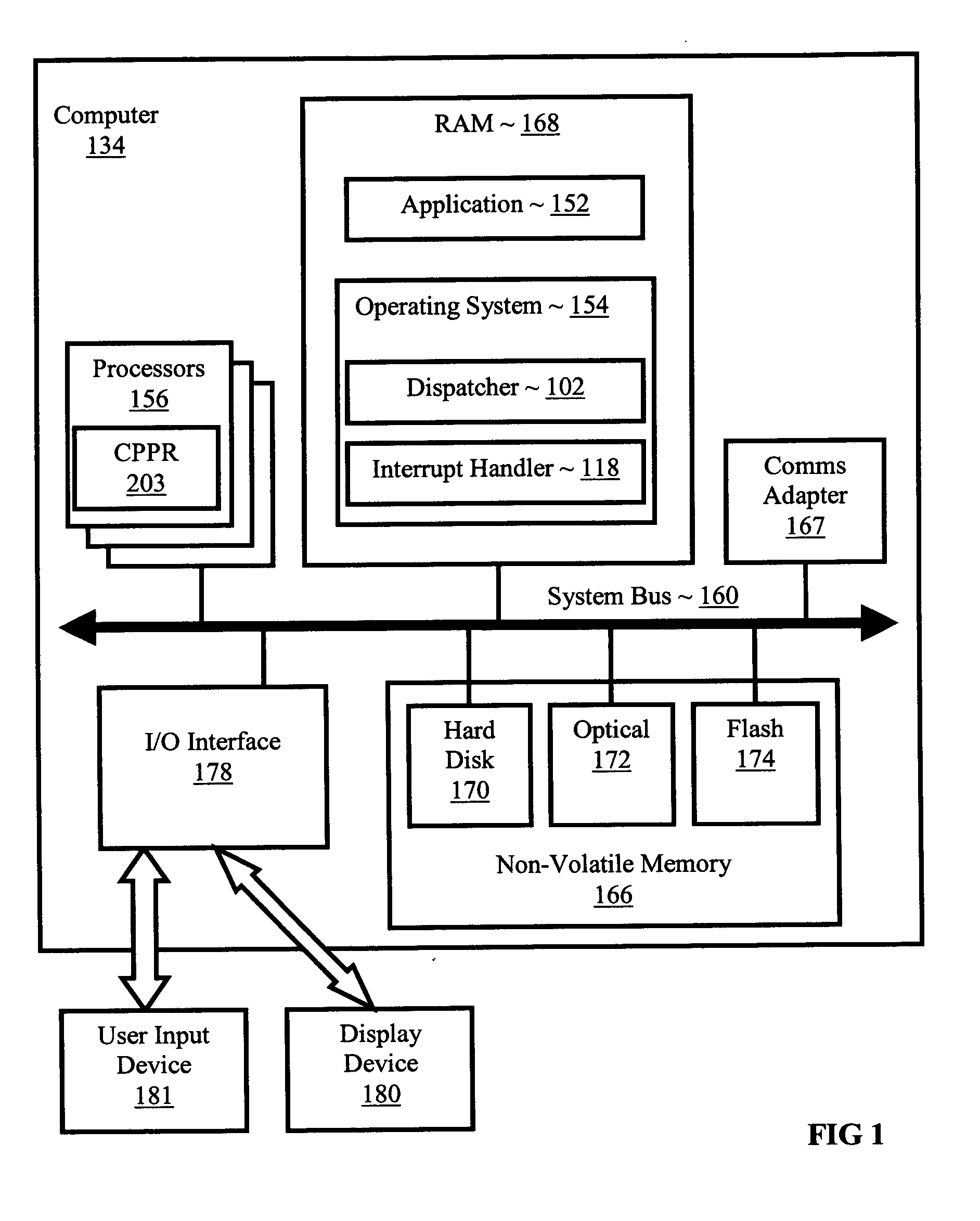

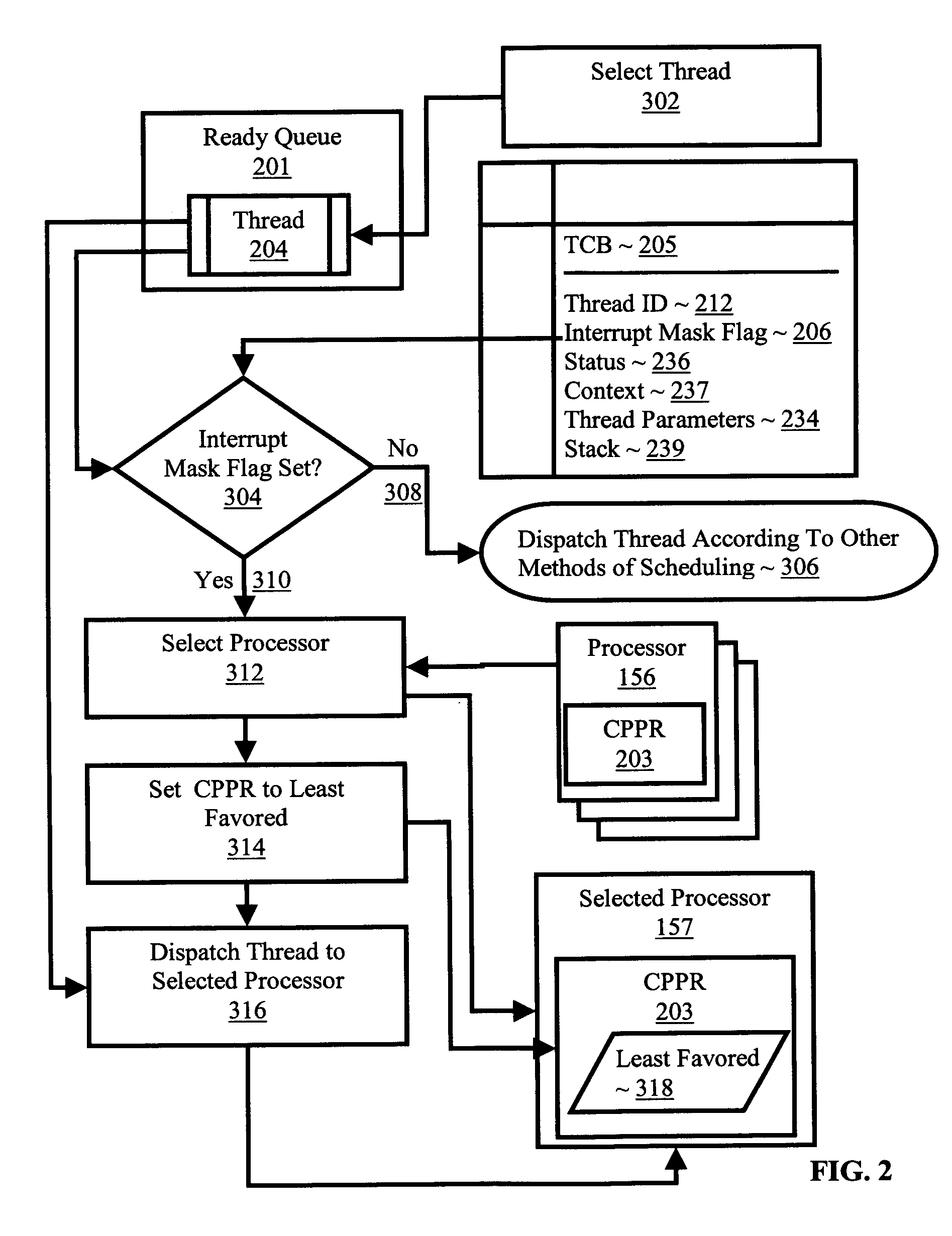

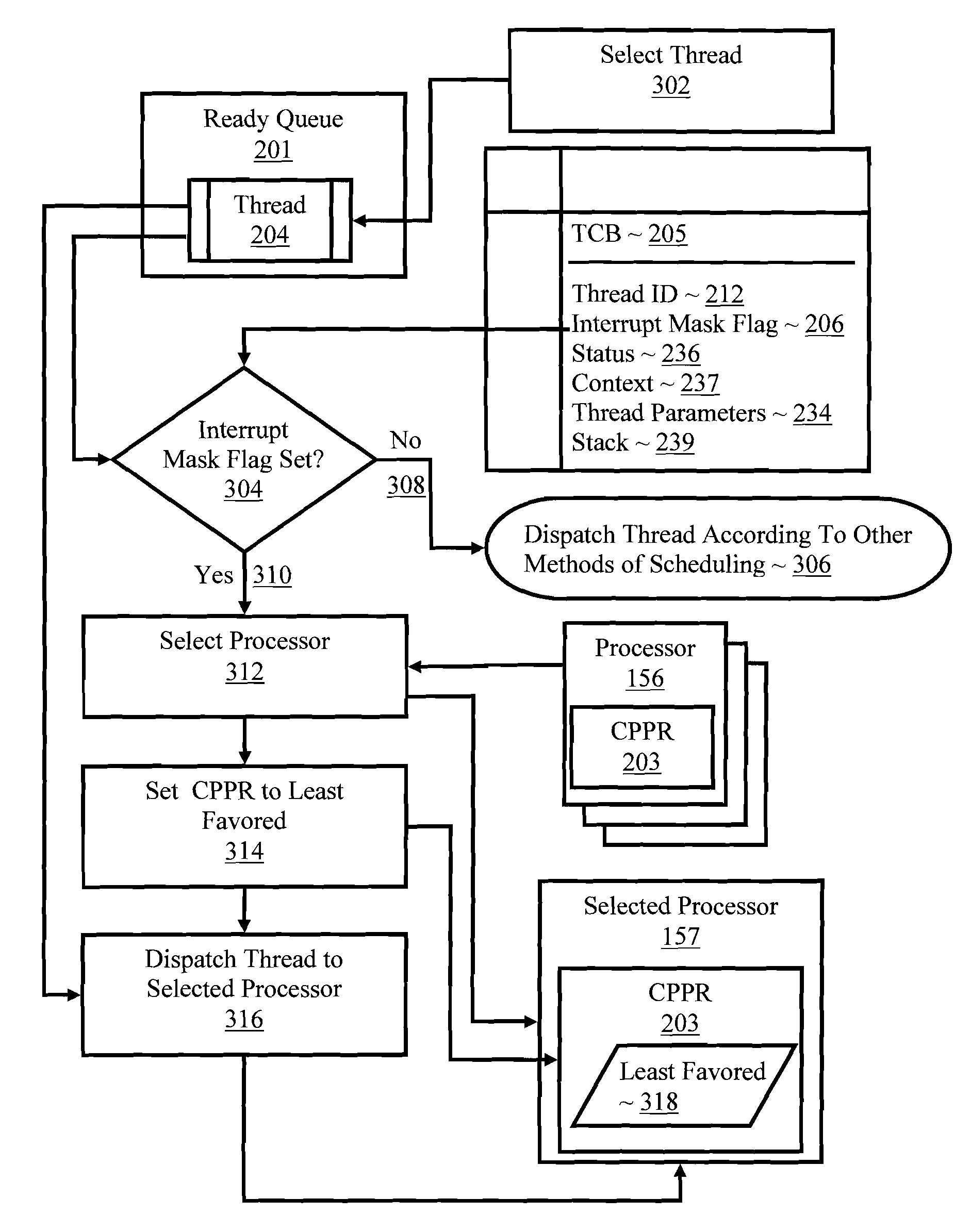

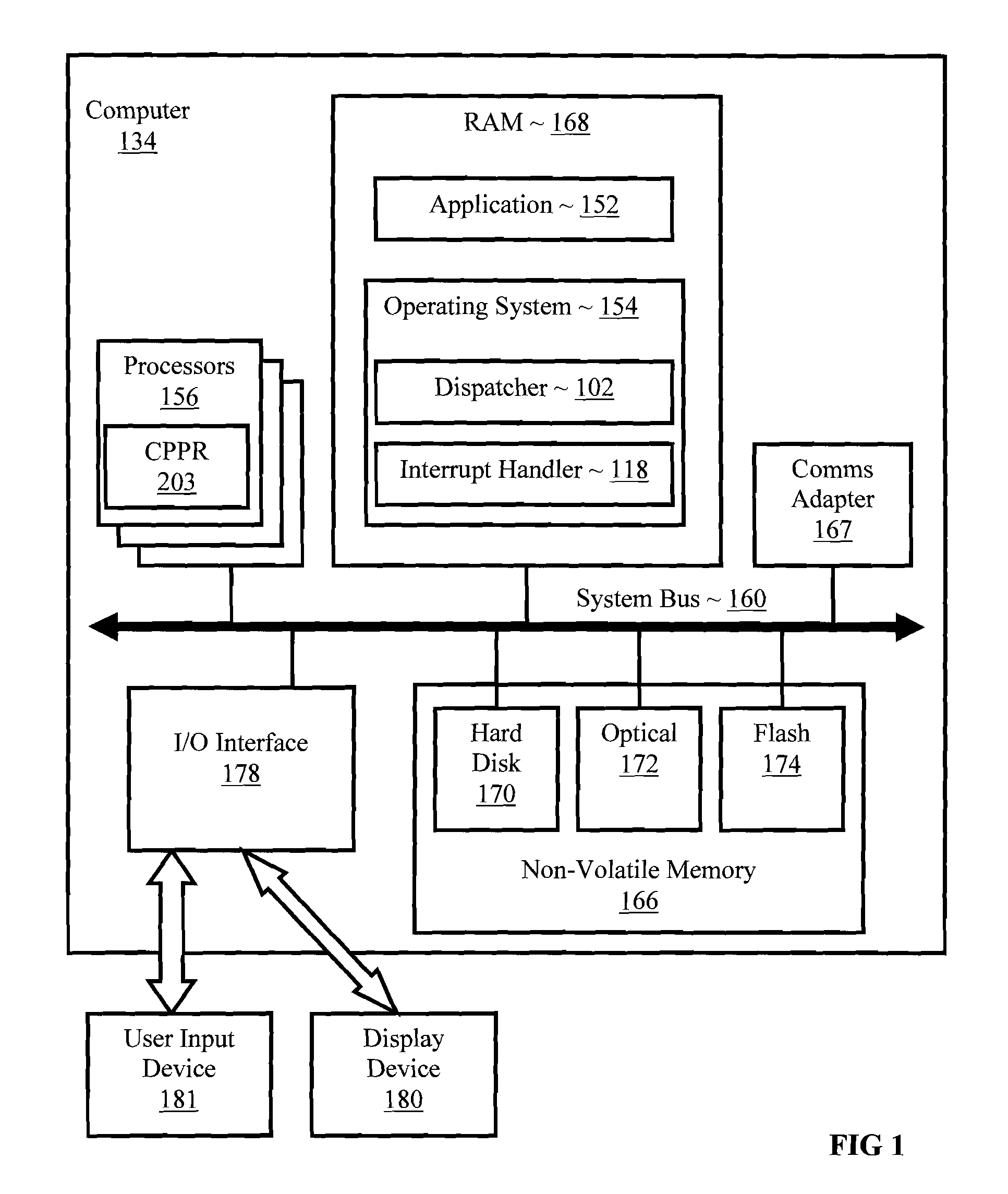

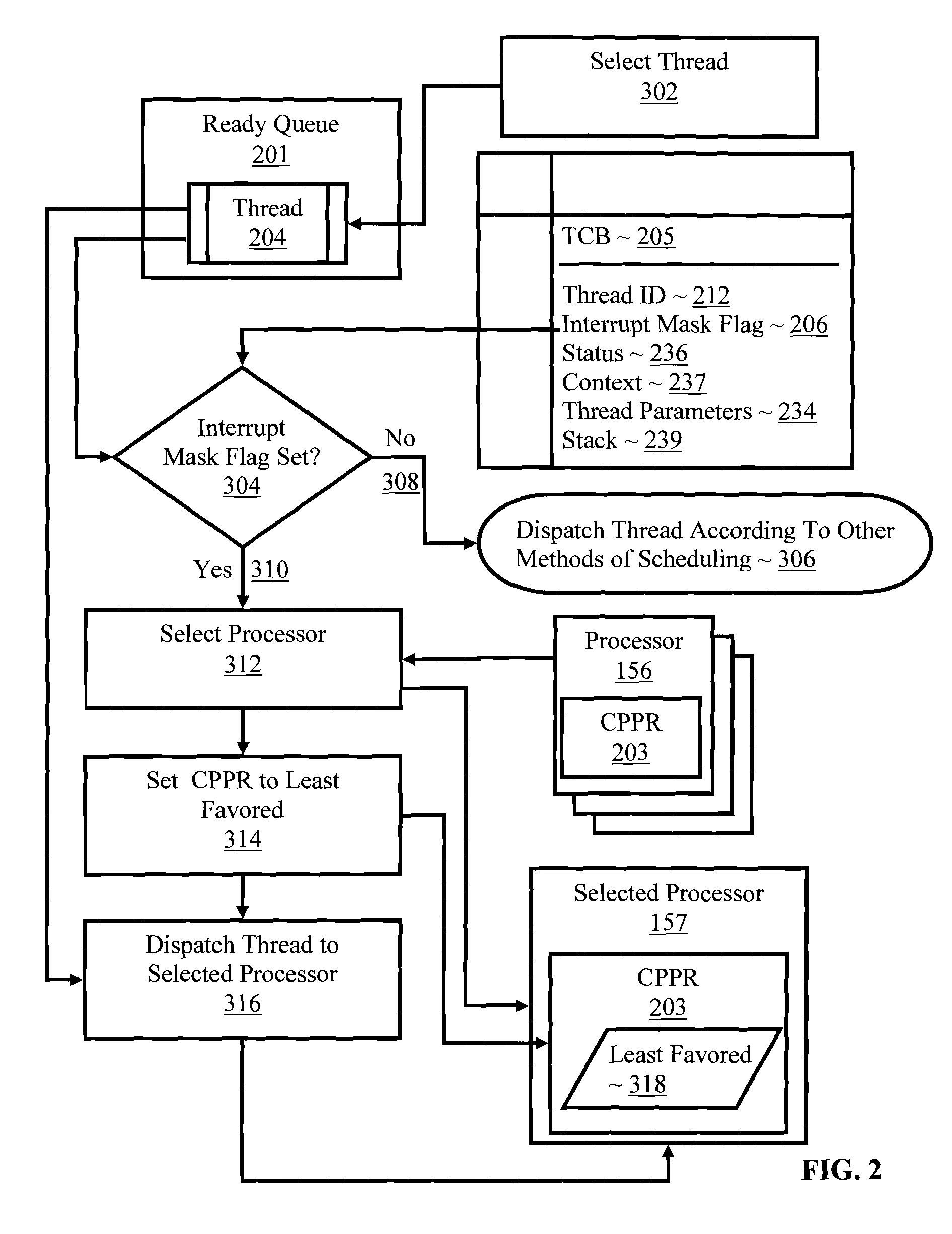

Scheduling threads in a multiprocessor computer

Methods, systems, and computer program products are provided for scheduling threads in a multiprocessor computer. Embodiments include selecting a thread in a ready queue to be dispatched to a processor and determining whether an interrupt mask flag is set in a thread control block associated with the thread. If the interrupt mask flag is set in the thread control block associated with the thread, embodiments typically include selecting a processor, setting a current processor priority register of the selected processor to least favored, and dispatching the thread from the ready queue to the selected processor. In some embodiments, setting the current processor priority register of the selected processor to least favored is carried out by storing a value associated with the highest interrupt priority in the current processor priority register.

Owner:IBM CORP

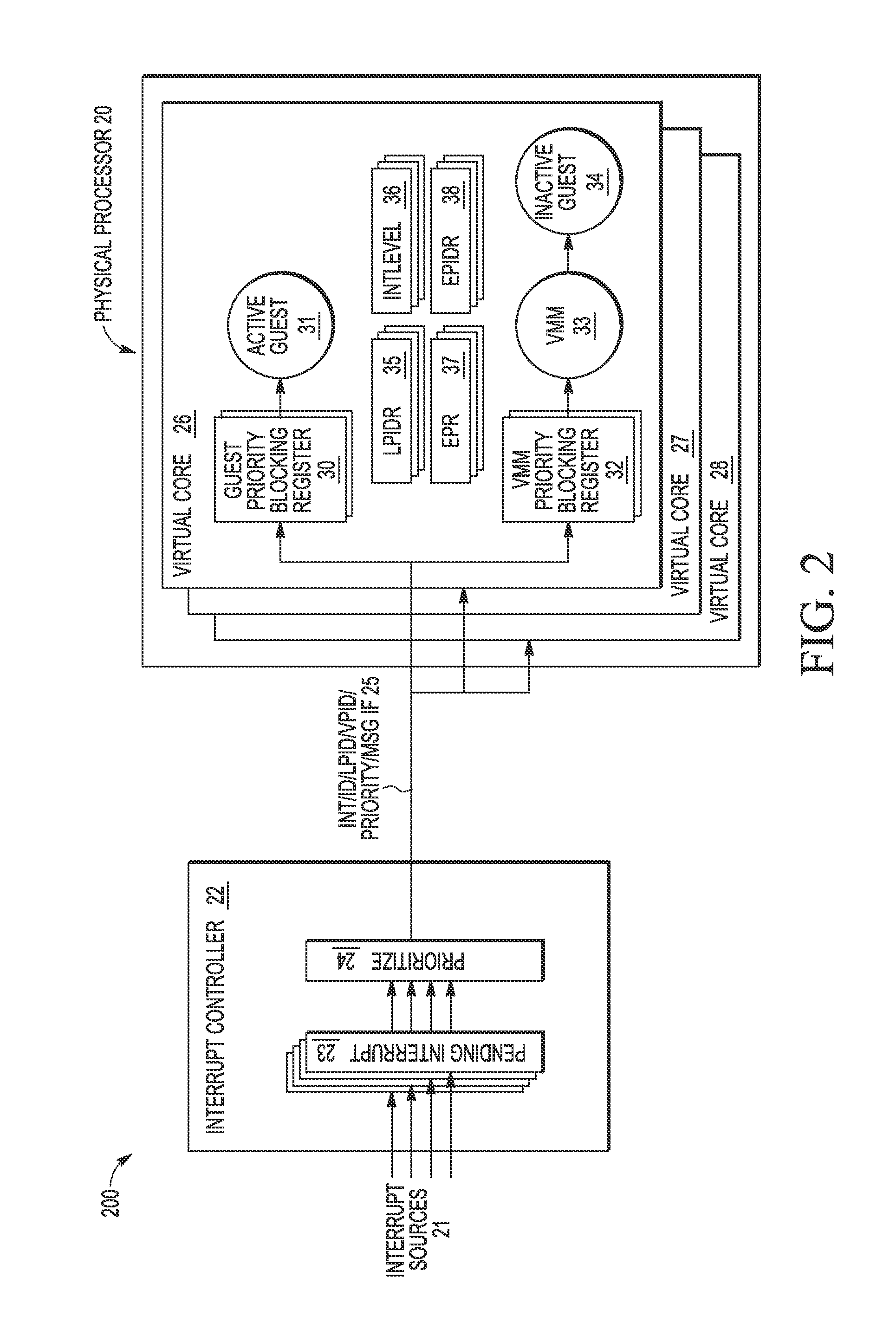

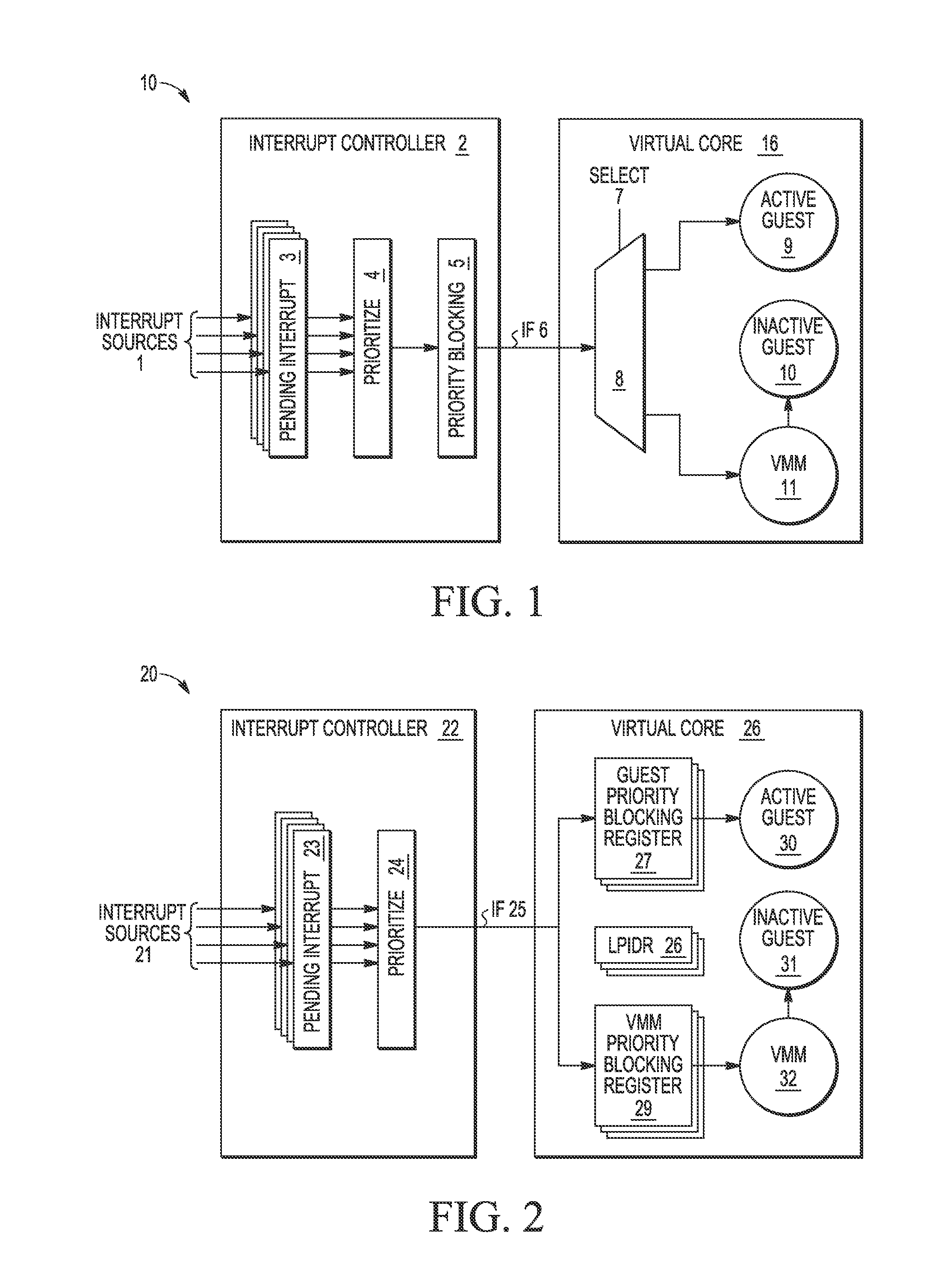

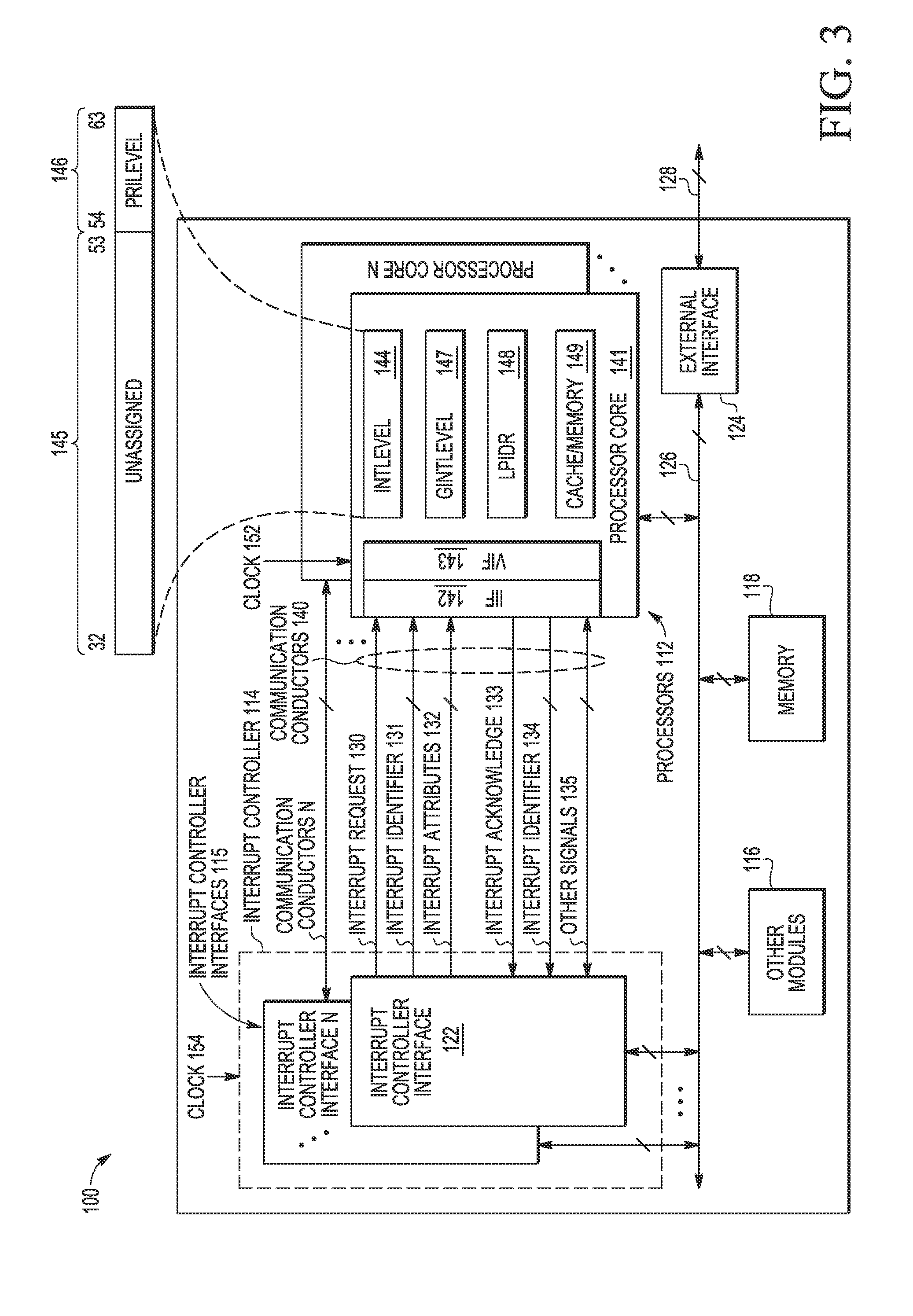

Processor Interrupt Interface with Interrupt Partitioning and Virtualization Enhancements

A method and circuit for a data processing system (200) provide a processor-based partitioned priority blocking mechanism by storing interrupt identifiers, partition identifiers, thread identifiers, and priority levels associated with accepted interrupt requests in special purpose registers (35-38) located at the processor core (26) to enable quick and efficient interrupt priority blocking on a partition basis.

Owner:NXP USA INC

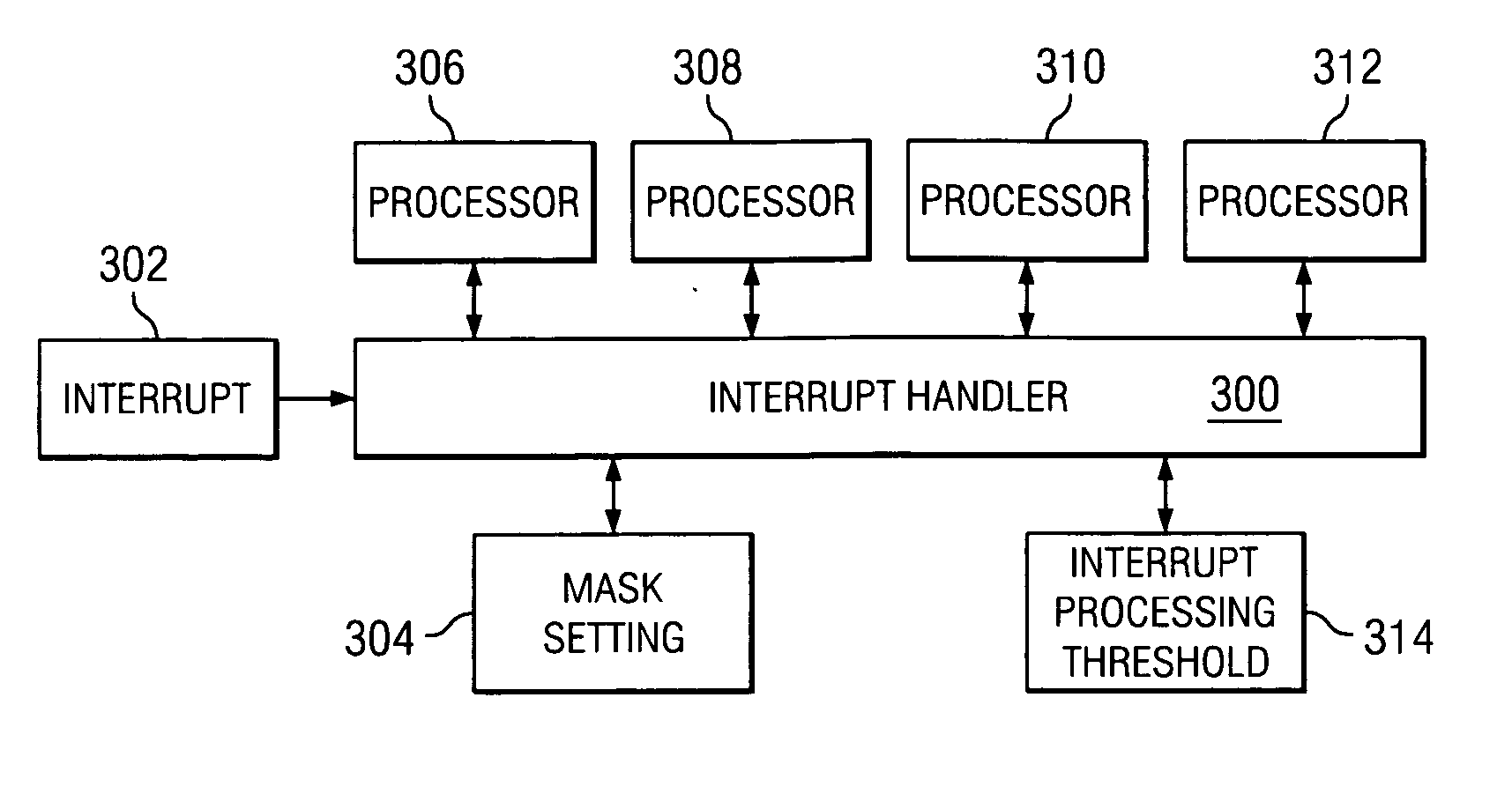

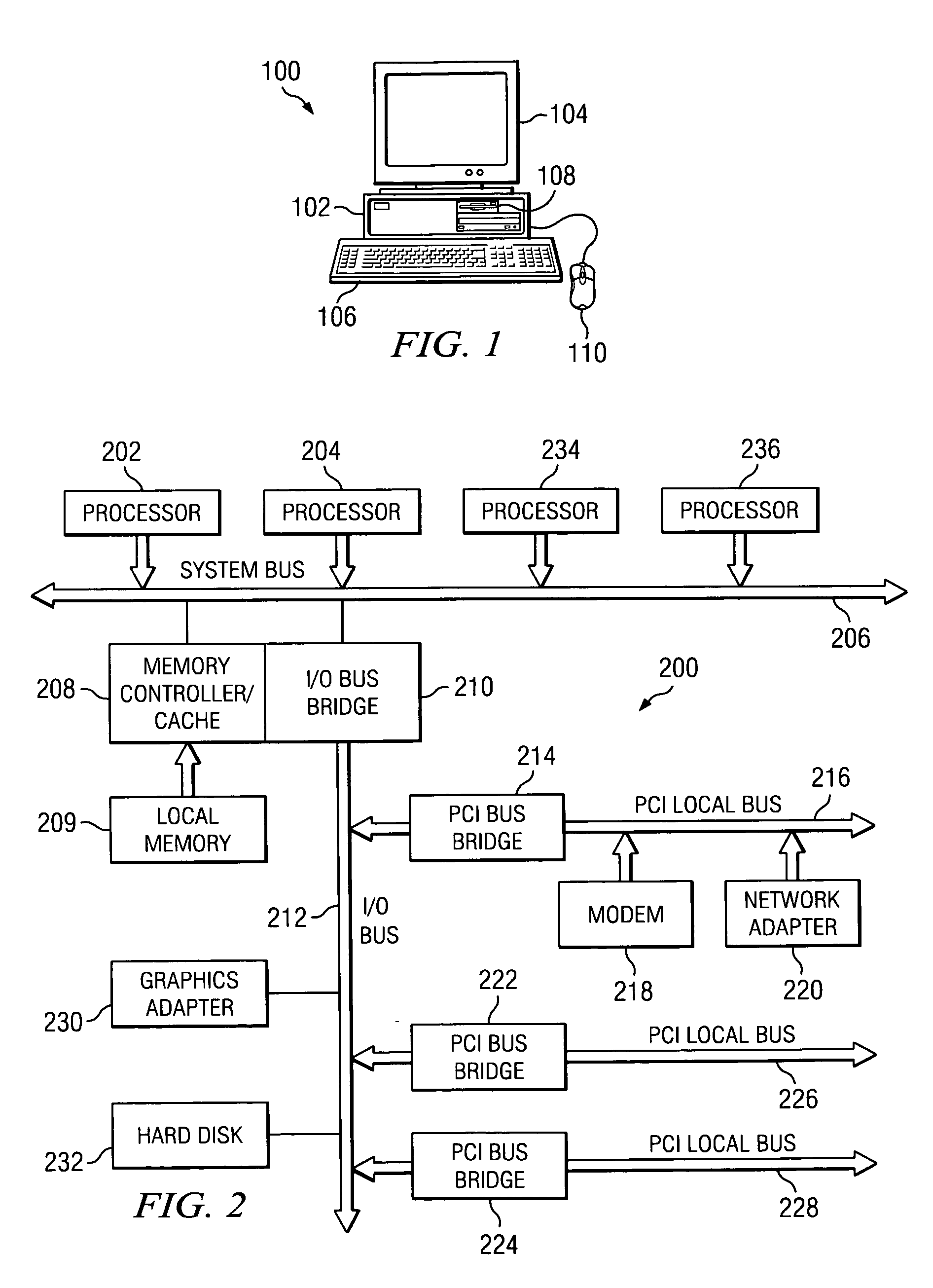

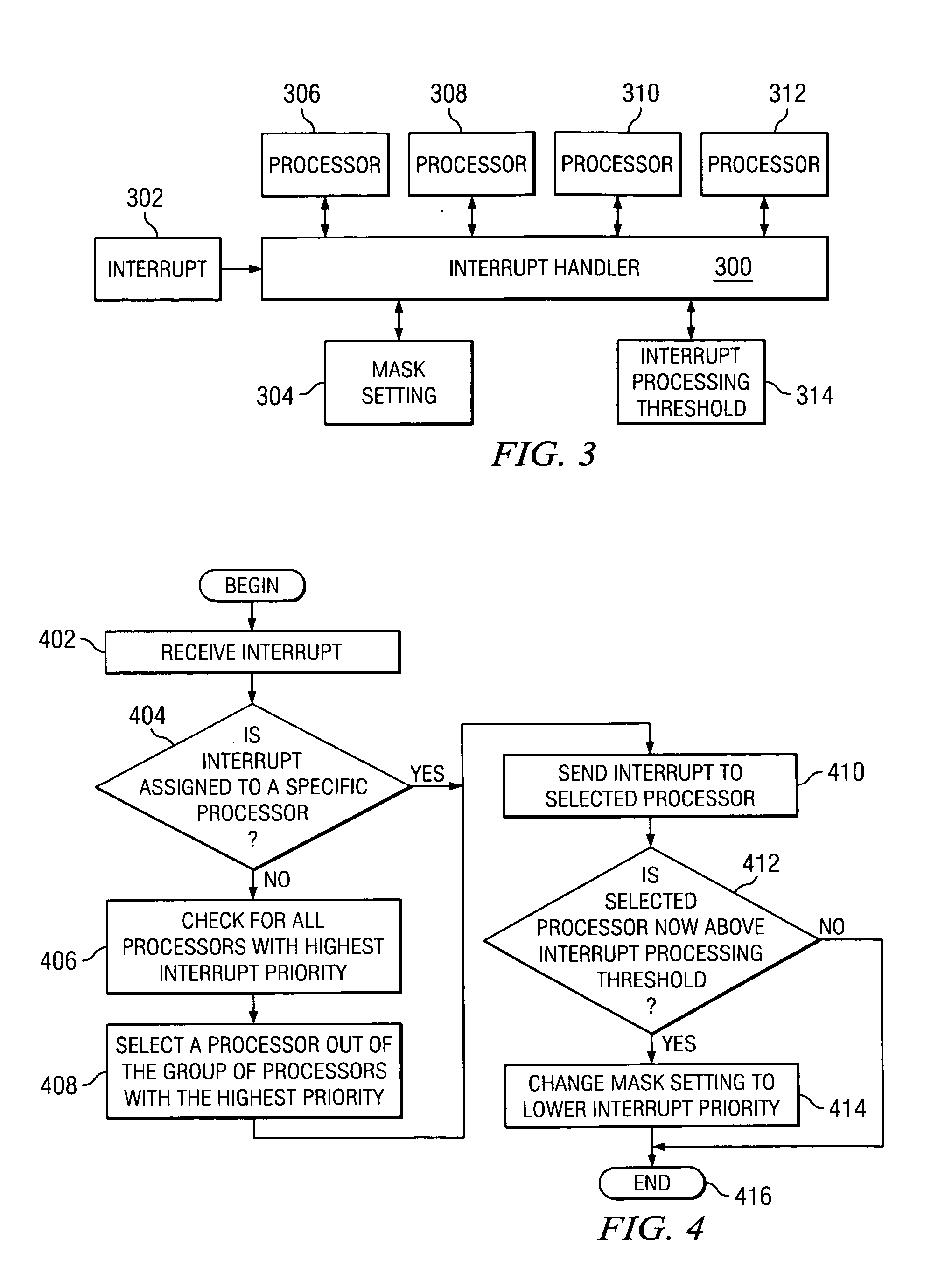

Interrupt thresholding for SMT and multi processor systems

InactiveUS20060112208A1Easy to implementDecreasing priority levelElectric digital data processingMulti processorInterrupt priority level

A method, system and computer program product for processing interrupts in a multi-processor system is provided. The method, system and computer program product process interrupts utilizing an unequal scheduling policy in order to achieve SLA target goals for interrupt processing. In a method of the present invention an interrupt is received. A determination is made as to whether the interrupt is assigned to a specific processor. If the interrupt is not assigned to a specific processor then a processor is selected from the group of processors based on their respective interrupt priority levels. Specifically, one processor is selected from all the processors that have the highest interrupt priority level. After the interrupt has been processed by the selected processor, a determination is made as to whether the selected processor has exceeded its threshold processing level. If threshold processing level has been exceeded, the selected processor's interrupt priority level is lowered.

Owner:IBM CORP

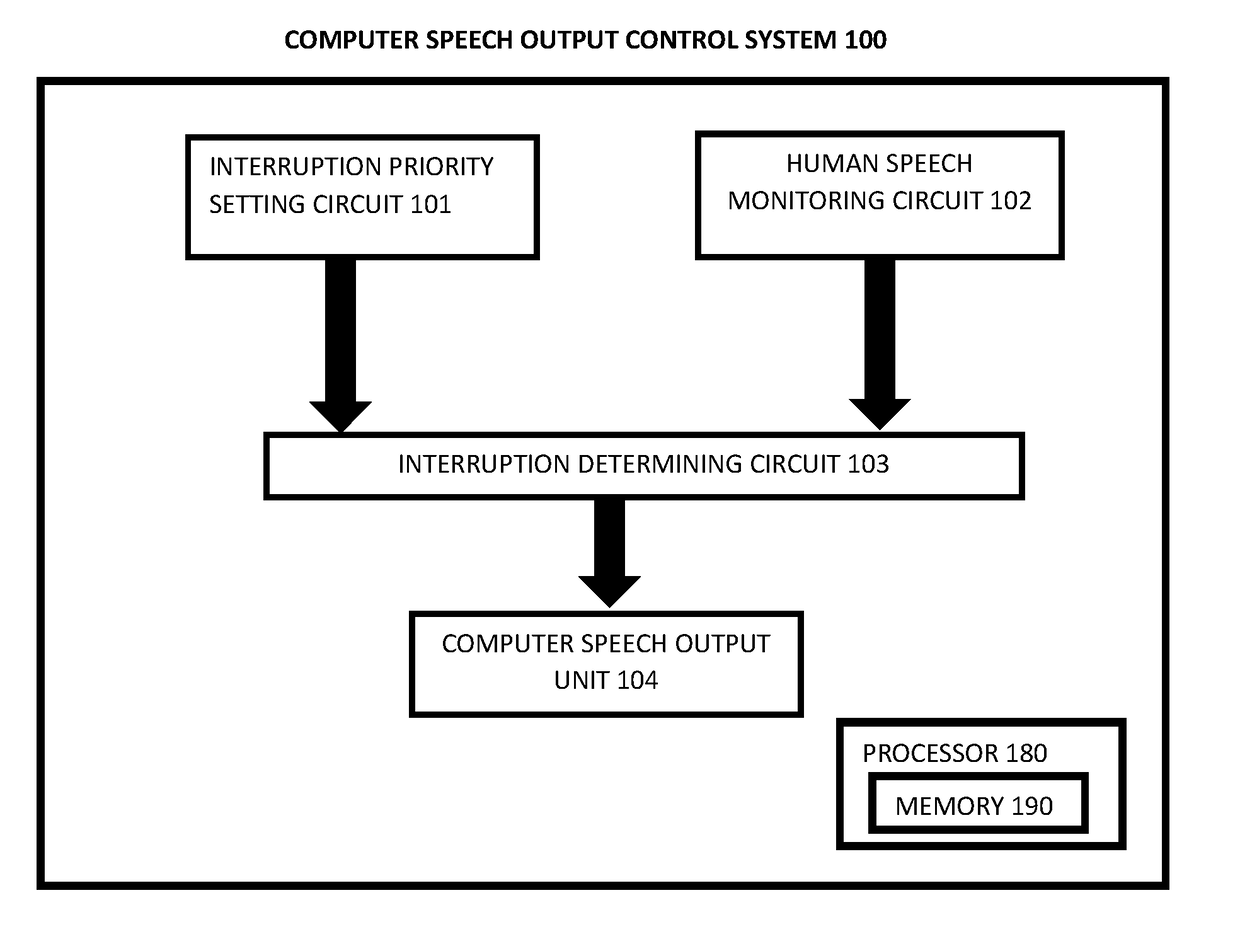

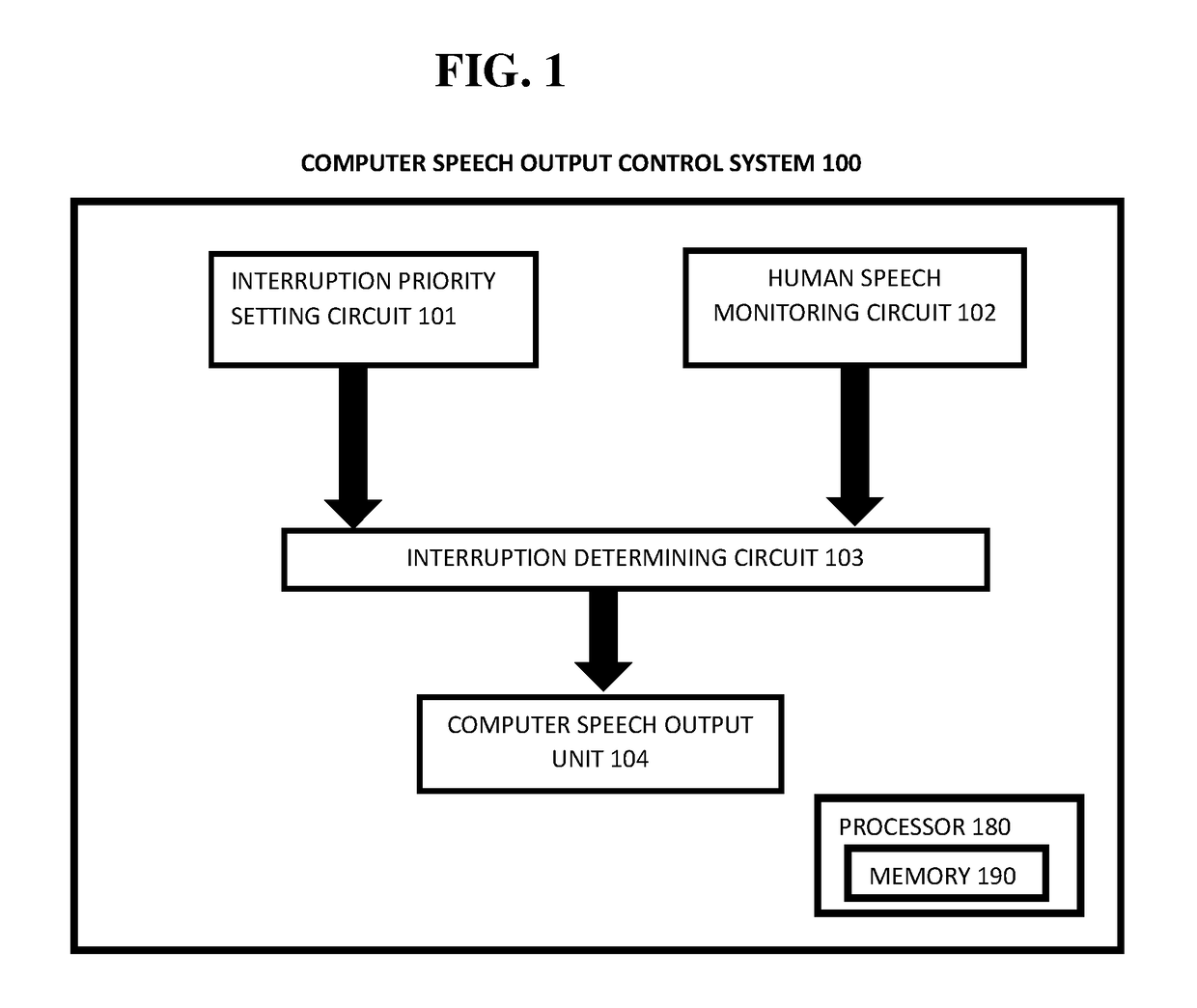

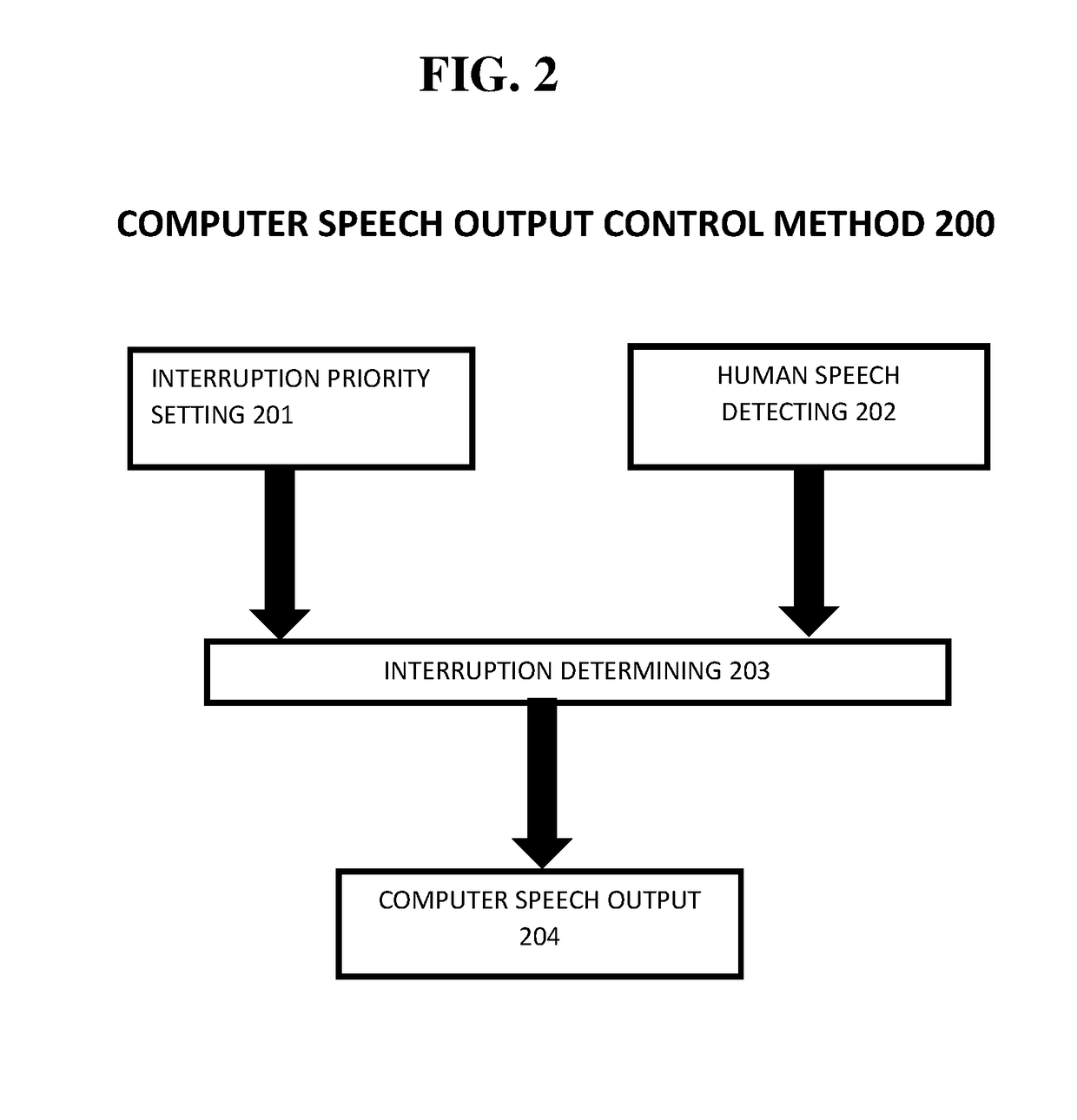

System, method, and recording medium for controlling dialogue interruptions by a speech output device

ActiveUS20170345429A1Speech recognitionInput/output processes for data processingControl systemPriority setting

A computer speech output control method, system, and non-transitory computer readable medium, include a computer speech output control system, including a computer speech output unit configured to output a computer speech, a human speech monitoring circuit configured to determine whether a human conversation is occurring, an interruption priority setting circuit configured to set a priority setting for when the human conversation can be interrupted by the computer speech, and an interruption determining circuit configured to determine whether to cause the computer speech output unit to output the computer speech based on the priority setting and a status of the human conversation.

Owner:IBM CORP

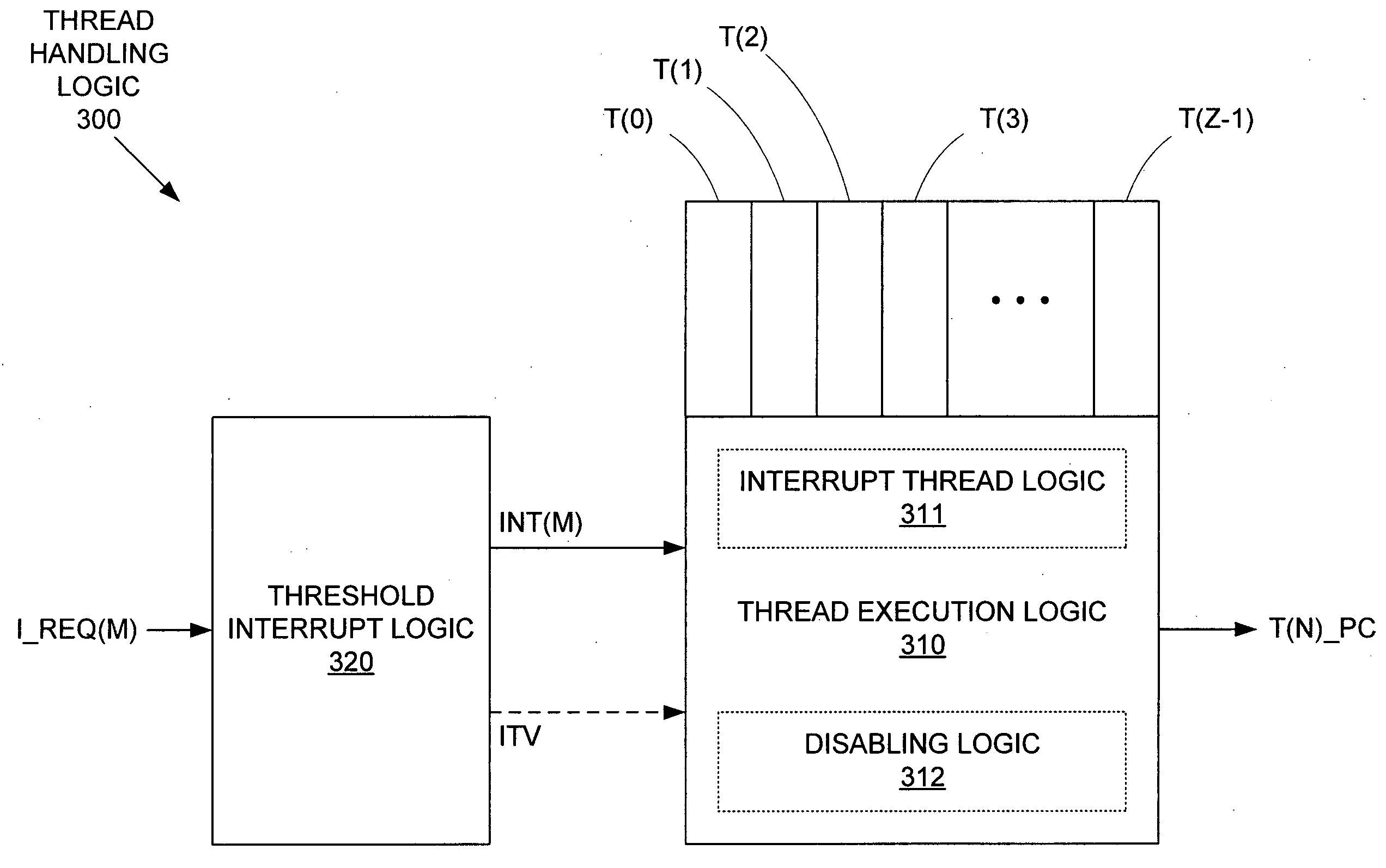

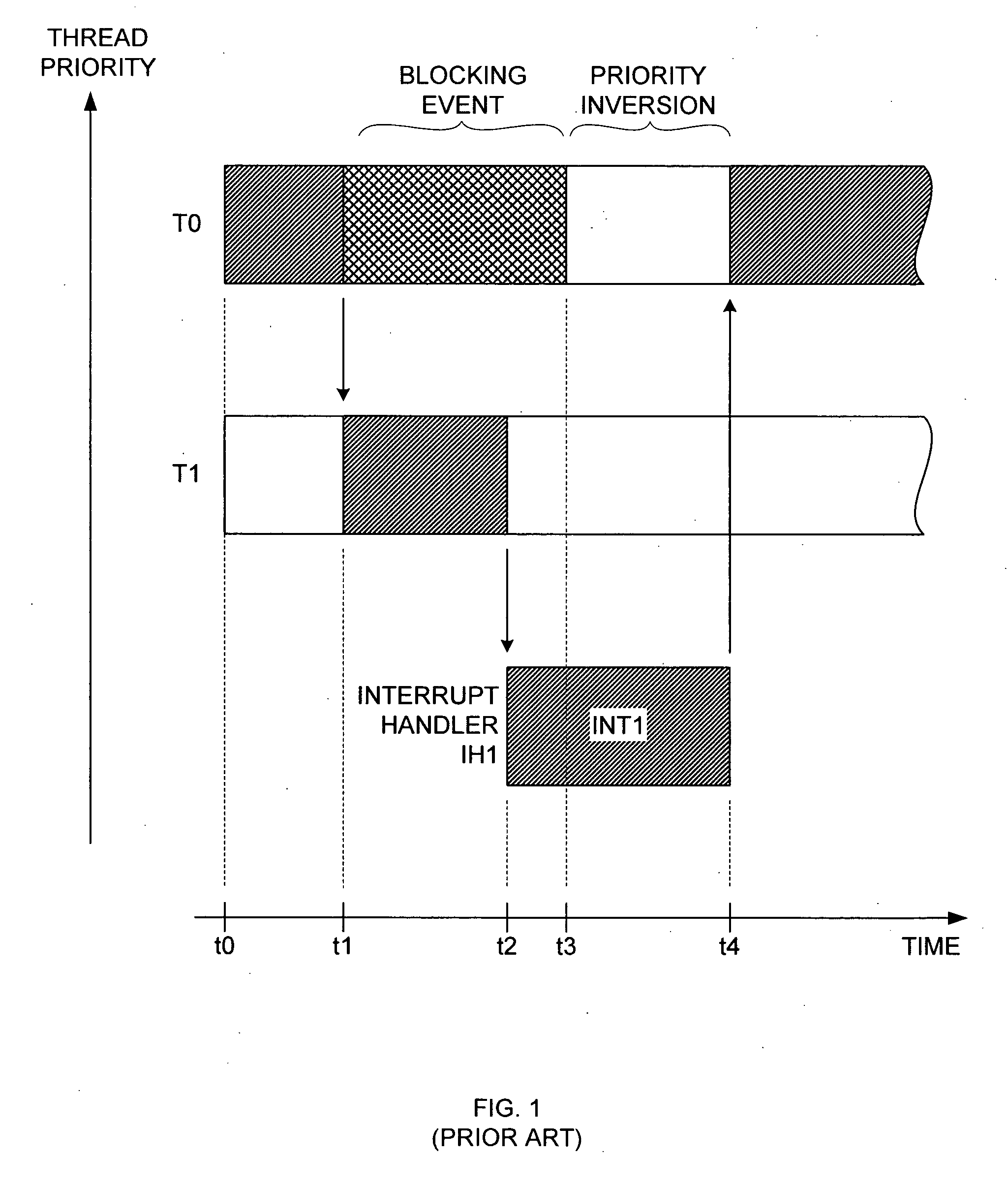

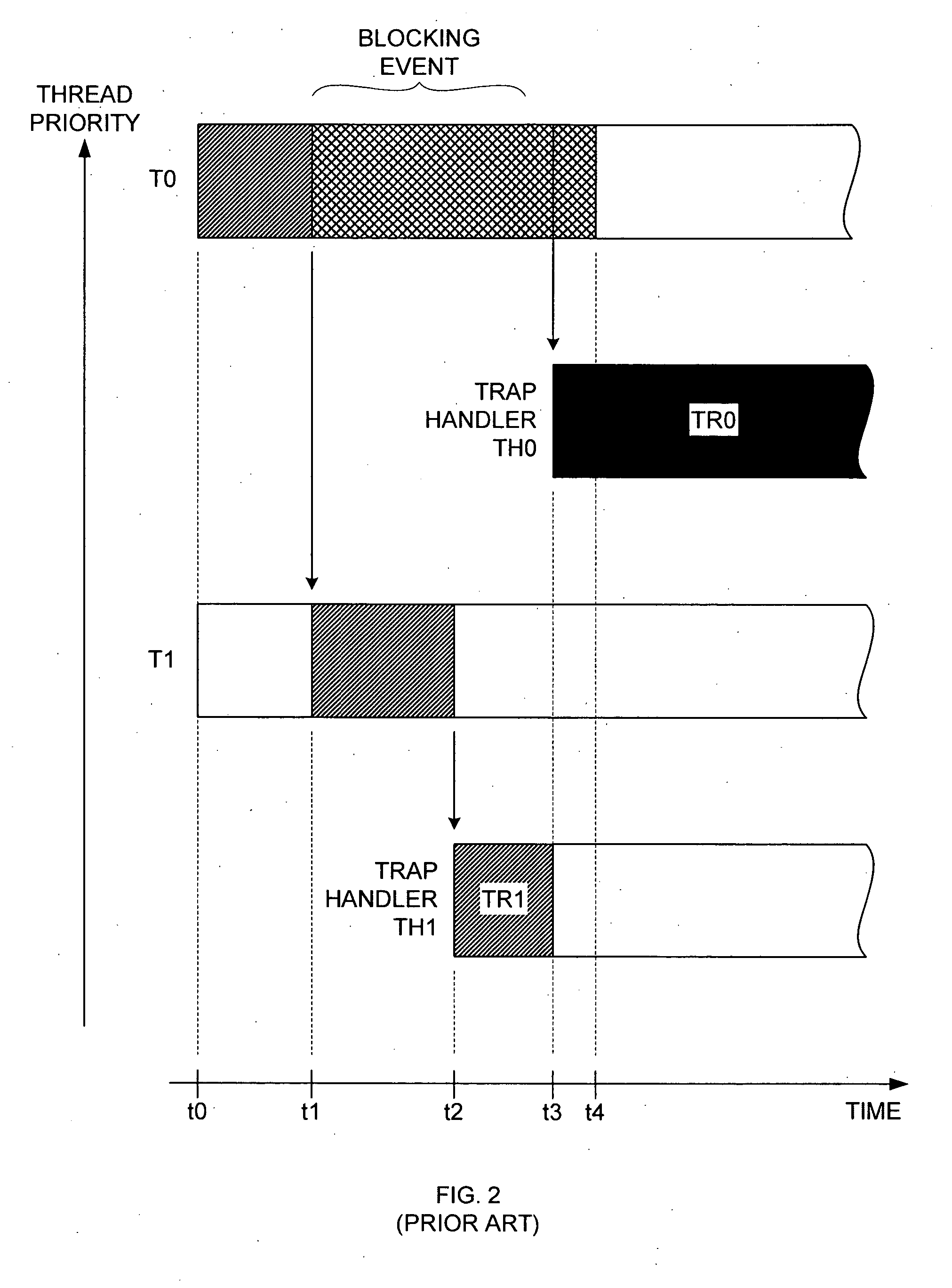

Interrupt and trap handling in an embedded multi-thread processor to avoid priority inversion and maintain real-time operation

ActiveUS20050102458A1Preventing unintended trap re-entrancySave on handlingProgram initiation/switchingDigital computer detailsPriority inversionEmbedded system

A real-time, multi-threaded embedded system includes rules for handling traps and interrupts to avoid problems such as priority inversion and re-entrancy. By defining a global interrupt priority value for all active threads and only accepting interrupts having a priority higher than the interrupt priority value, priority inversion can be avoided. Switching to the same thread before any interrupt servicing, and disabling interrupts and thread switching during interrupt servicing can simplify the interrupt handling logic. By storing trap background data for traps and servicing traps only in their originating threads, trap traceability can be preserved. By disabling interrupts and thread switching during trap servicing, unintended trap re-entrancy and servicing disruption can be prevented.

Owner:INFINEON TECH AG

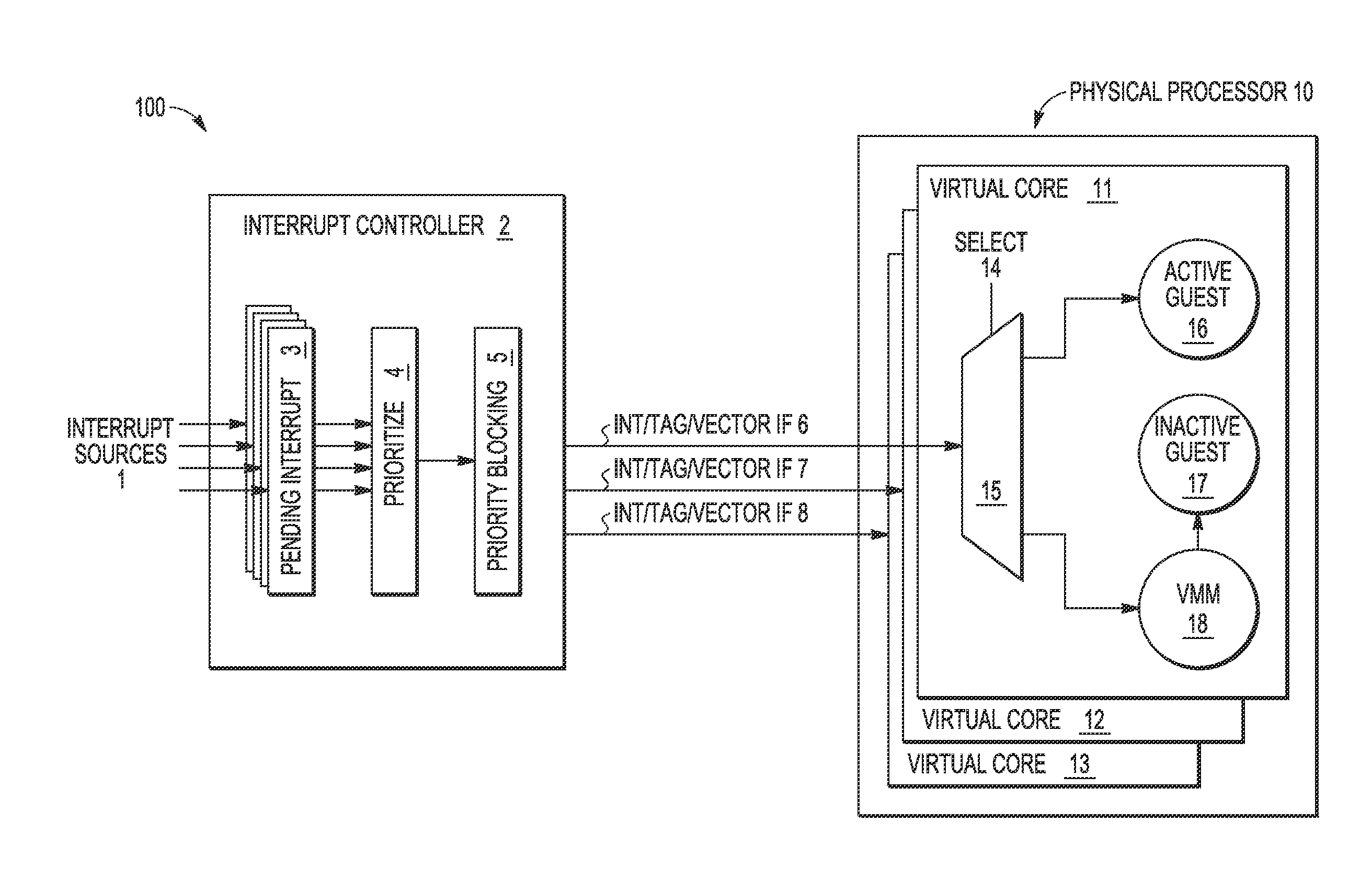

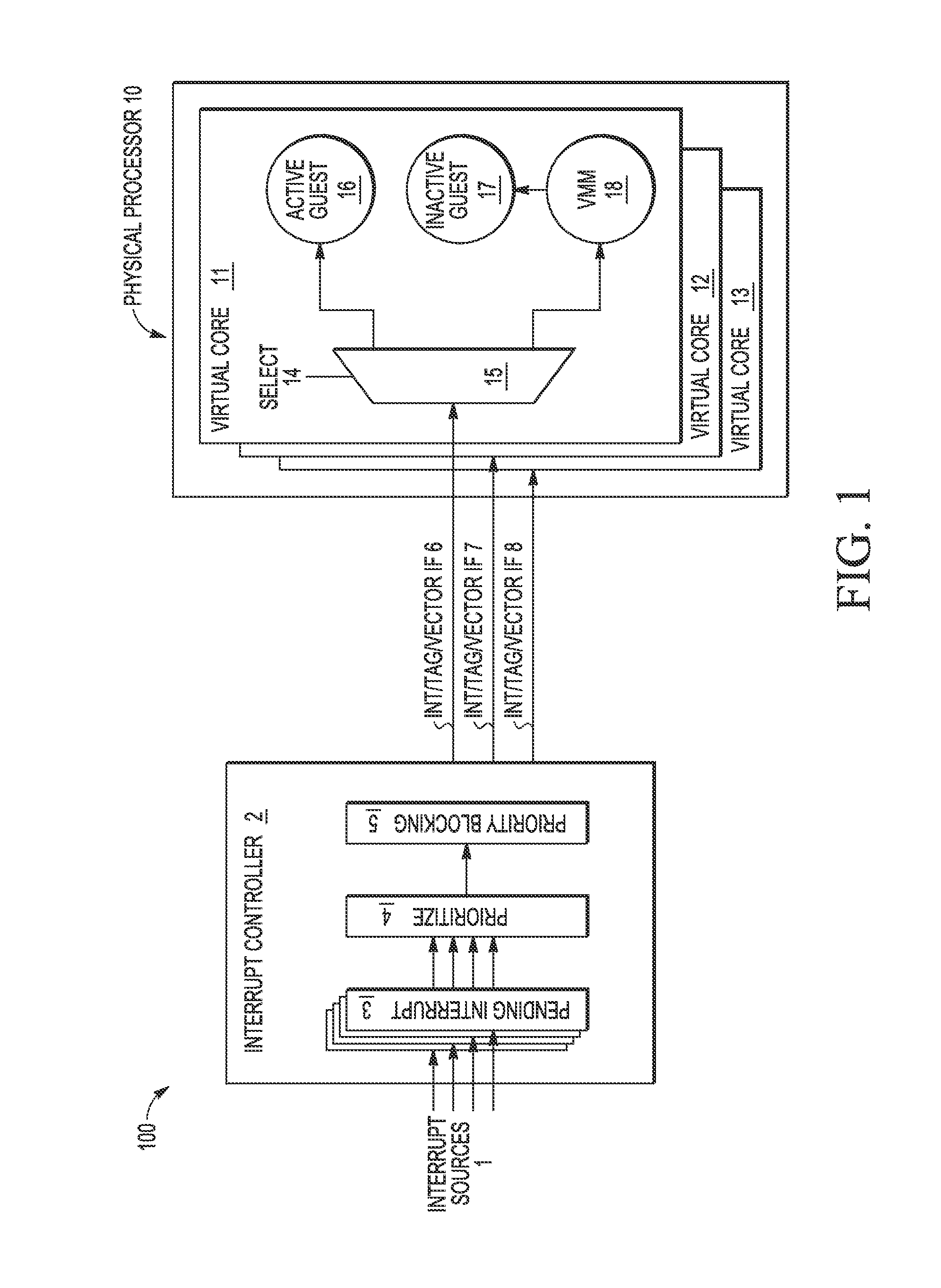

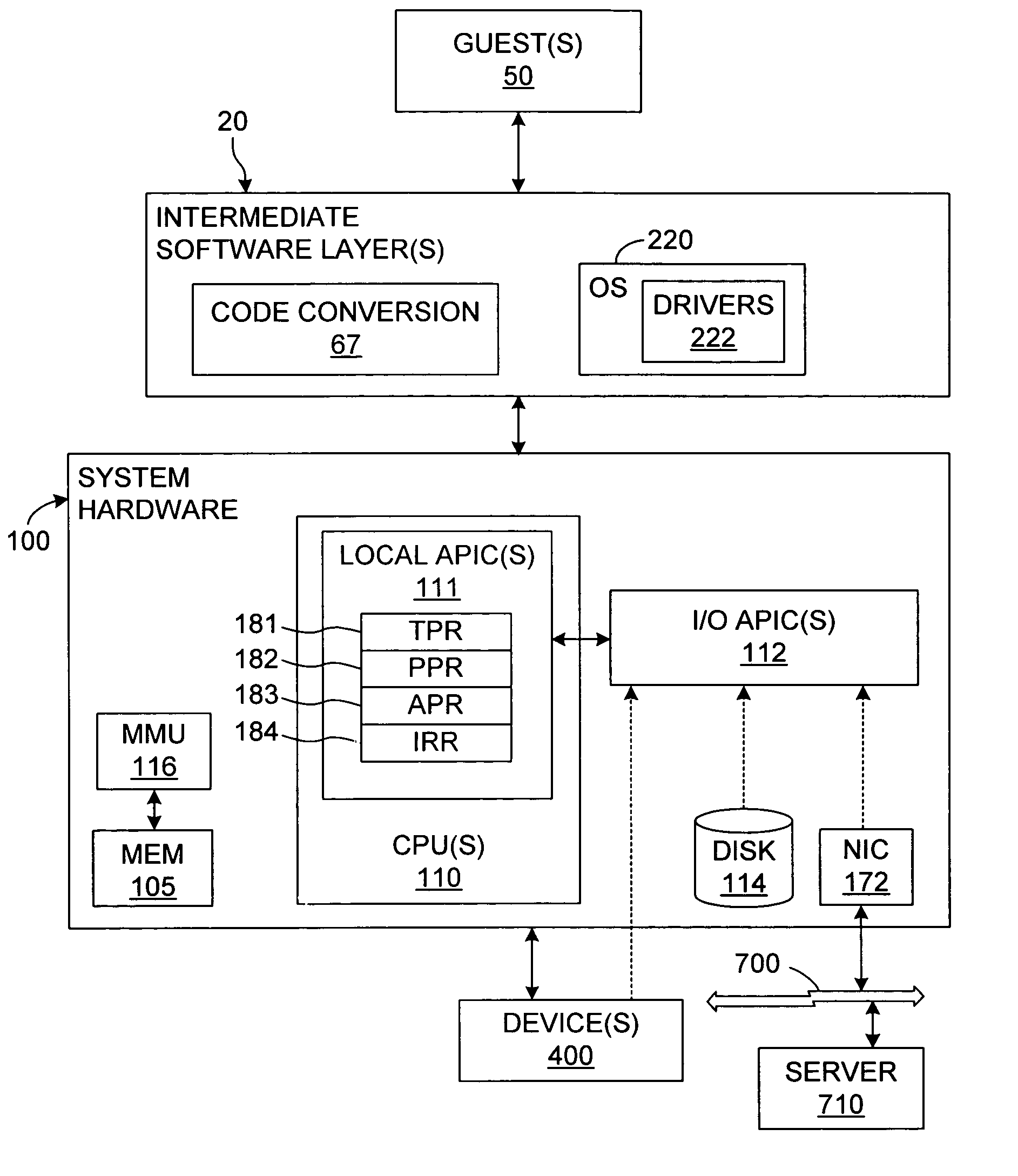

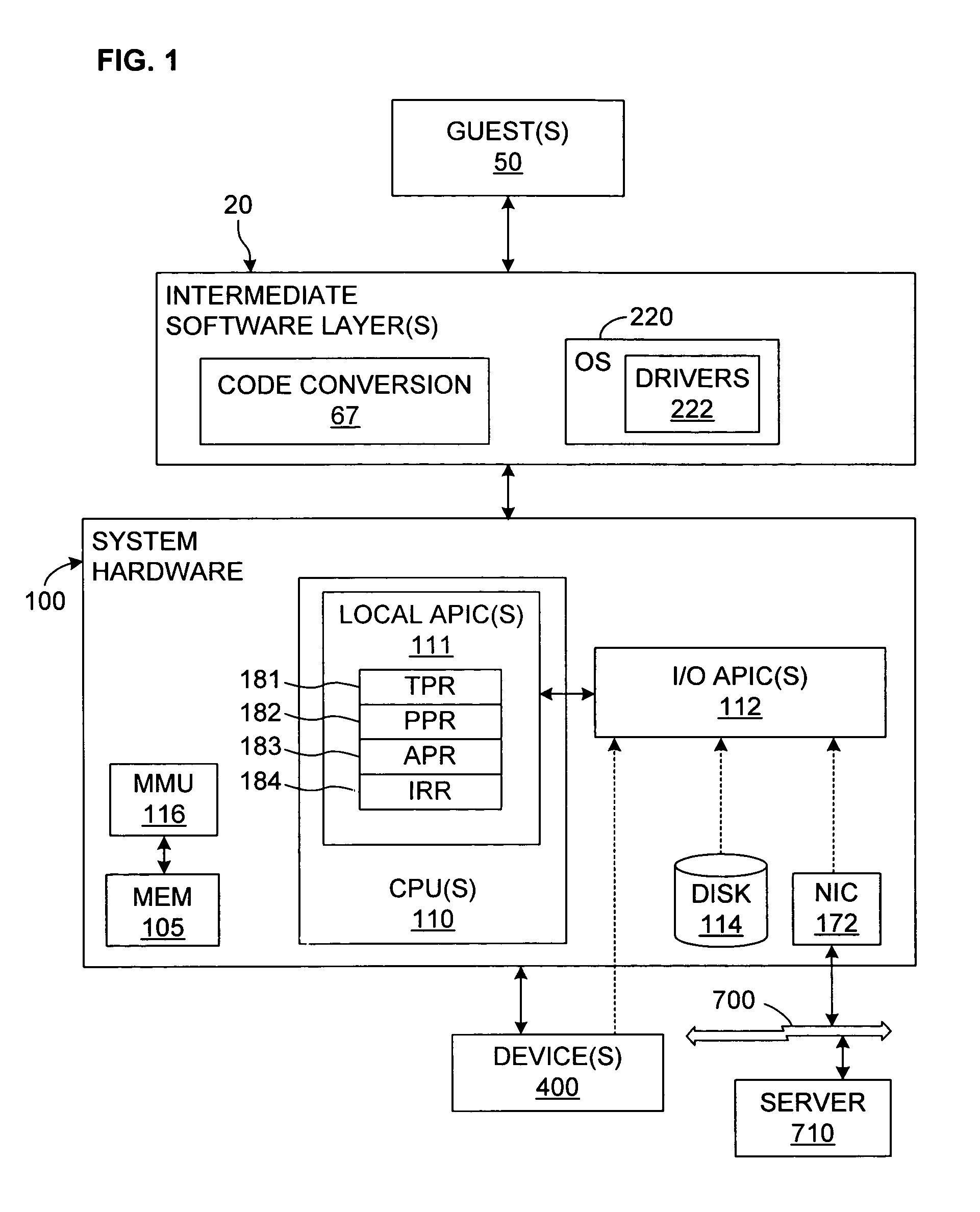

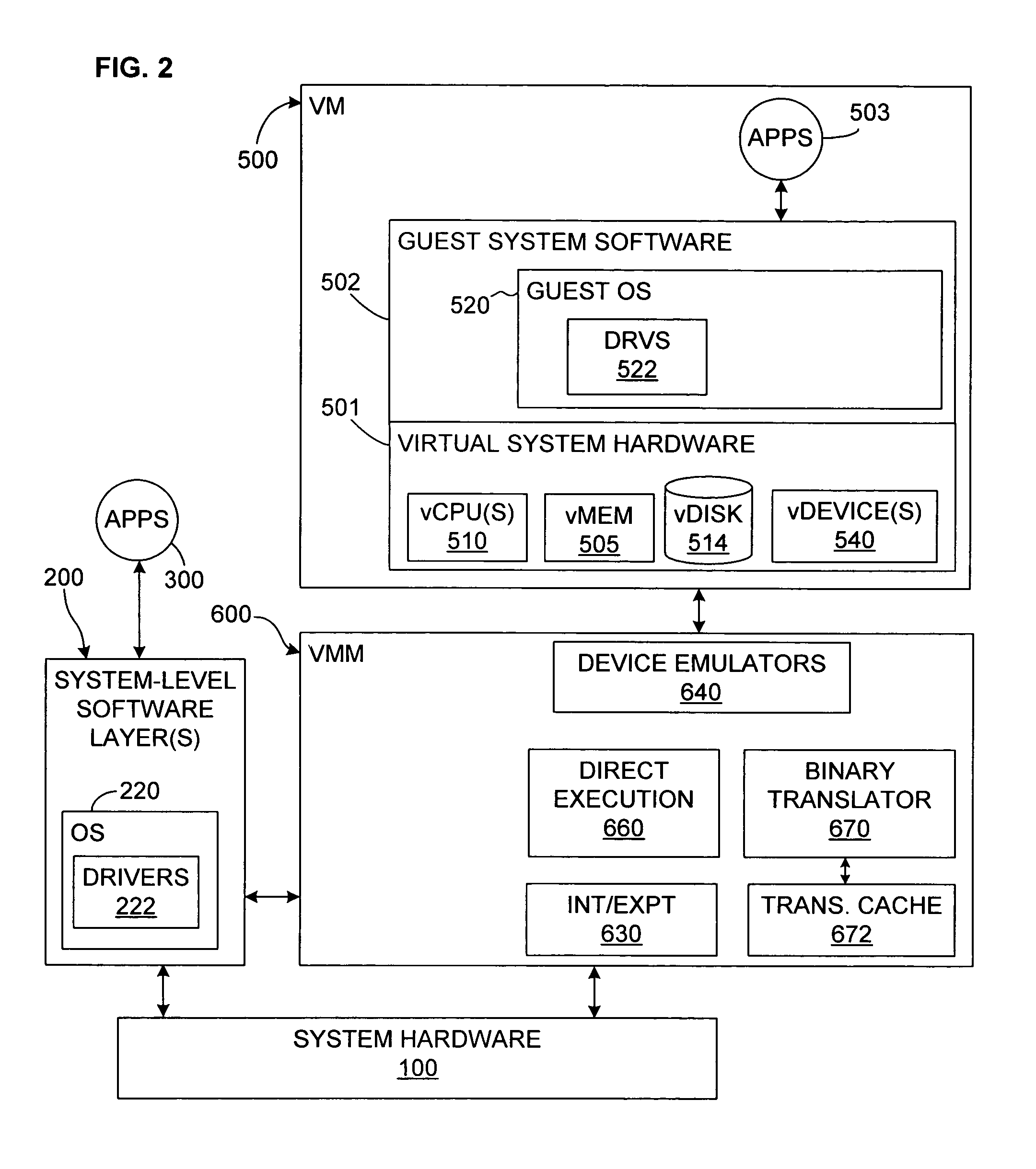

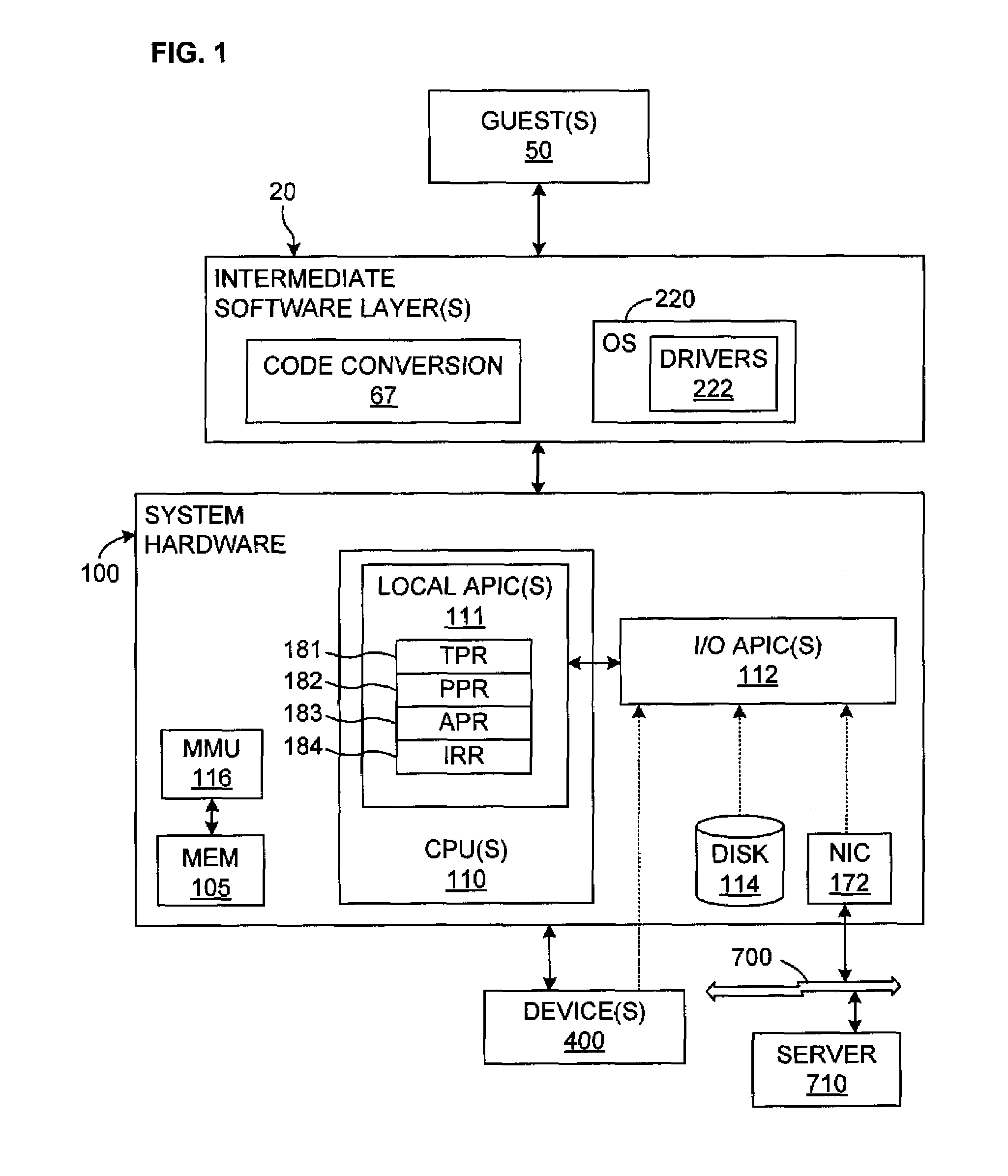

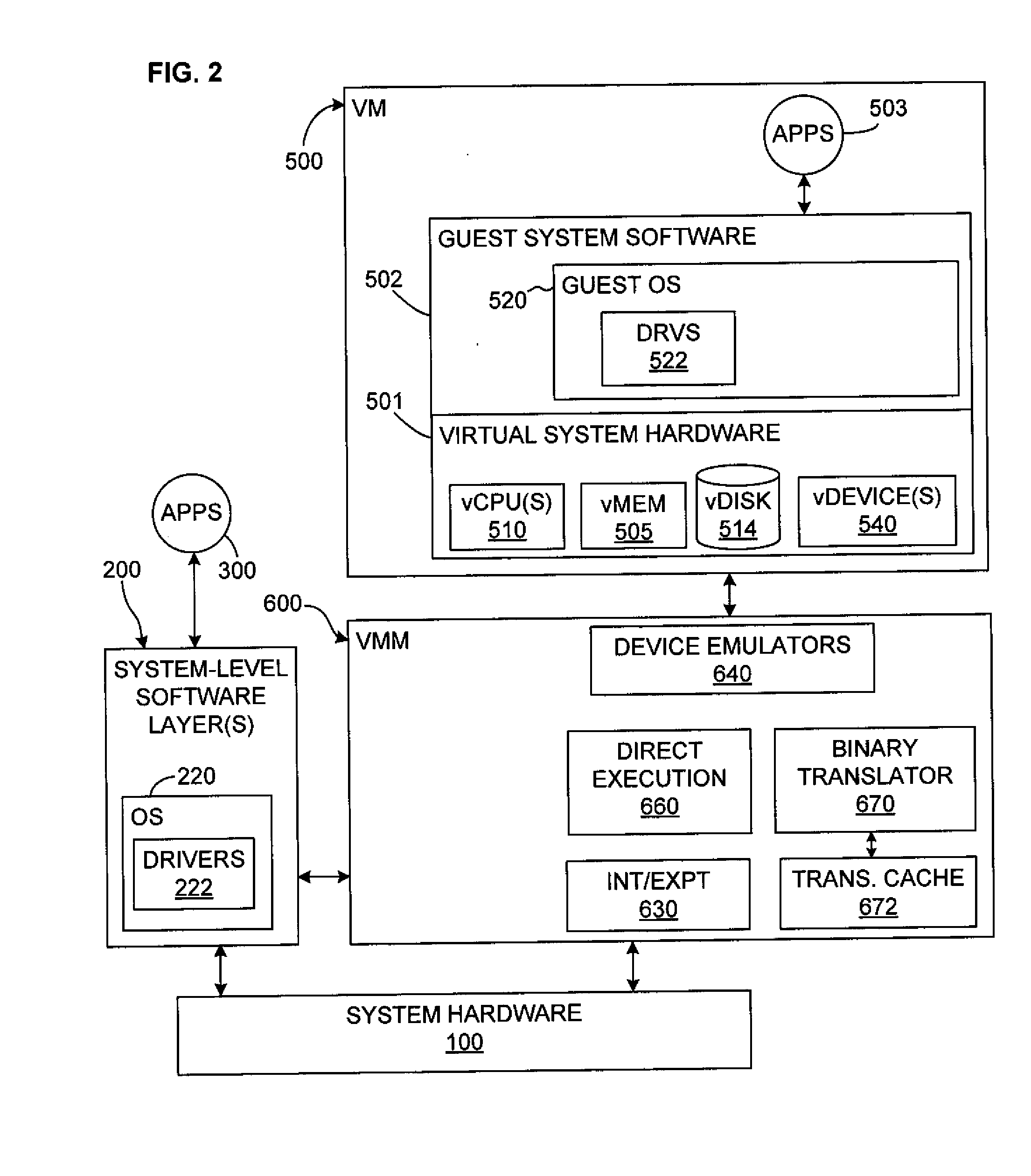

System and method for virtualizing processor and interrupt priorities

ActiveUS7590982B1Multiprogramming arrangementsSoftware simulation/interpretation/emulationVirtualizationProcessor scheduling

Dispatching of interrupts to a processor is conditionally suppressed, that is, only if an old priority value and a new priority value are either both less than or both greater than a maximum pending priority value. This conditional avoidance of dispatching is preferably implemented by a virtual priority module within a binary translator in a virtualized computer system and relates to interrupts directed to a virtualized processor by a virtualized local APIC.

Owner:VMWARE INC

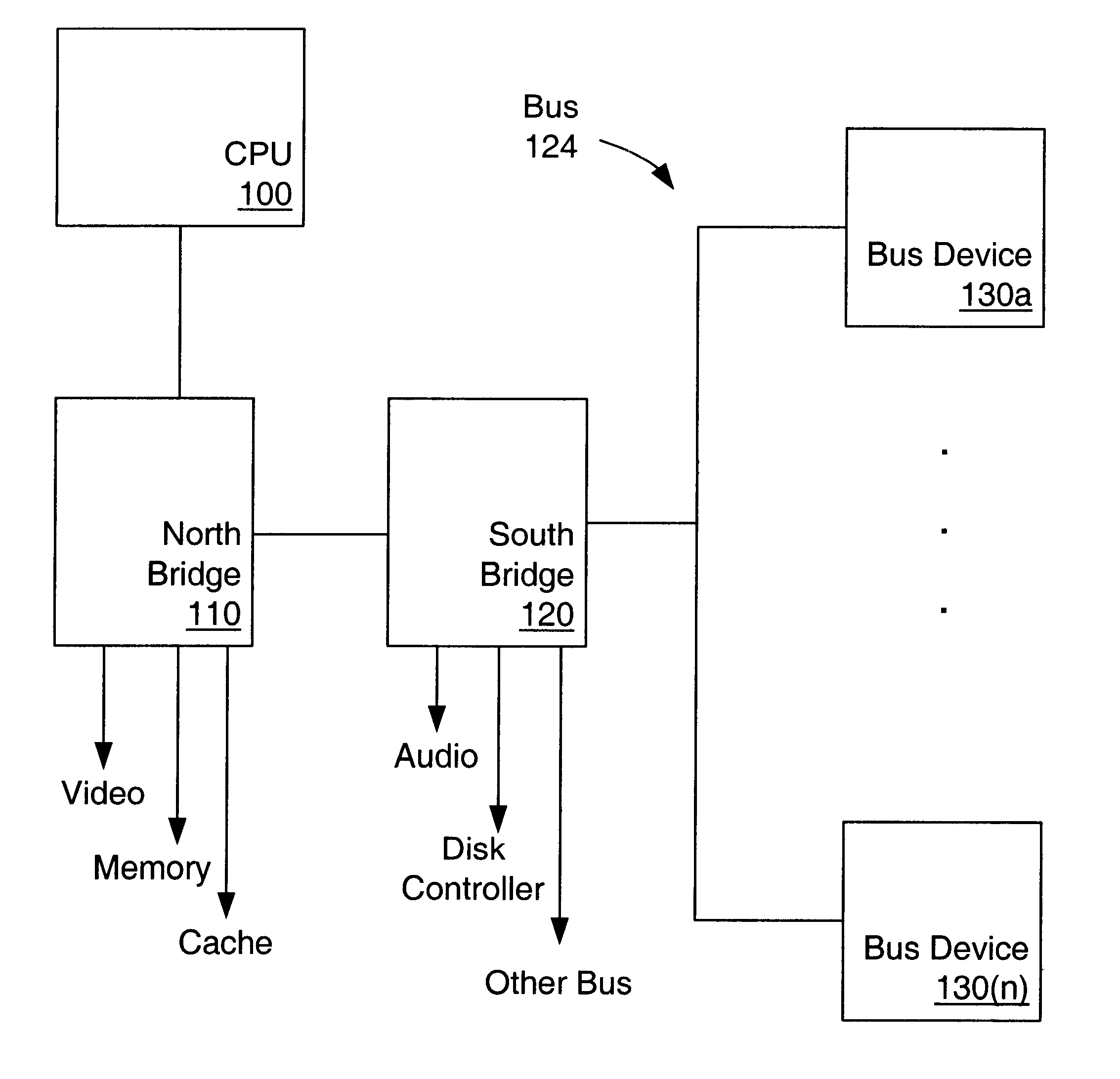

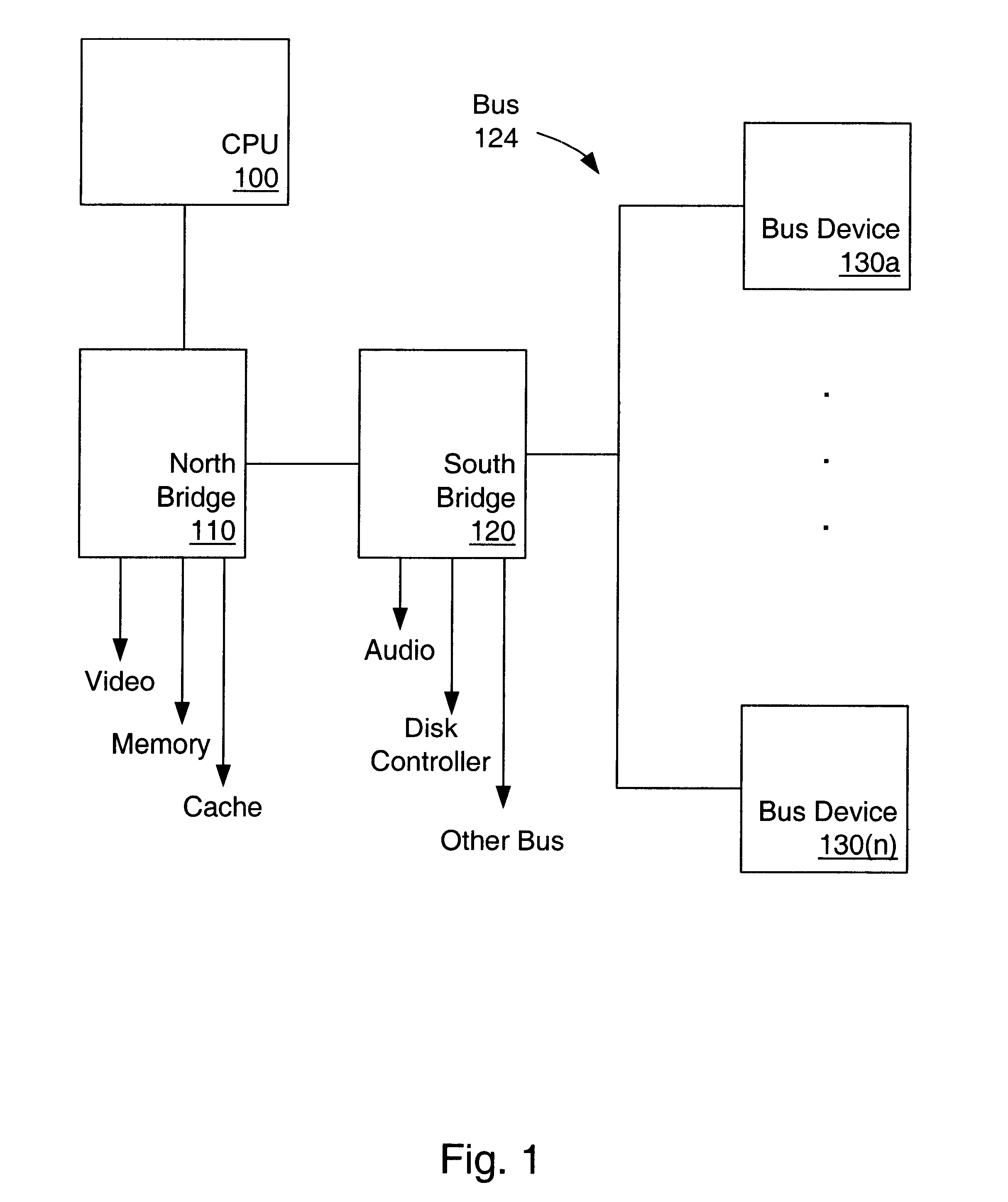

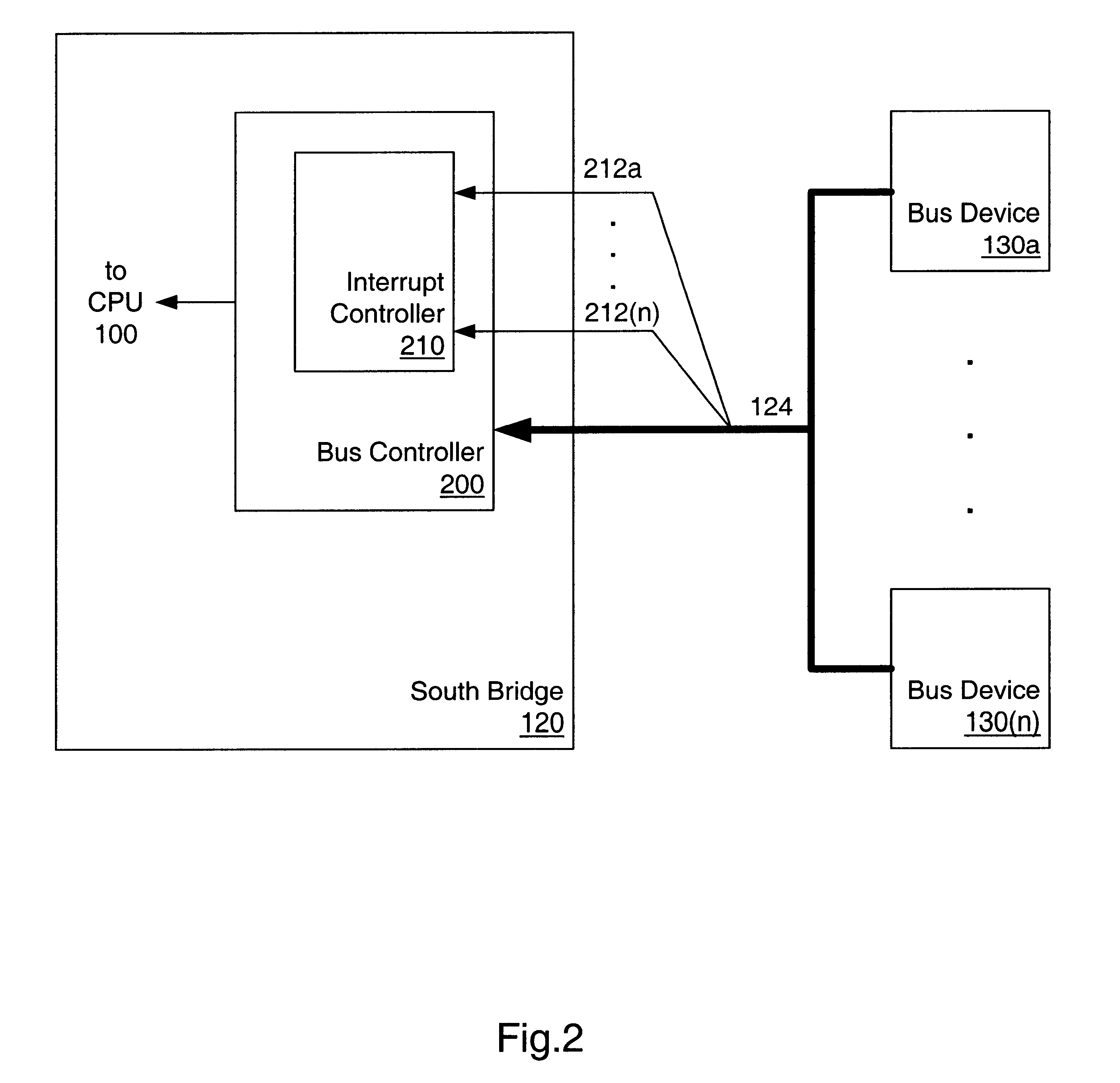

System and method for implementing a multi-level interrupt scheme in a computer system

A system and method for implementing a multi-level interrupt scheme in a computer system is provided. Bus devices and a bus controller may be coupled to a shared bus in a computer system. The bus may include an interrupt line for each bus device coupled to the bus. A bus device may be configured to convey an interrupt using its designated interrupt line. Each bus device may be configured to convey different types of interrupt signals on its interrupt line depending on an interrupt priority level of a given interrupt. The bus controller may be configured to receive interrupt signals from each bus device coupled to the bus and may arbitrate amongst the interrupt signals based on the interrupt priority level of each interrupt signal. The bus controller may grant the interrupt that corresponds to the highest priority level. If multiple interrupts correspond to the same highest priority level in a group of interrupts, then the bus controller may use any suitable arbitration scheme to grant an interrupt.

Owner:ADVANCED MICRO DEVICES INC

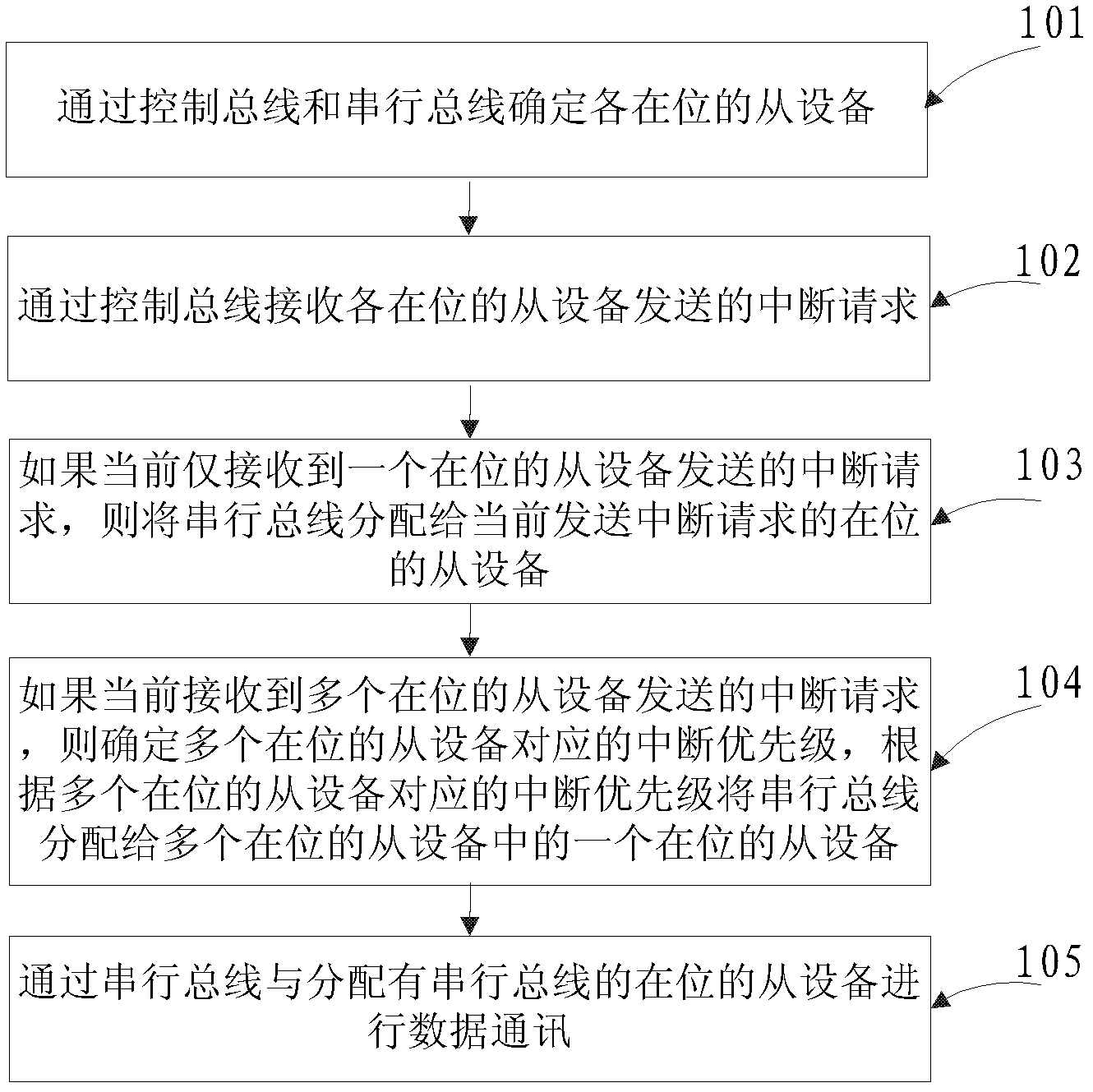

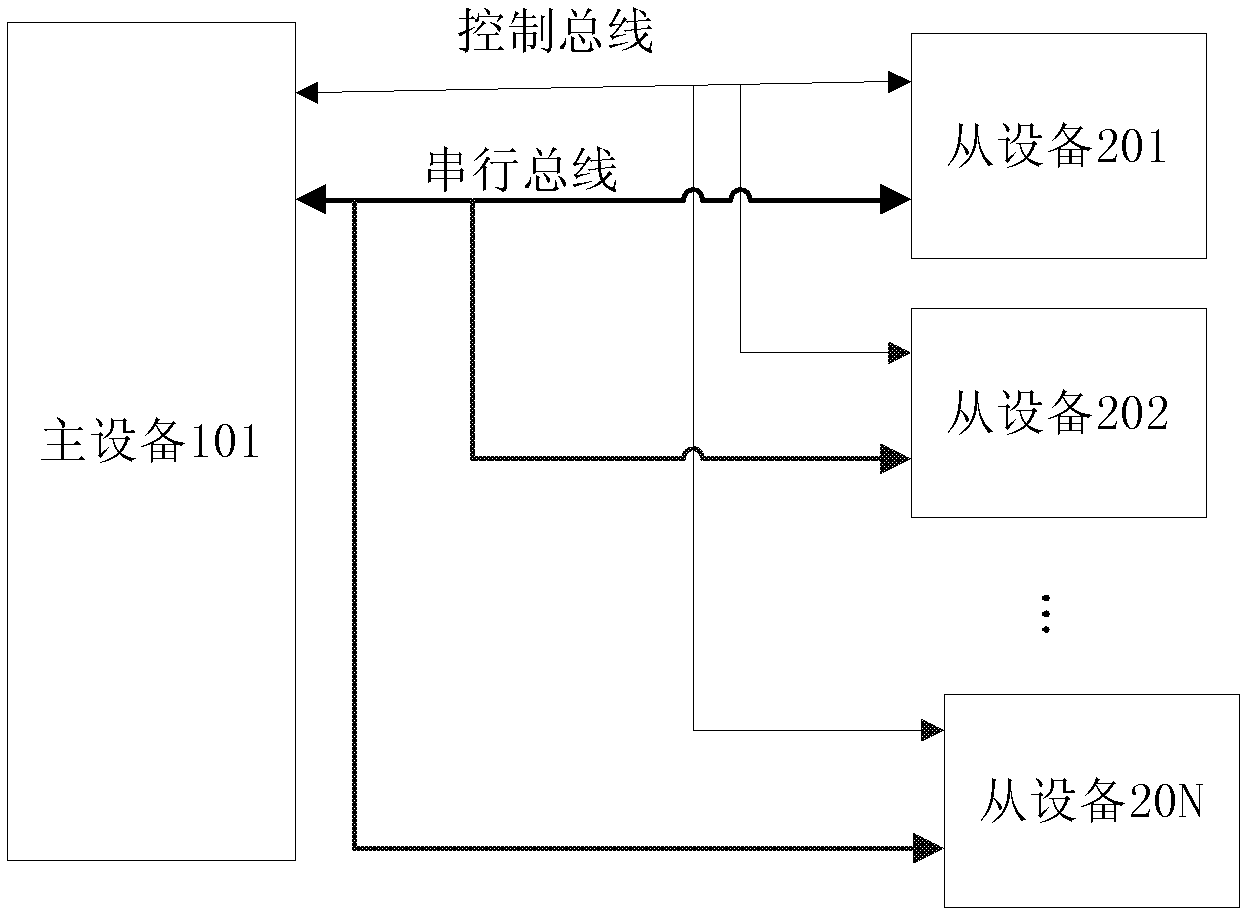

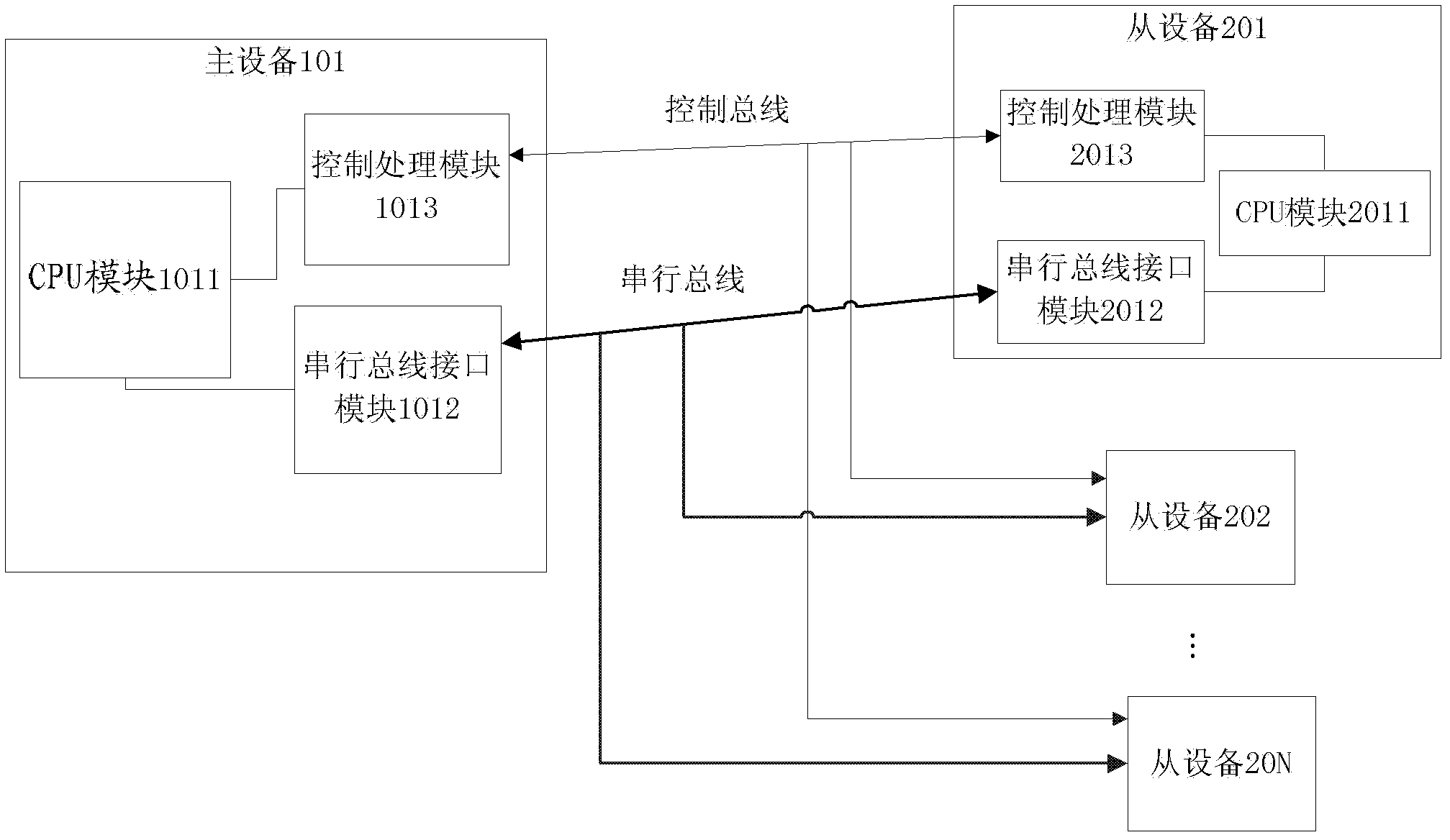

Method, device and system capable of achieving serial port communication

InactiveCN103166821AImprove processing efficiencyWill not cause conflictBus networksProcess efficiencyControl bus

The invention discloses a method, a device and a system capable of achieving serial port communication and belongs to the communication technical field. The method comprises the following steps: each slave device in place is ascertained through a control bus and a serial bus; each interrupt request sent by each slave device in place is received through the control bus; when the interrupt request of only one slave device in place is received at present, the serial bus is assigned to the slave device, in place, which sends the interrupt request at present; when the interrupt requests of a plurality of slave devices in place are received at present, a corresponding interrupt priority level of each of slave devices in place is ascertained and the serial bus is assigned to one of the slave devices in place according to the interrupt priority levels of the plurality of slave devices in place; and data communication is conducted through the serial bus and the slave device, in place, which the serial bus is assigned to. According to the technical scheme, device identification (ID) is not brought in, so that a series of problems which are caused by setting of the device ID in the prior art can be solved, processing efficiency of a primary device is improved and shared serial bus conflicts can not be caused.

Owner:SHENZHEN HUAWEI AGISSON ELECTRIC CO LTD

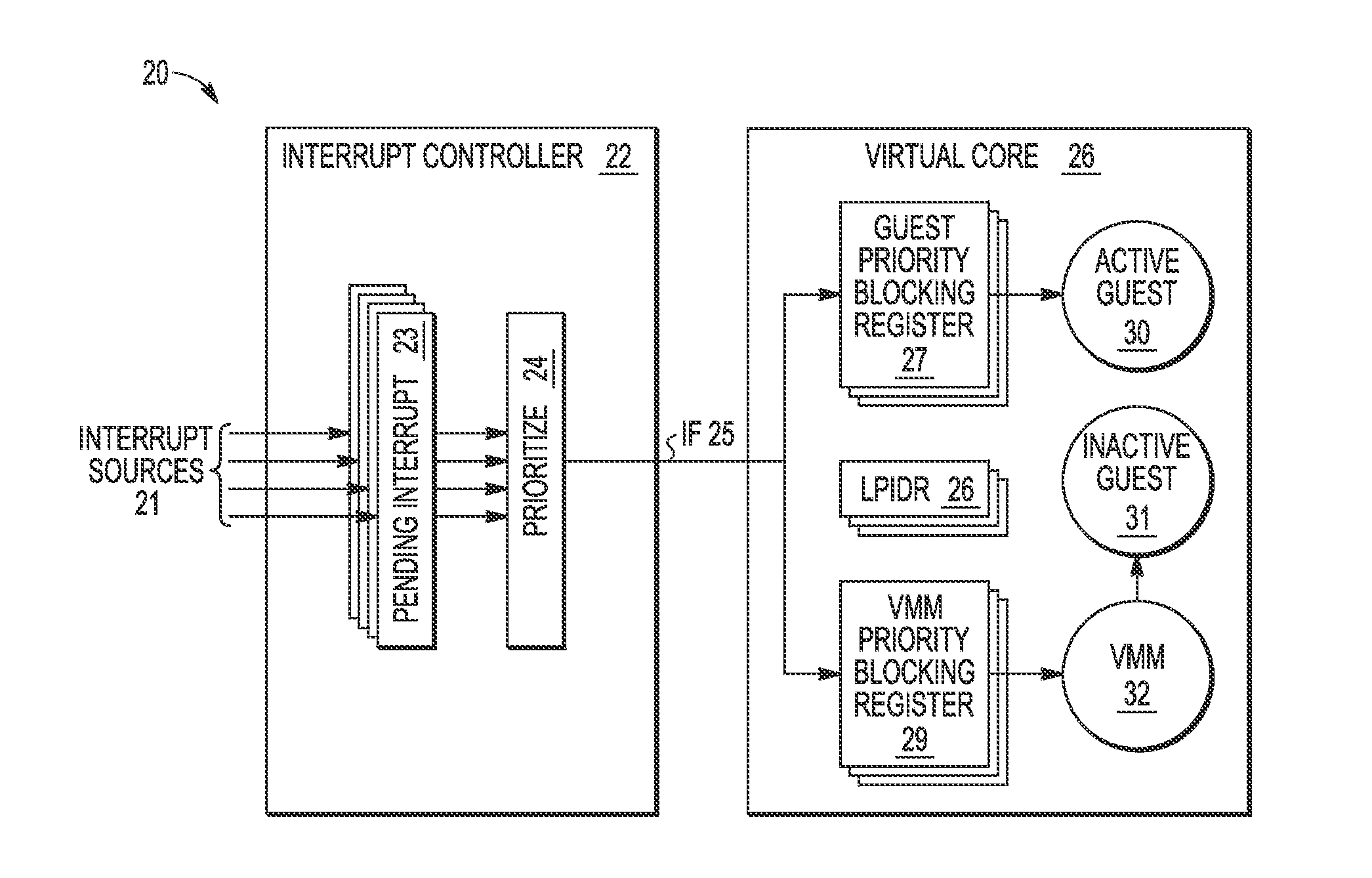

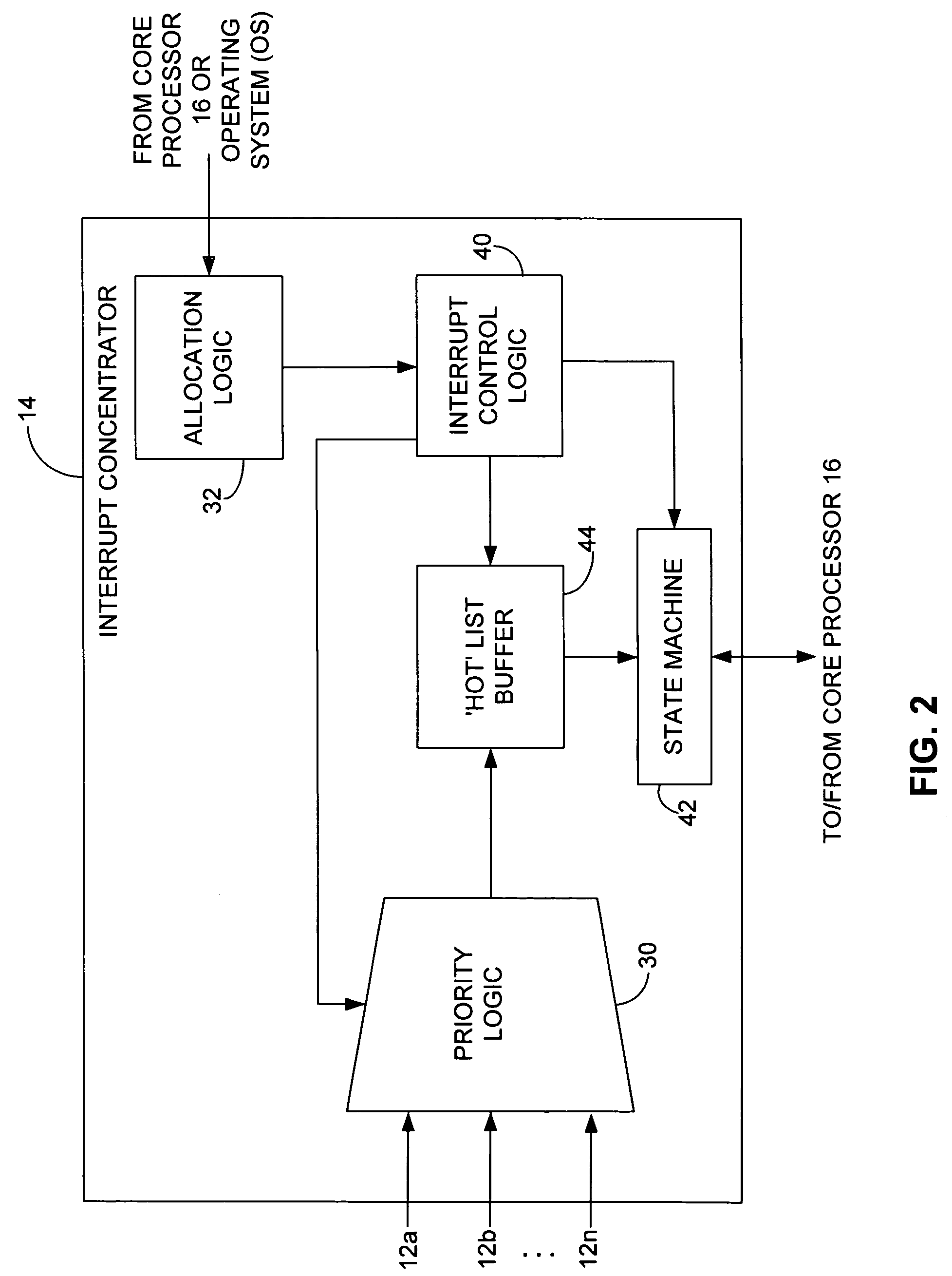

Interrupt Priority Management Using Partition-Based Priority Blocking Processor Registers

A method and circuit for a data processing system (20) provide a processor-based partitioned priority blocking mechanism by storing priority levels and associated partition information in special purpose registers (27-29) located at the processor core (26) to enable quick and efficient interrupt priority blocking on a partition basis.

Owner:NXP USA INC

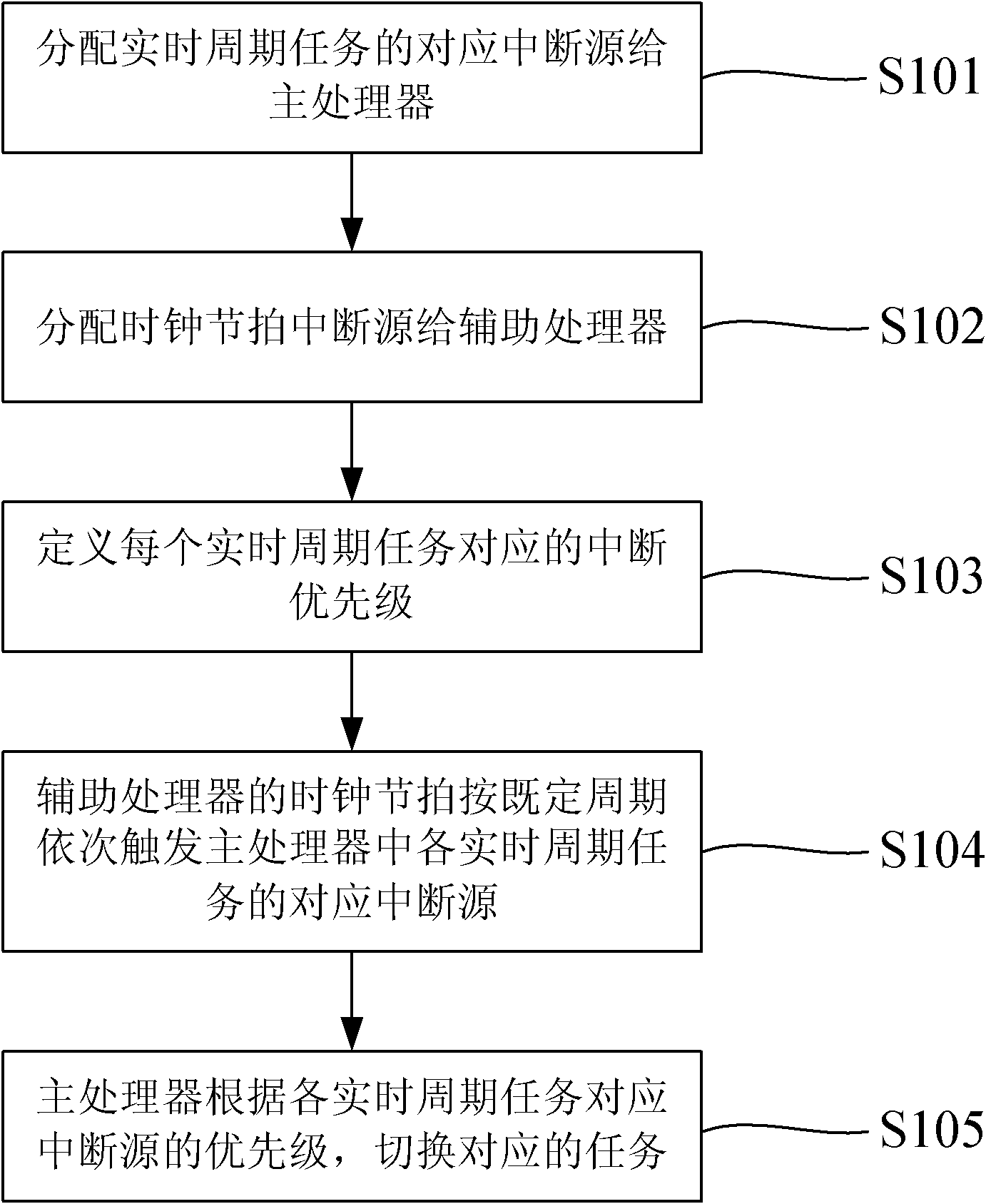

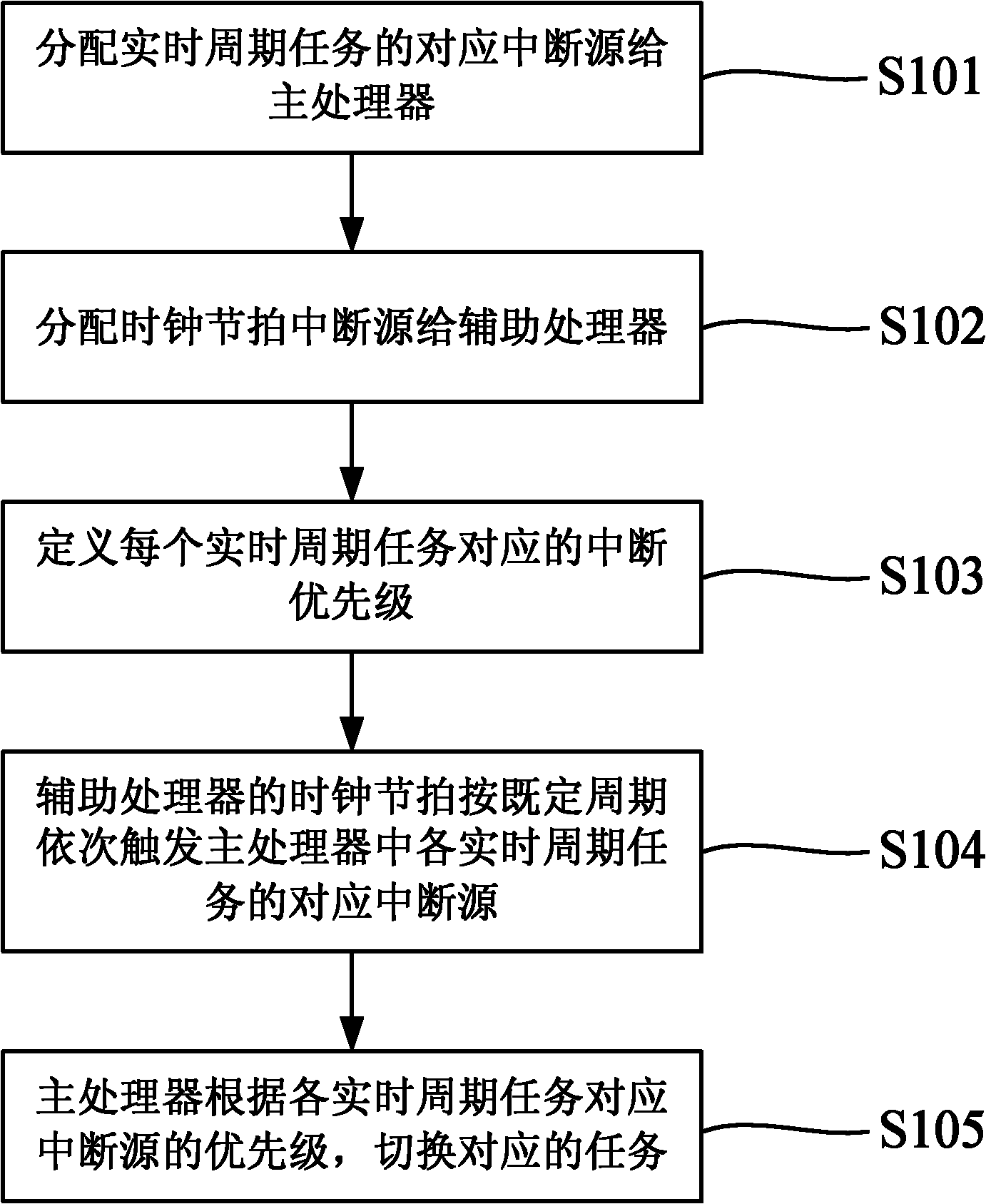

Real-time task scheduling method based on multicore processor

InactiveCN102222022ASave storage spaceReduce loadProgram initiation/switchingCoprocessorMaster processor

The invention provides a real-time task scheduling method based on a multicore processor, comprising the following steps of: distributing the corresponding interrupt source of a real-time periodic task to a main processor; distributing the interrupt source of a timing clock to an auxiliary processor; defining the interrupt priority level corresponding to each real-time periodic task; triggering the corresponding interrupt source of each real-time periodic task in the main processor in sequence according to established period by the timing clock of the auxiliary processor; and switching the corresponding task according to the priority level of the interrupt source corresponding to each real-time periodic task by the main processor. The method can reduce the load of the main processor, and has the advantages of small resource occupation, high cost performance and low development threshold.

Owner:范示德汽车技术(上海)有限公司

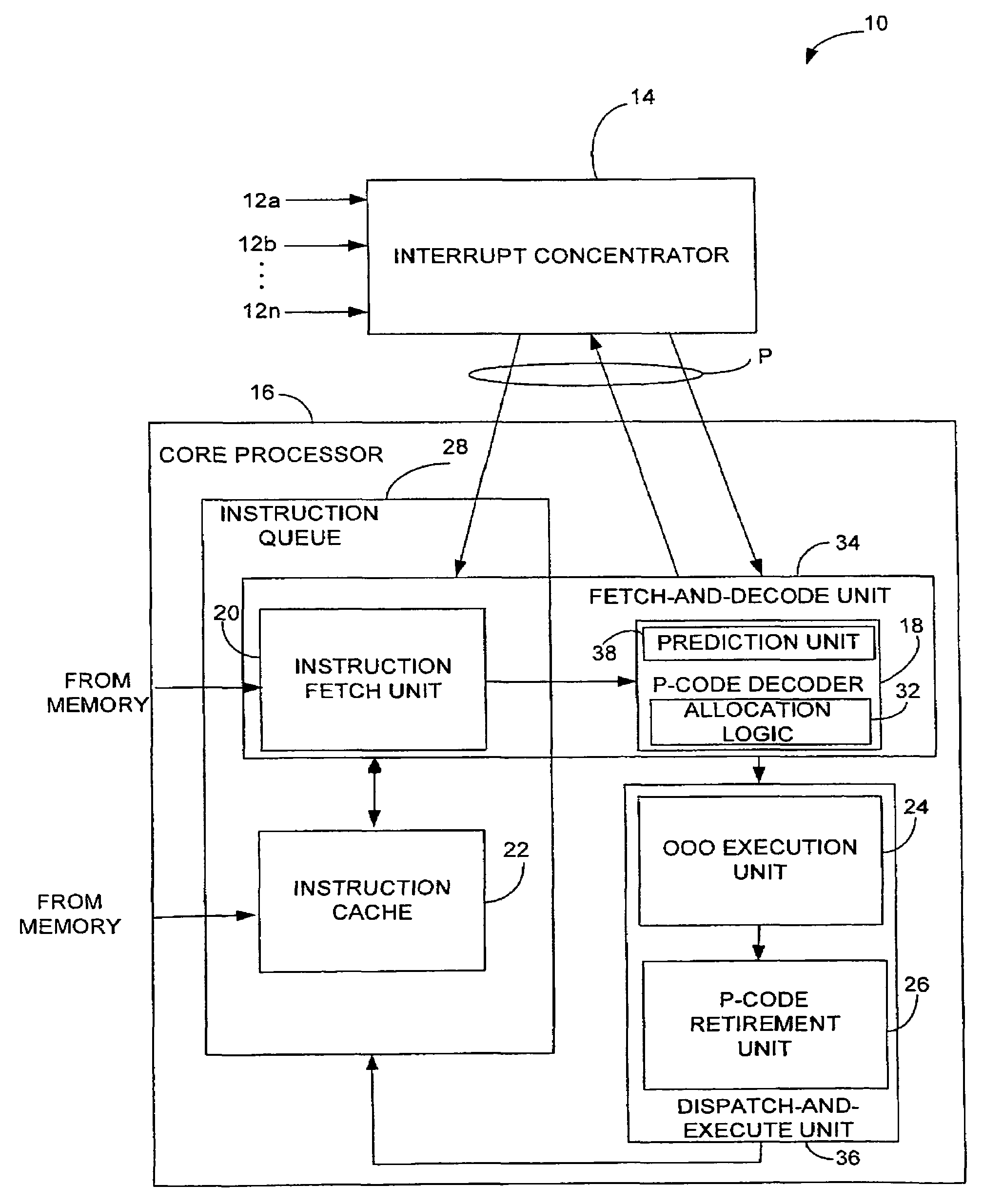

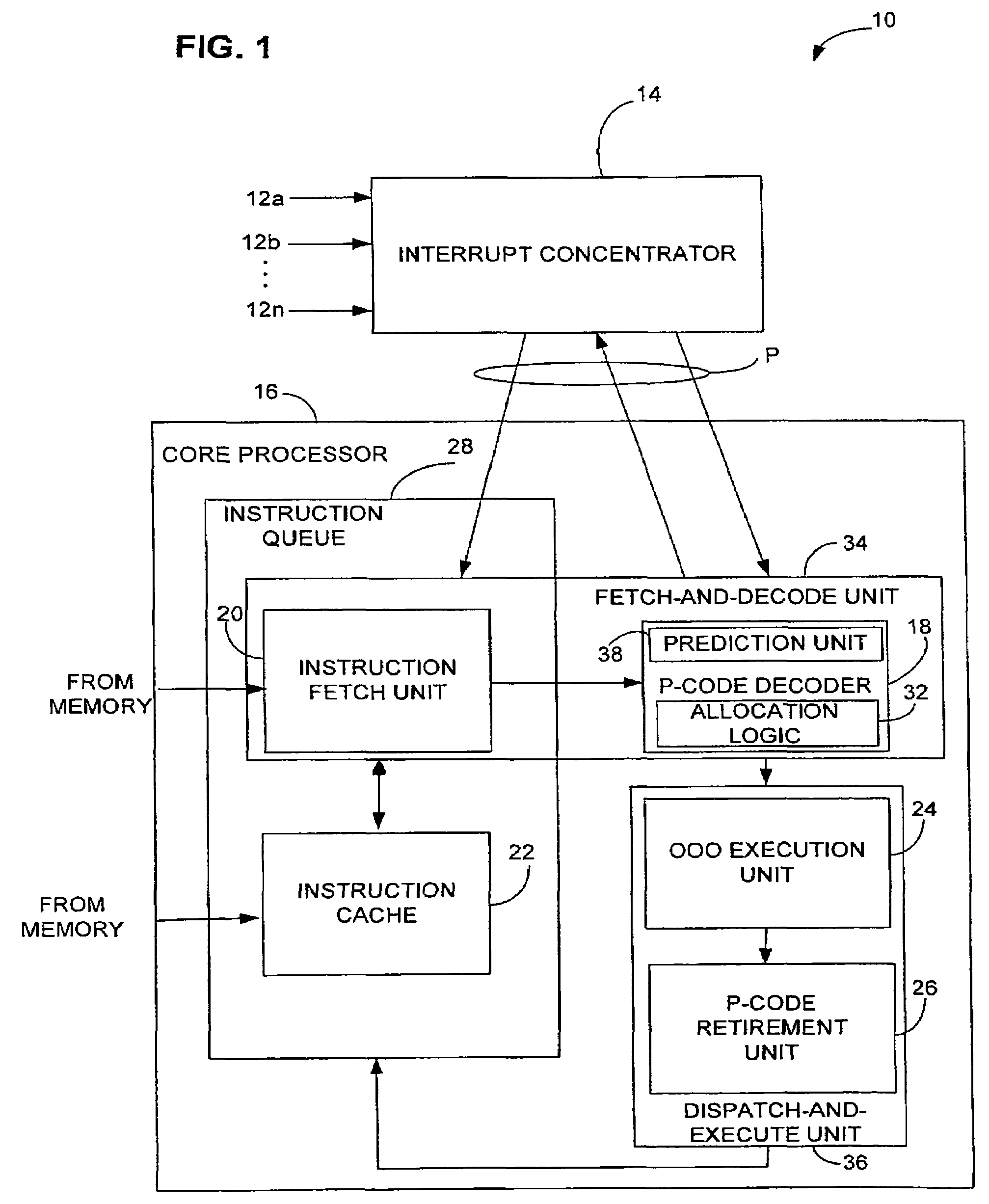

Allocation of processor bandwidth between main program and interrupt service instruction based on interrupt priority and retiring micro-ops to cache

InactiveUS7213137B2Program initiation/switchingResource allocationProcessing InstructionProgram instruction

The method and apparatus feature detecting an interrupt service request; storing into an instruction cache interrupt service instructions in response to detecting the interrupt service request; and fetching instructions from the instruction cache into an instruction stream sequence, the instruction stream sequence including mainline program instructions and the interrupt service instructions resulting in allocating core processor bandwidth between the interrupt servicing and mainline program instructions while executing the instruction stream sequence based on an interrupt priority; and processing instructions within the instruction stream sequence including the mainline program instructions and the inserted interrupt servicing instructions. The method and apparatus further feature recycling of executed micro-ops and detecting imminent context switch for interrupt service instruction preparation.

Owner:INTEL CORP

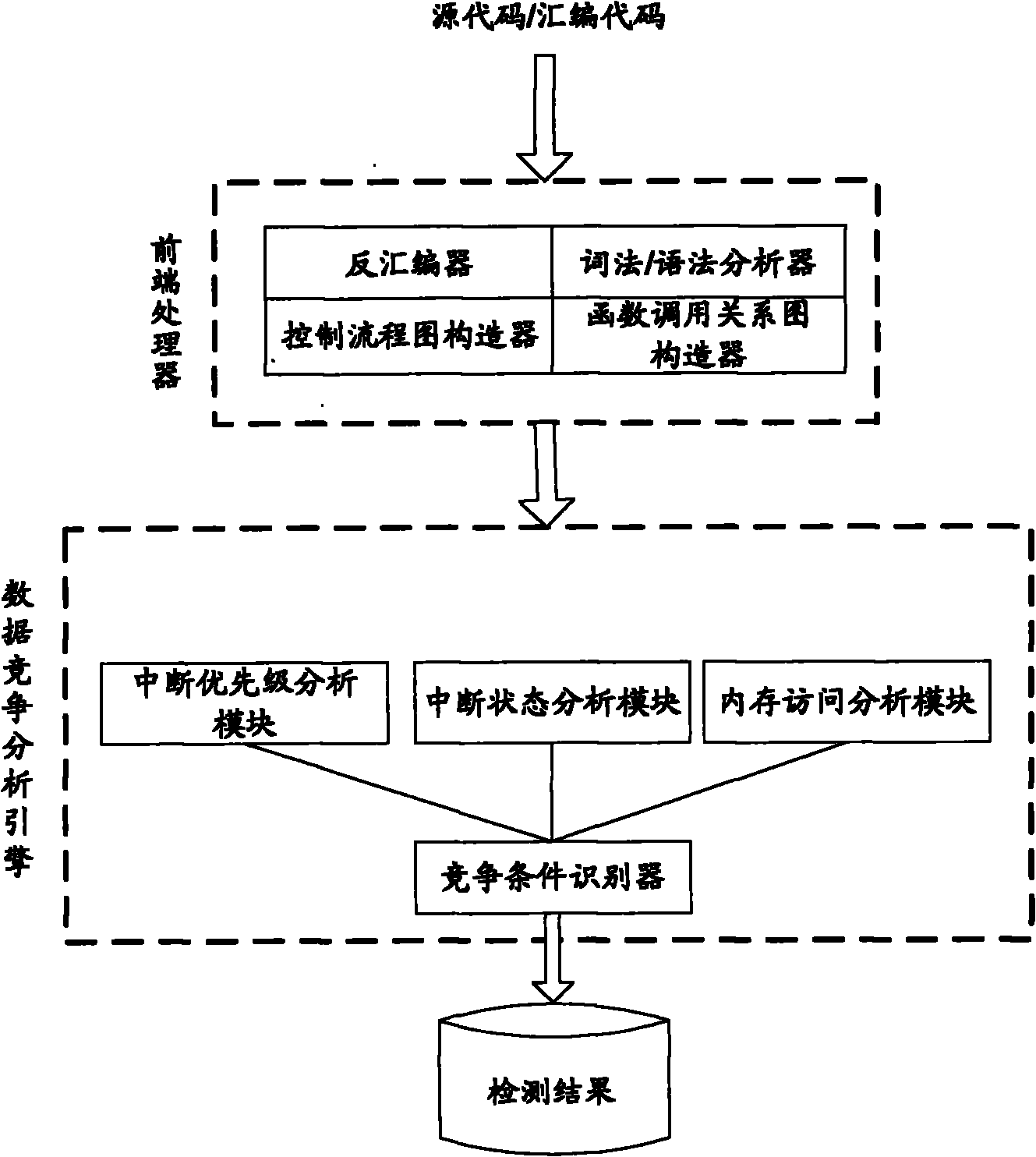

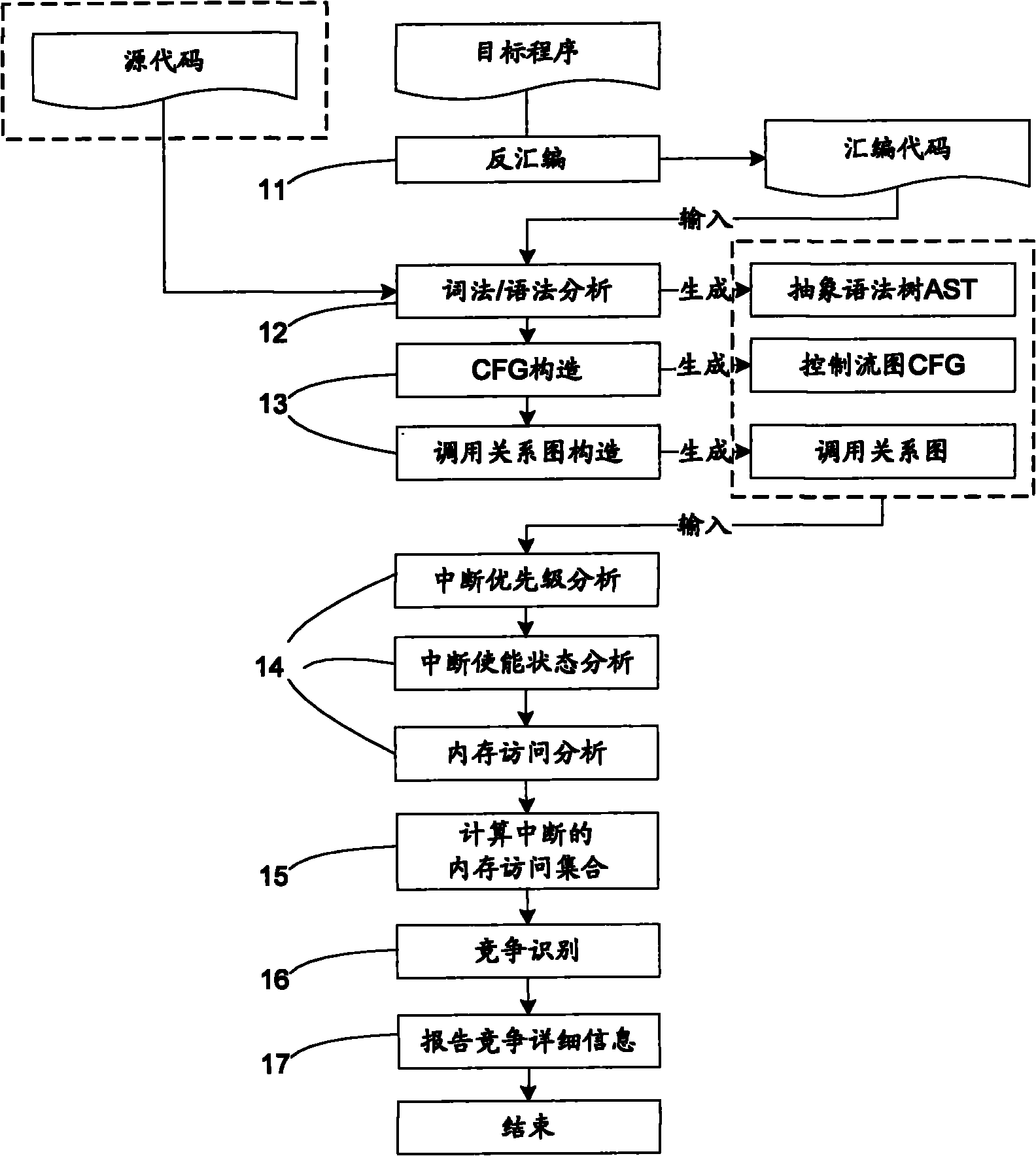

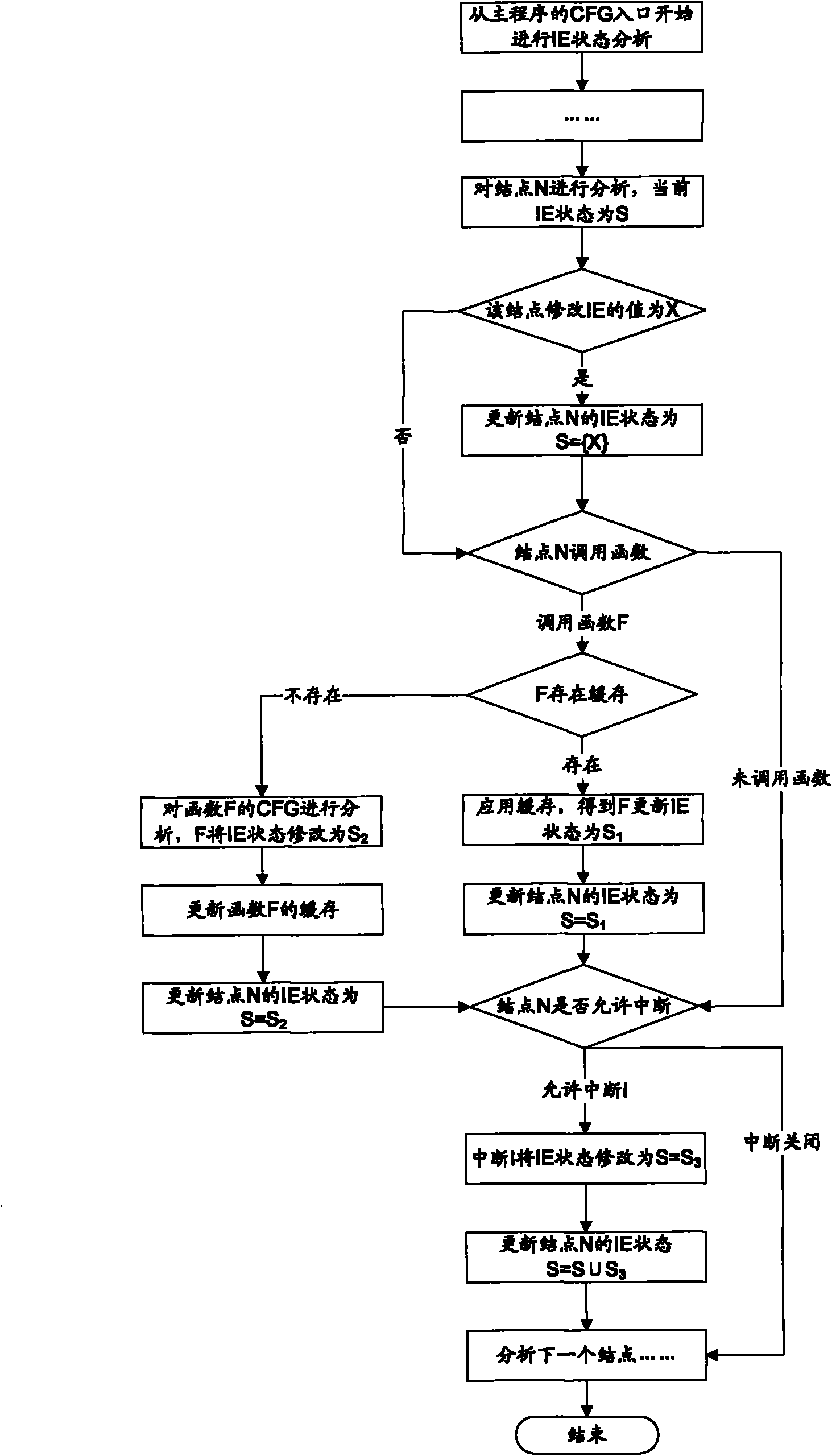

System for detecting interrupt-driven type program data competition

ActiveCN102063328AReduce false positivesHigh degree of automationMultiprogramming arrangementsSoftware developmentSyntax

The invention discloses a system for detecting interrupt-driven type program data competition, which comprises a front-end processor and a data race analysis engine, wherein the front-end processor comprises a disassembler, a morphology / syntax analyzer, a control flow graph constructor and a function call relation graph constructor, and the data race analysis engine comprises an interrupt priority analysis module, an interrupt state analysis module, a memory access analysis module and a race condition identifier. A static detection method is adopted in the invention, wherein a source code or assembly code is input; the detected program does not need to run; the method can be applied in the early stage of software development; the automaticity is high; and the interrupt enabled state is analyzed in iterative inter-process manner; through 'iteration', all the possible interrupt switching conditions can be extremely collected and the failed report of data race detection is reduced; and through 'inter-process', the function call and the influence of the interruption on the program state are regarded and the detection accuracy and the detection efficiency are increased.

Owner:BEIJING INST OF CONTROL ENG

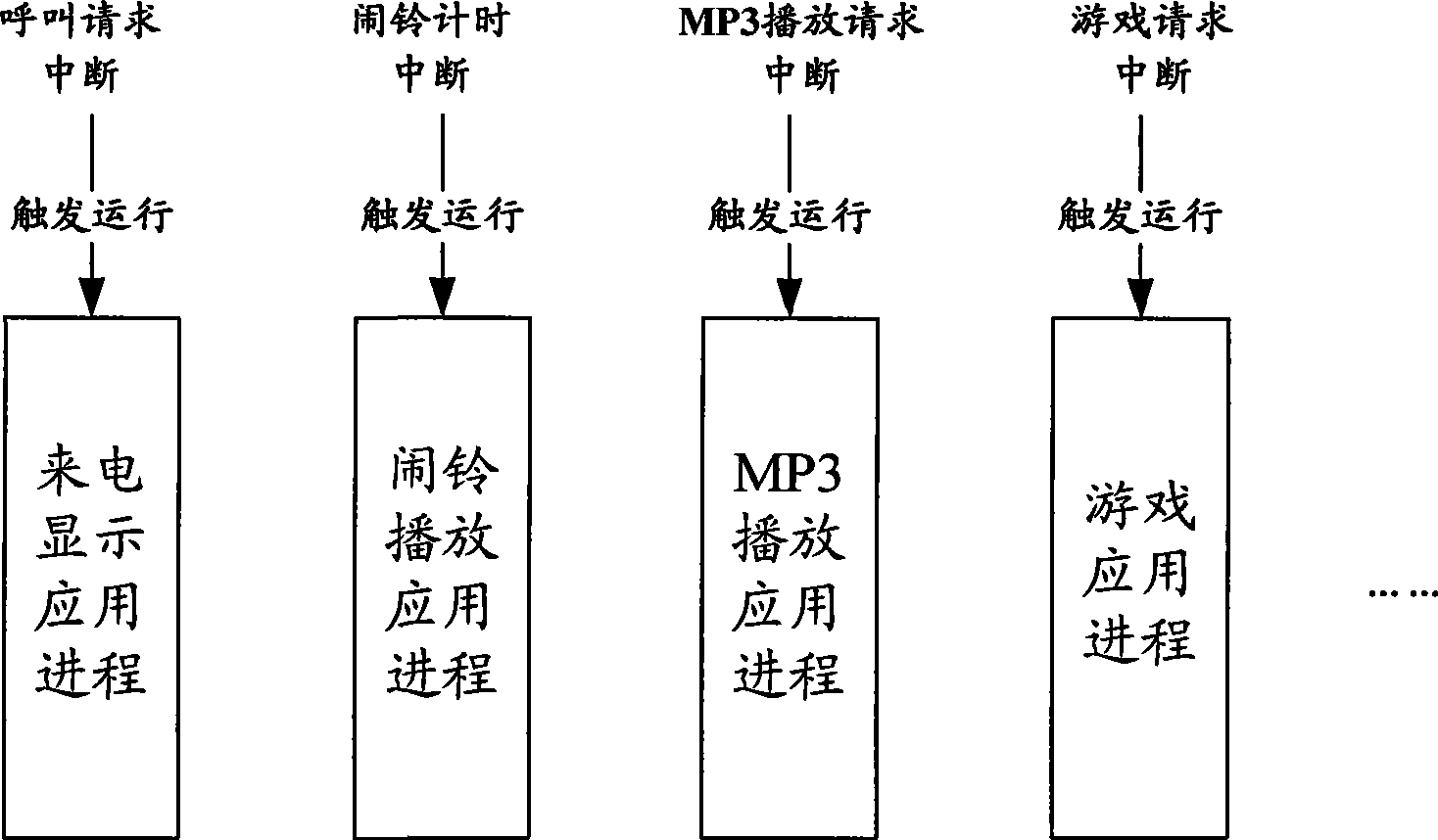

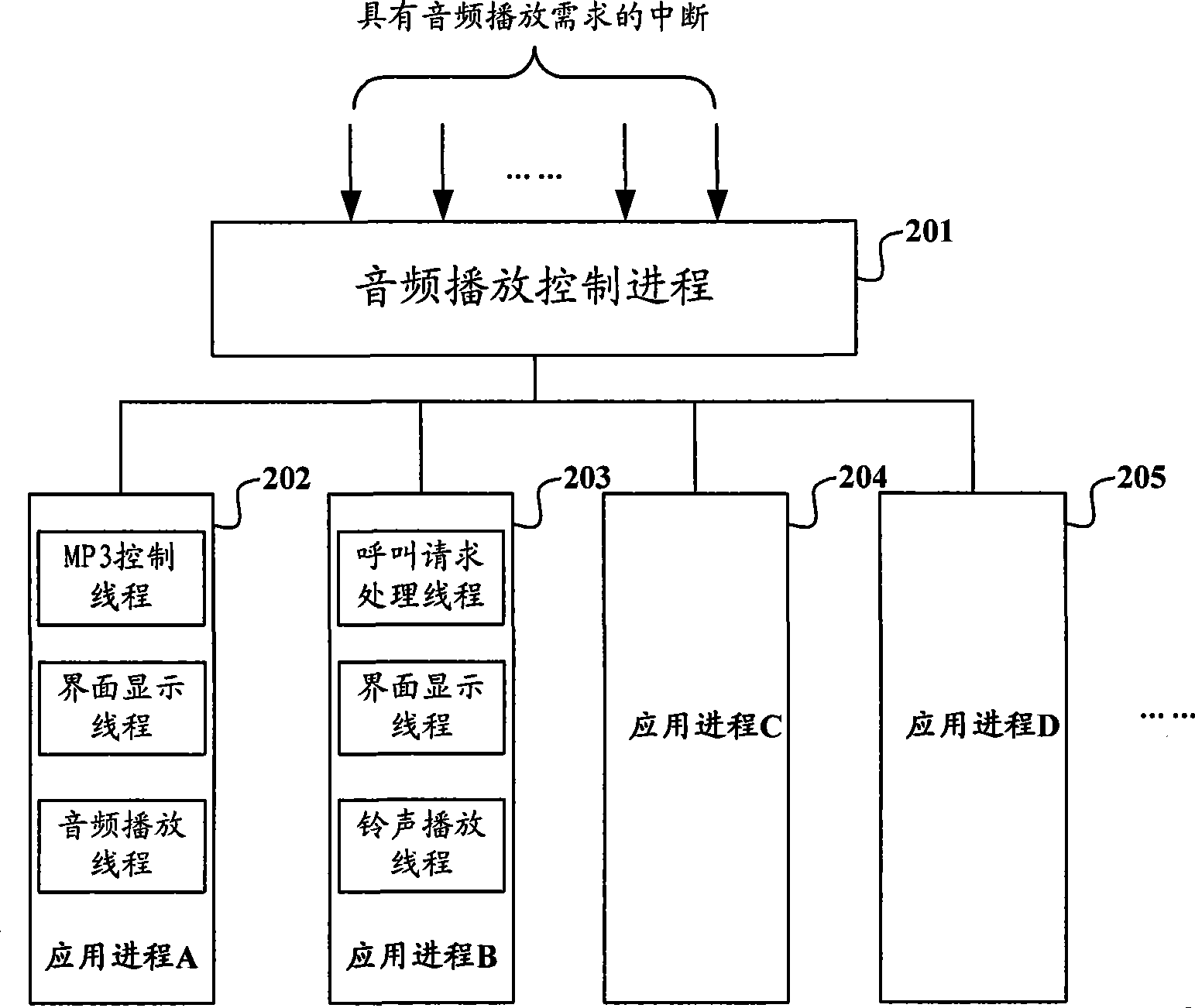

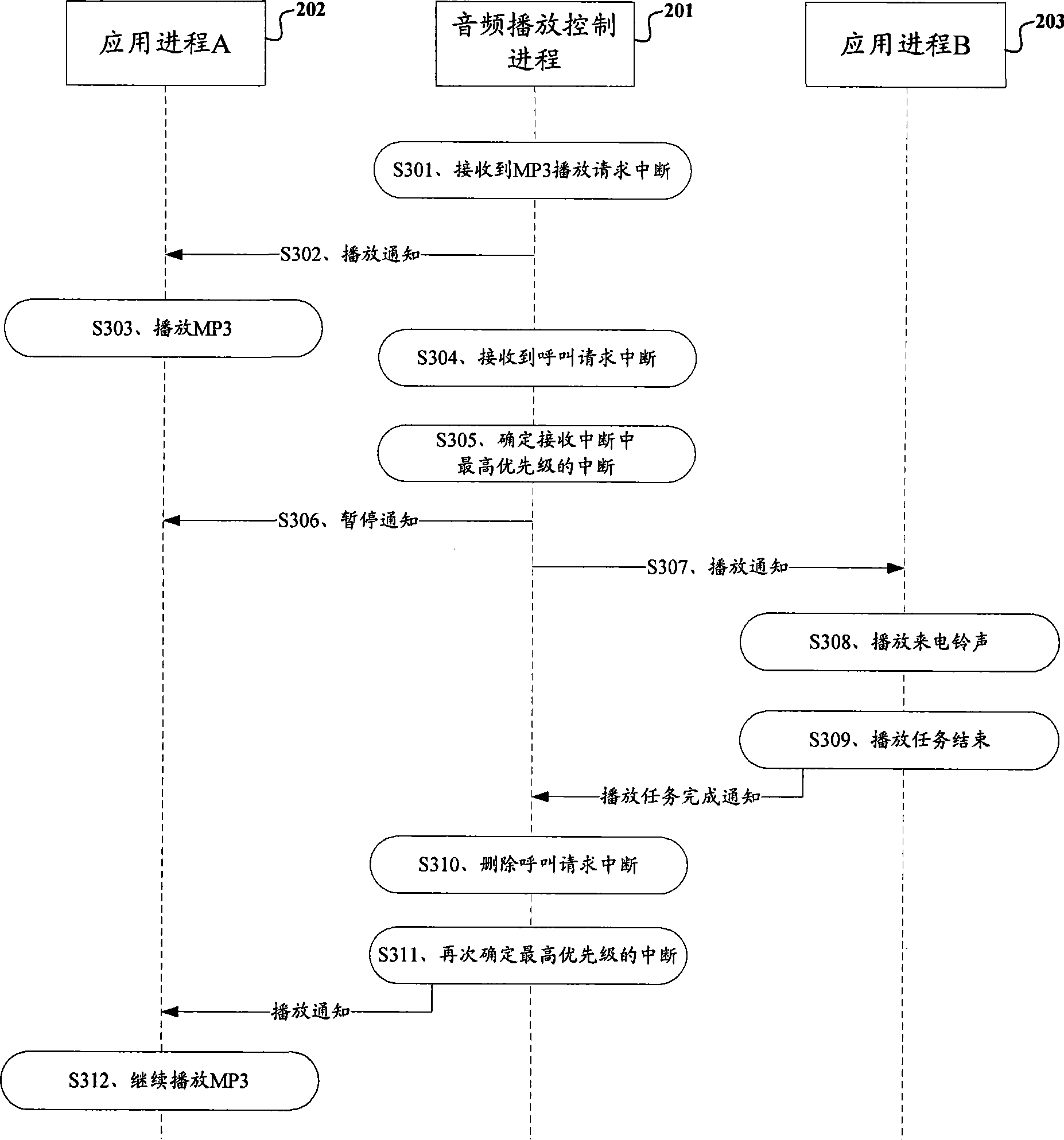

Mobile terminal and multimedia playing control method thereof

InactiveCN101364188AQuick responseImprove playback efficiencyProgram initiation/switchingSubstation equipmentEmbedded systemInterrupt priority level

The invention relates to the multimedia field, in particular to the technology for improving the multimedia displaying efficiency of a mobile terminal. A mobile terminal and a multimedia displaying control method thereof comprise the following steps: the multimedia displaying control process of the mobile terminal receives interrupt with multimedia displaying demands, firstly inform application process corresponding to the interrupt with high priority level of carrying out multimedia displaying according to the priority level of the interrupt prearranged, and inform application process corresponding to other interrupt of stopping multimedia displaying. Because the multimedia displaying control process of the mobile terminal is adopted to receive various interrupt with multimedia displaying demands, application process corresponding to interrupt with the highest priority level firstly carries out multimedia displaying, thereby avoiding the conflict caused by a plurality of application process for preempting the resources of a system when a plurality of interrupt with multimedia displaying demands reach simultaneously, improving the multimedia displaying efficiency of the mobile terminal, and accelerating response speed.

Owner:QINGDAO HISENSE MOBILE COMM TECH CO LTD

Method and apparatus for prioritizing interrupts in a communication system

InactiveUS6553443B1Multiplex system selection arrangementsElectric digital data processingCommunications systemEmbedded system

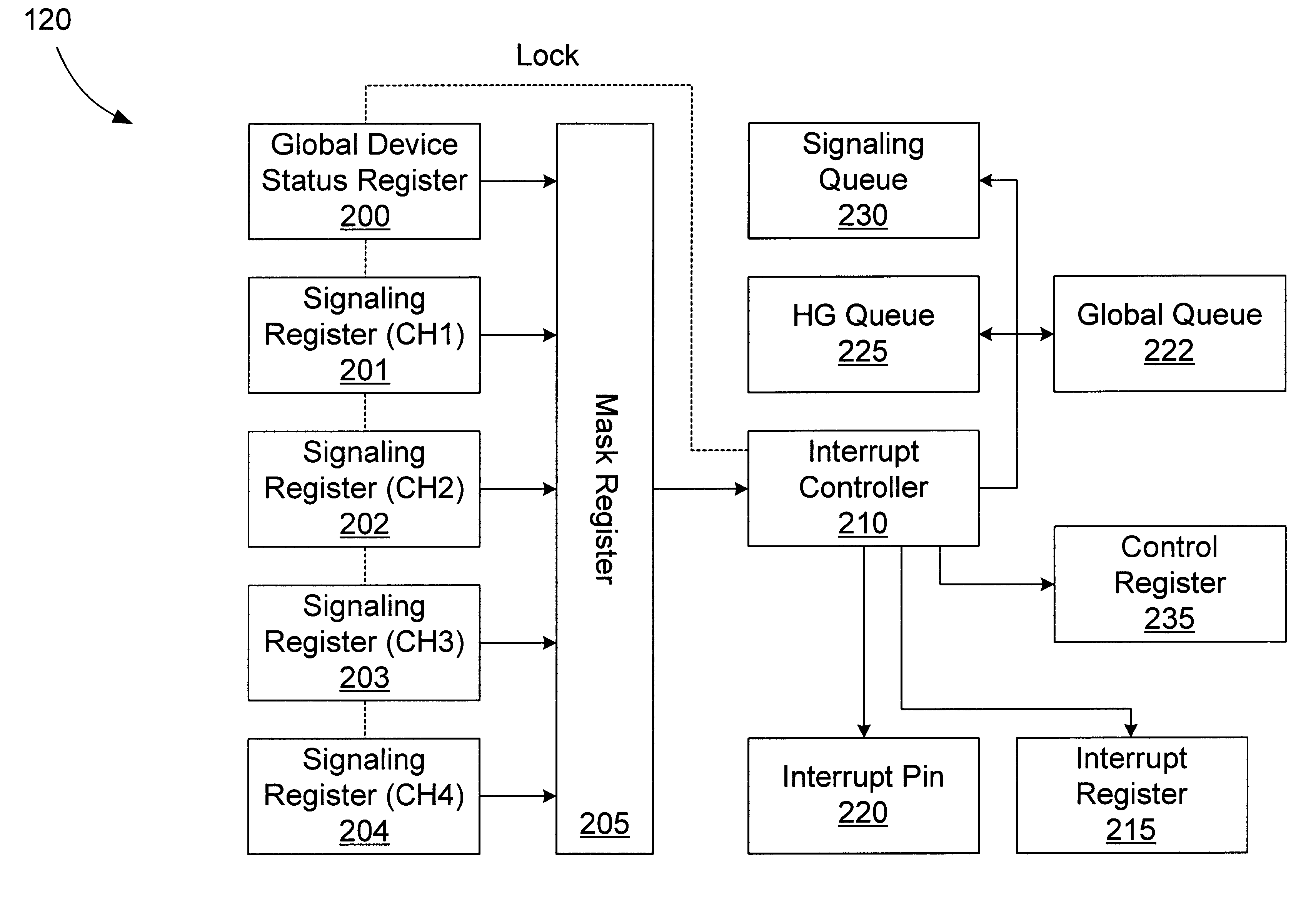

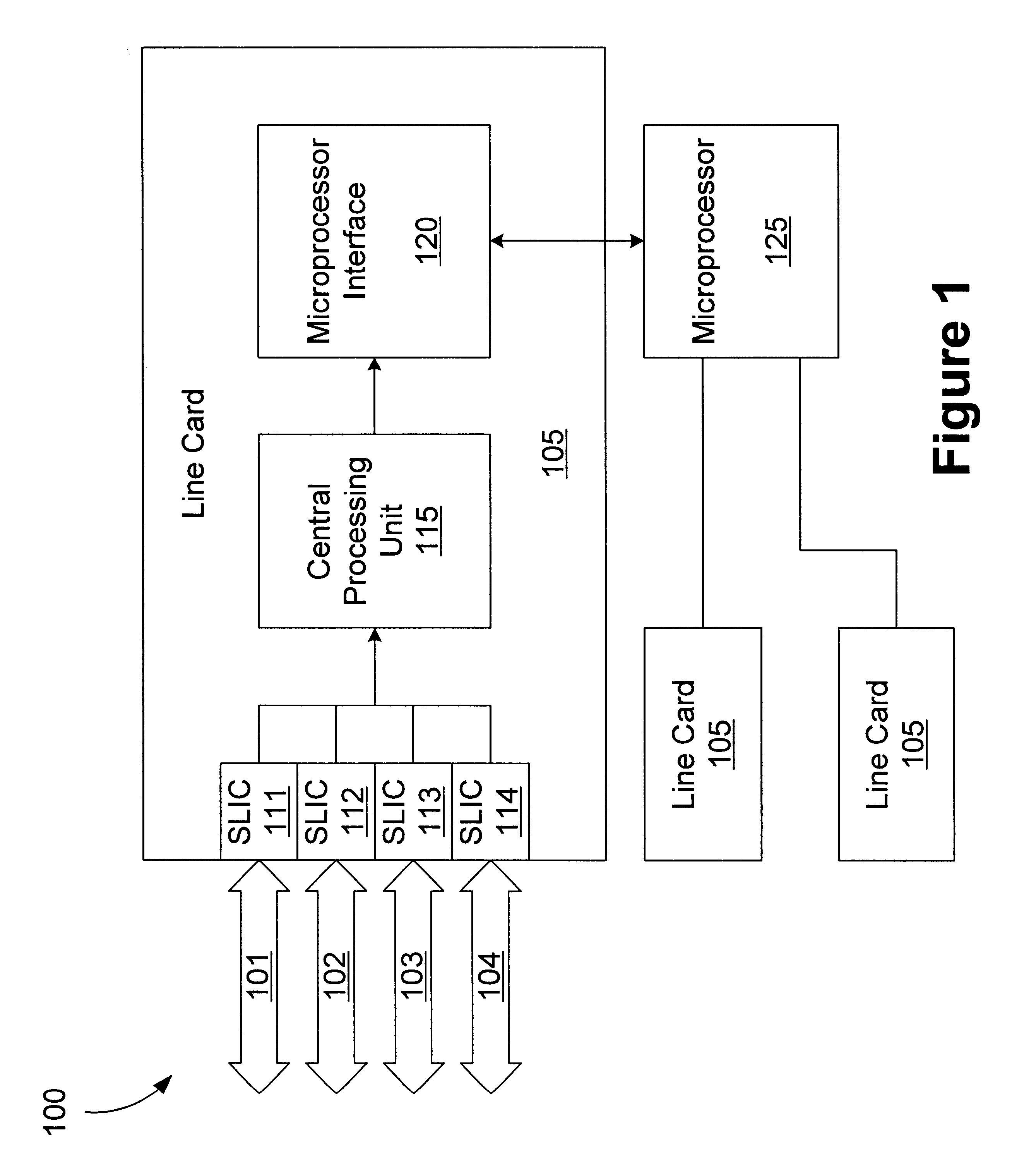

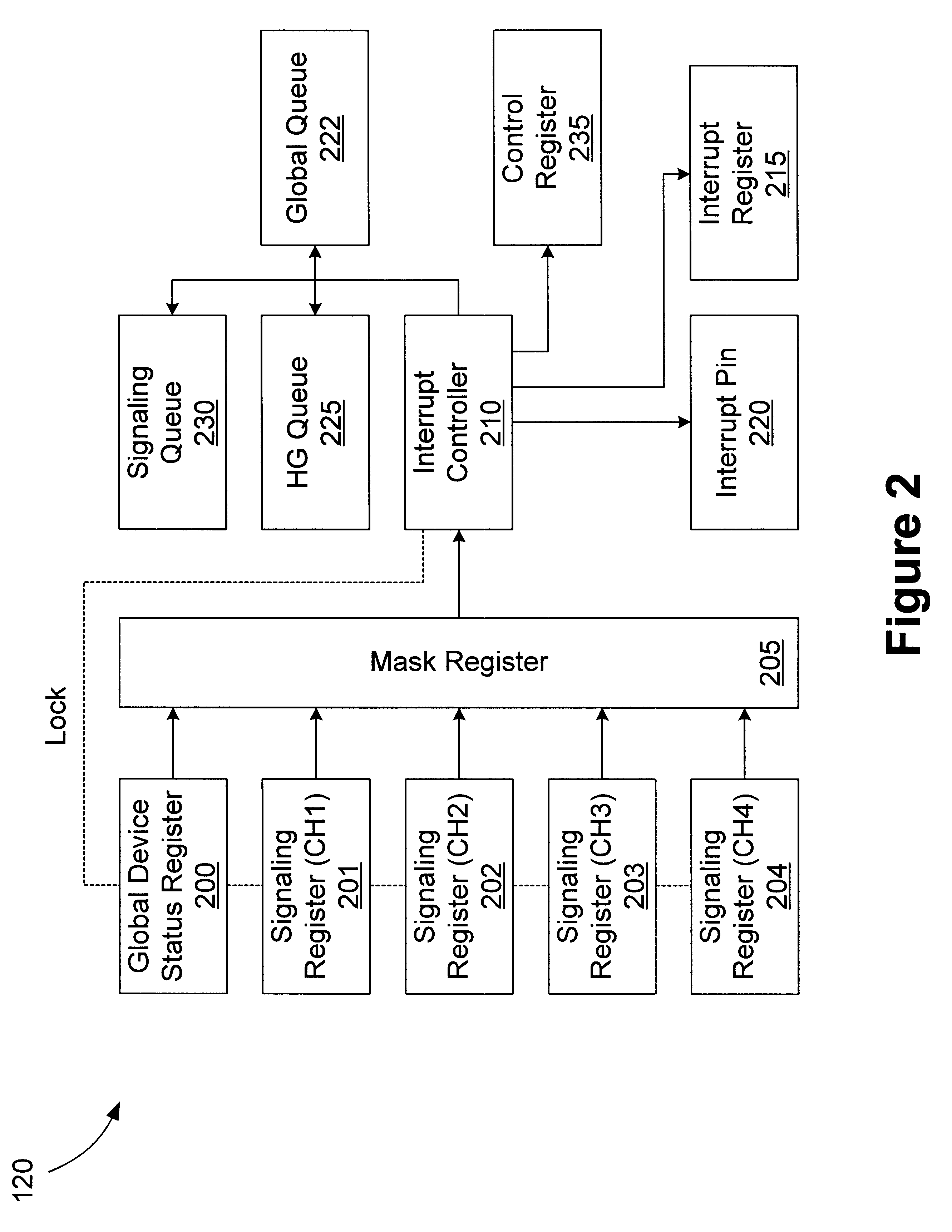

A communications system includes a communications channel, a first processing unit; and interface unit, and an interrupt controller. The first processing unit is adapted to monitor the communications channel and provide a plurality of status bits. The interface unit includes an interrupt register. The interrupt controller is adapted to identify a plurality of interrupts in response to changes in the status bits. Each interrupt has a priority, and the interrupt controller is adapted to store selected interrupts in the interrupt register in an order determined by the priority of the interrupts. A method includes monitoring a communications channel. A plurality of status bits associated with the monitoring are provided. A plurality of interrupts are identified based on changes in the status bits, each interrupt having a priority. Selected interrupts are stored in an interrupt queue in an order determined by the priority of the interrupts.

Owner:MICROSEMI SEMICON U S

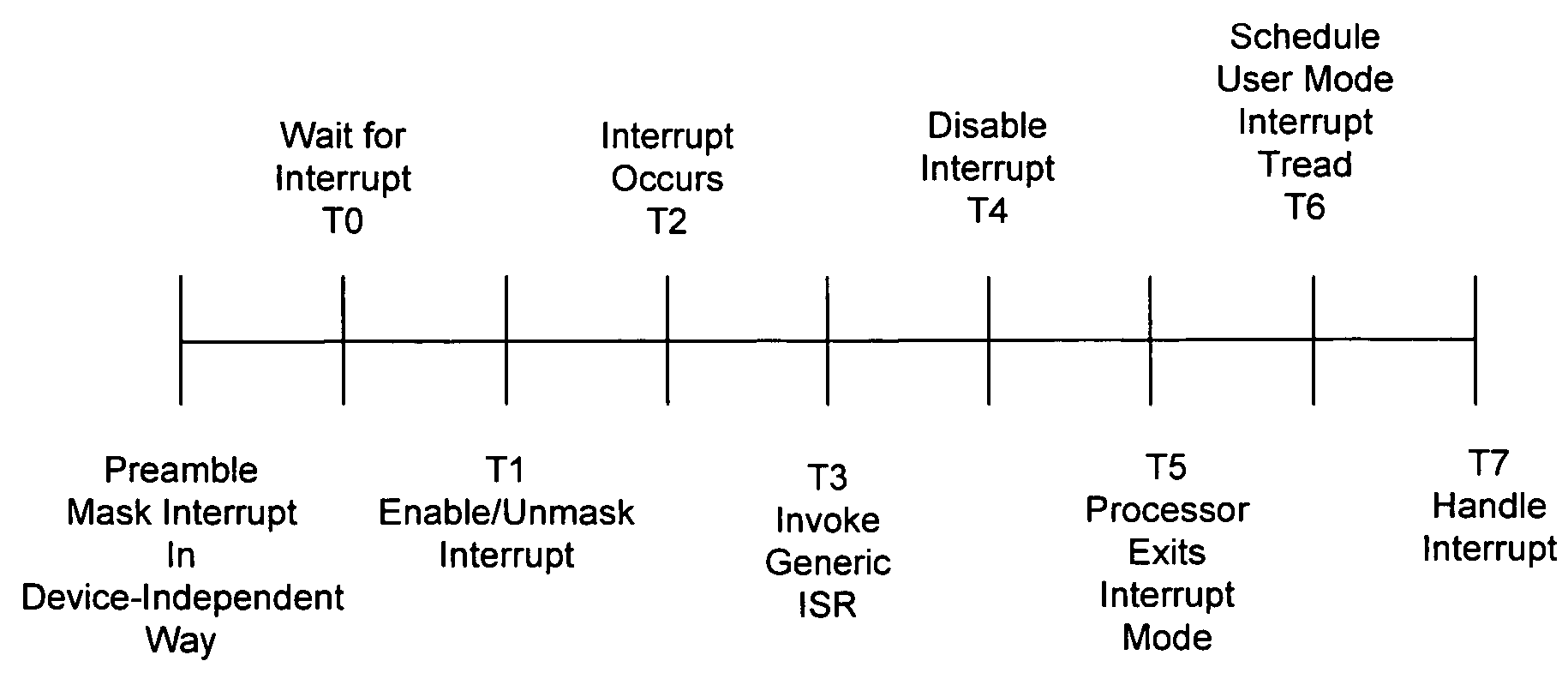

Method for delivering interrupts to user mode drivers

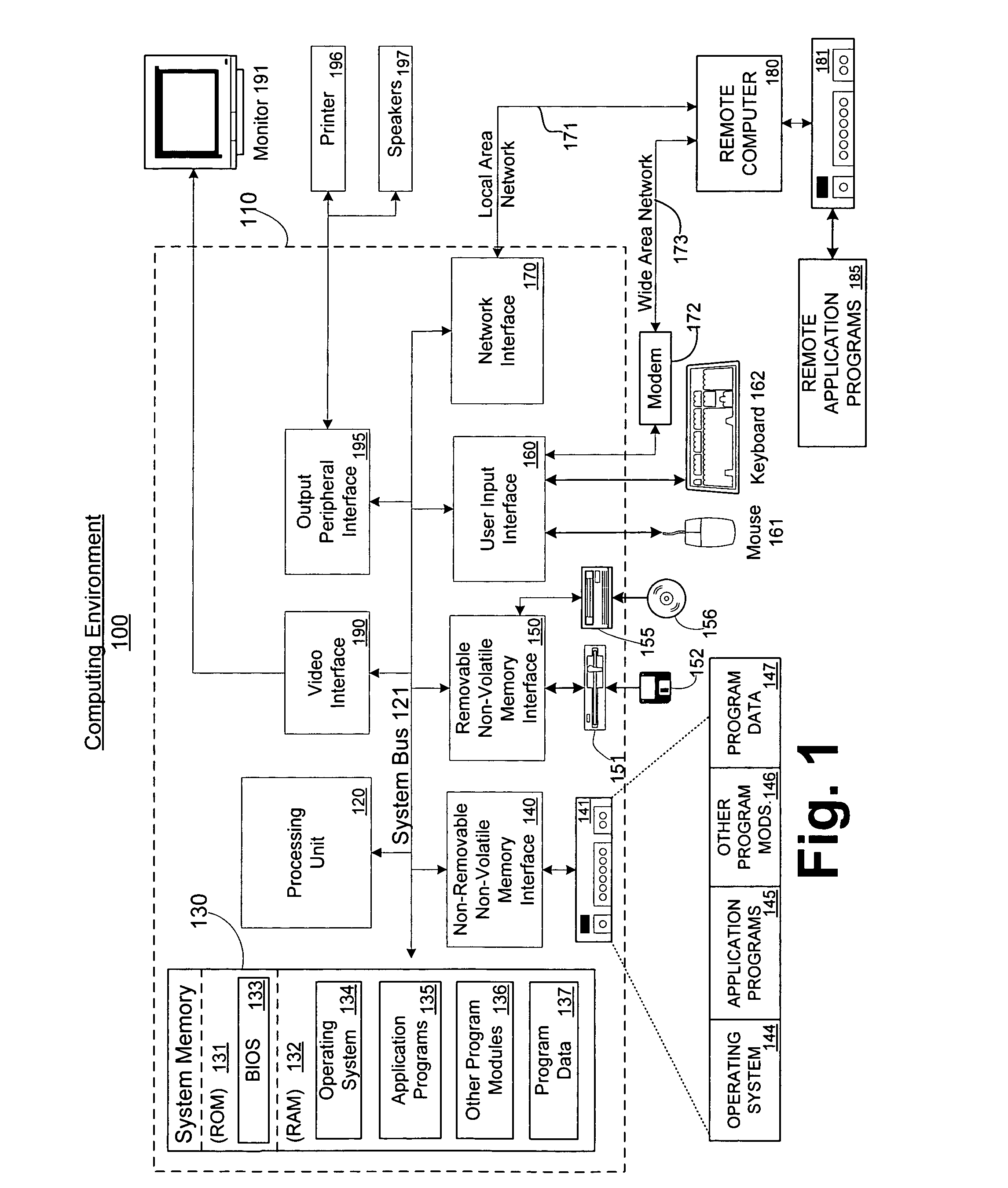

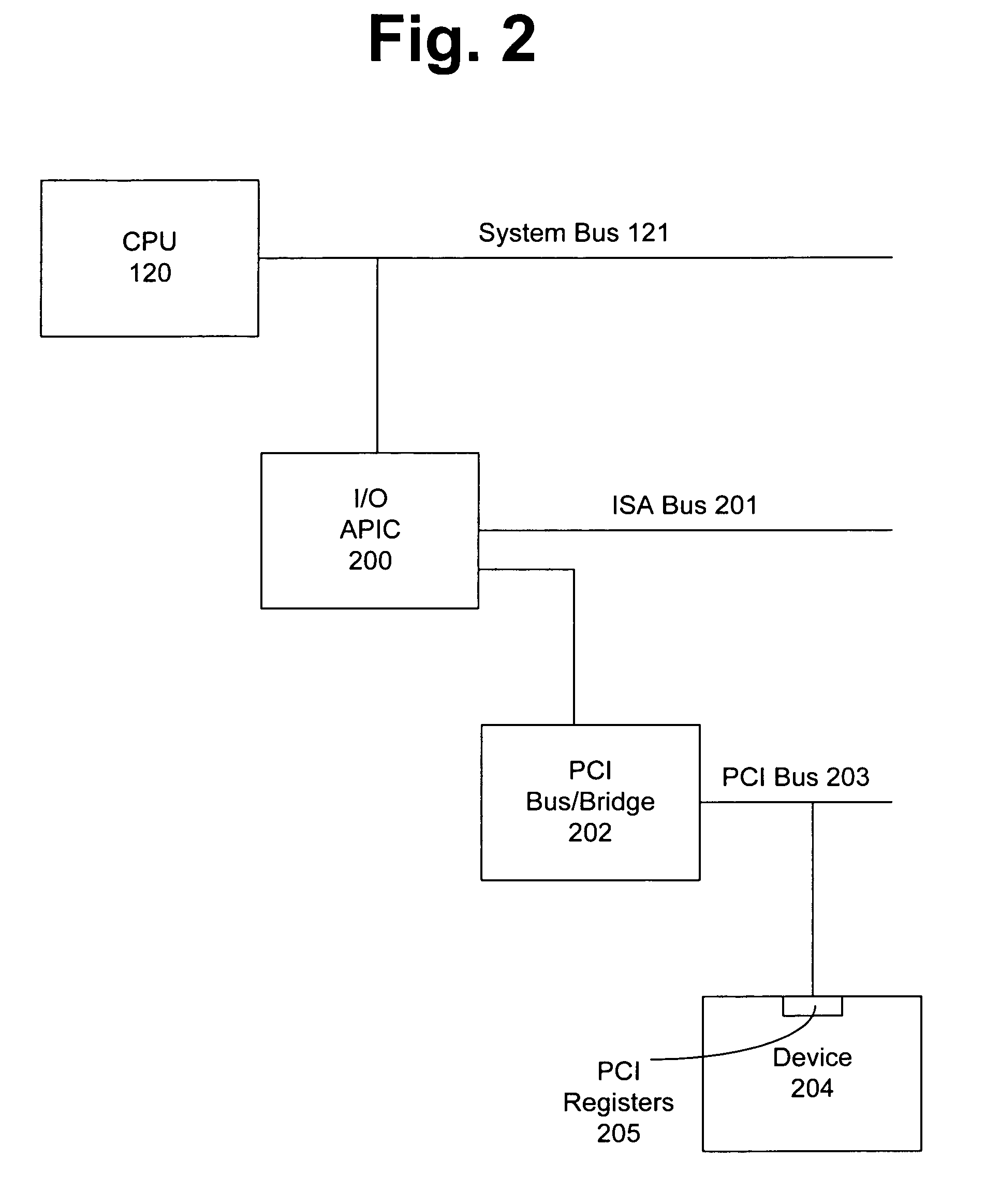

Systems and methods for providing a framework within which device drivers may run at a user-mode level. A platform (e.g., APIC) or bus (PCI bus) generic feature is used to take the CPU out of interrupt mode without having to wait for a user-level driver to clear the device interrupt. This allows writing the complete device driver in user space. The device driver still get notifications on interrupts but not at interrupt priority. The same scheme can be extended to shared interrupts, where multiple devices share a single interrupt line.

Owner:MICROSOFT TECH LICENSING LLC

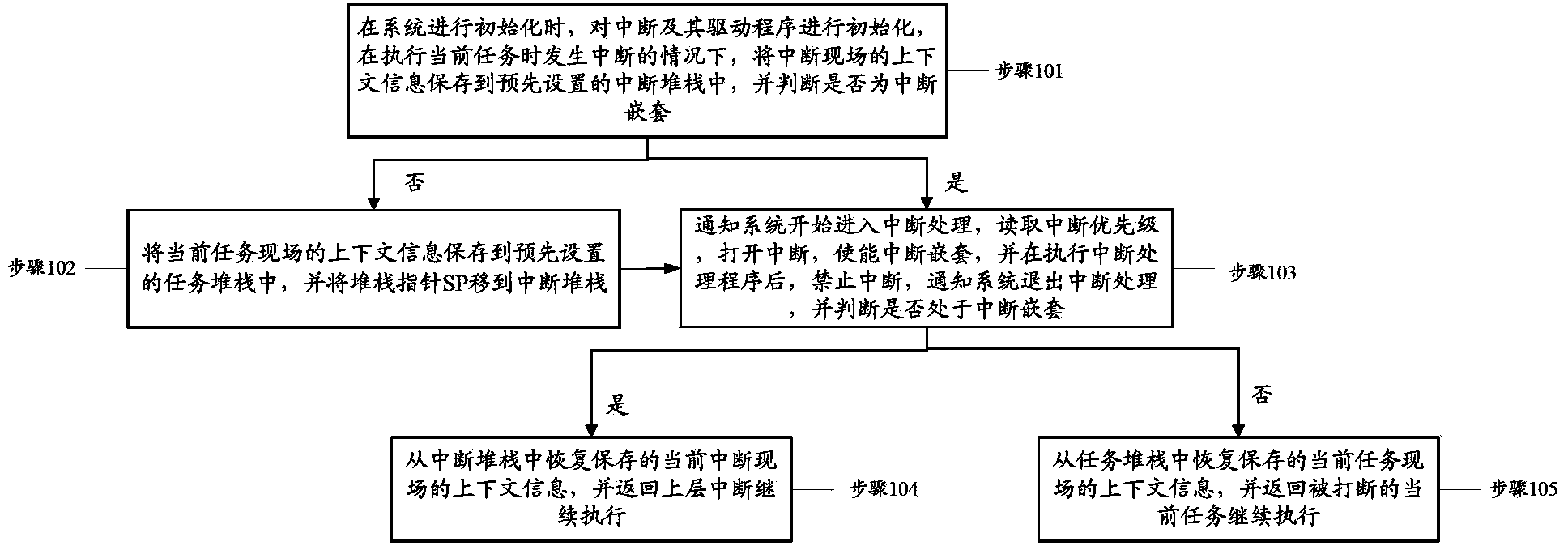

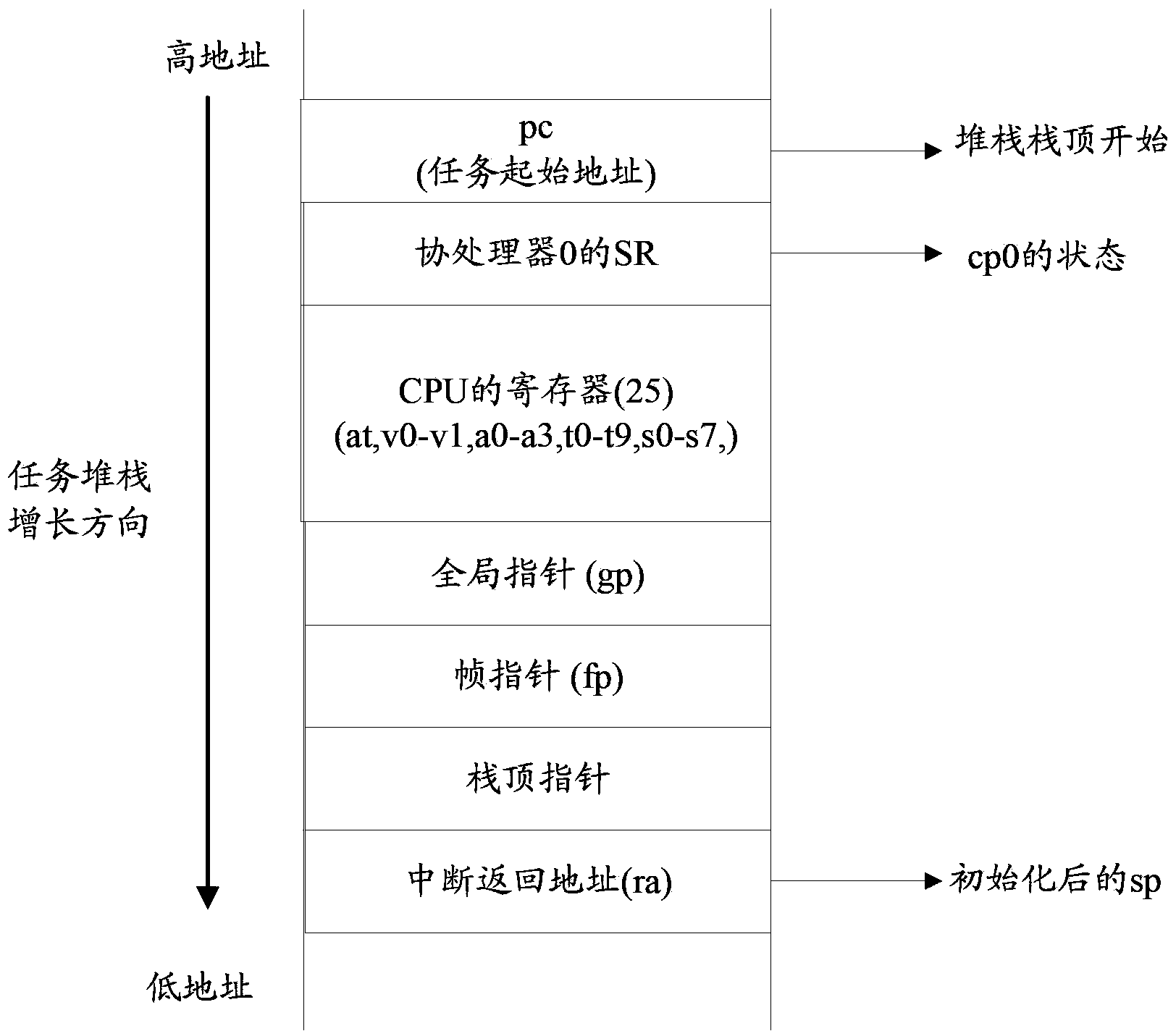

Interrupt processing method and device

InactiveCN103778009AImprove efficiencyReduce memory size requirementsProgram initiation/switchingEmbedded systemNotification system

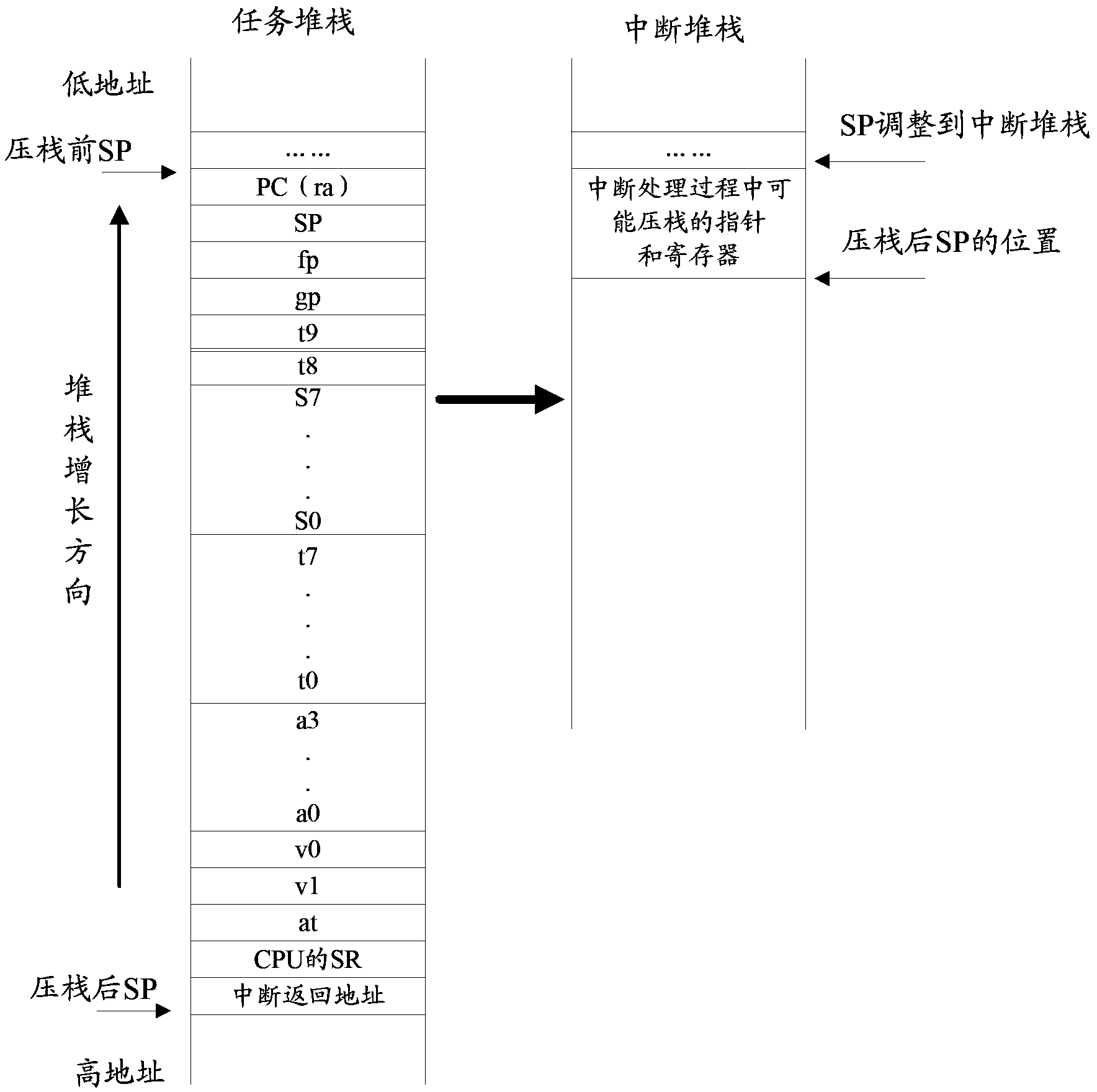

The invention discloses an interrupt processing method and device. The method comprises the steps of step 1, initializing interrupt and the drive program of the interrupt when a system is initialized, and when the interrupt occurs during execution of a current task, storing the context information of the interrupt field into a preset task stack and determining whether the interrupt is a interrupt nesting; step 2, storing the context information of a current task field into the preset task stack and moving a stack pointer (SP) to an interrupt stack; step 3, informing the system to start entering interrupt processing, reading interrupt priority levels, opening the interrupt, enabling the interrupt nesting, and after executing an interrupt processing program, prohibiting the interrupt, informing the system to exit the interrupt processing and determining whether the system is in the interrupt nesting; step 4, recovering the context information of the stored current interrupt field and returning to upper-layer interrupt; step 5, recovering the context information of the stored current task field and returning to the current task.

Owner:SANECHIPS TECH CO LTD

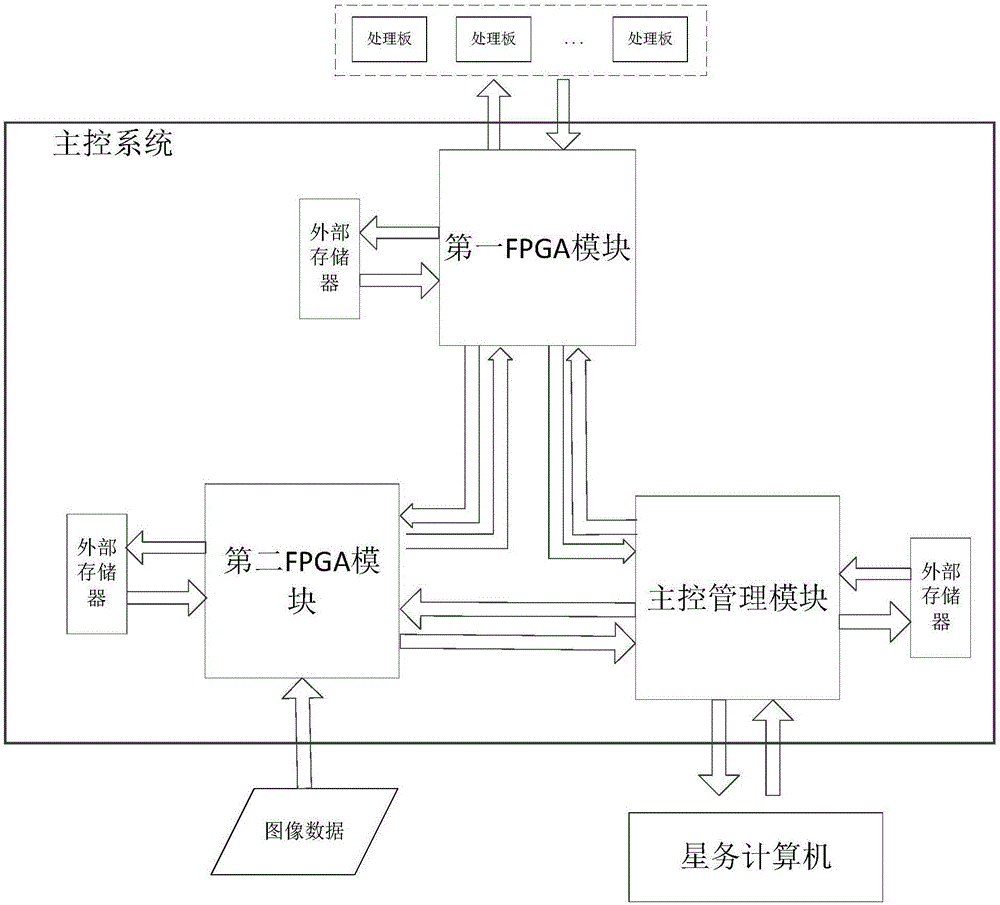

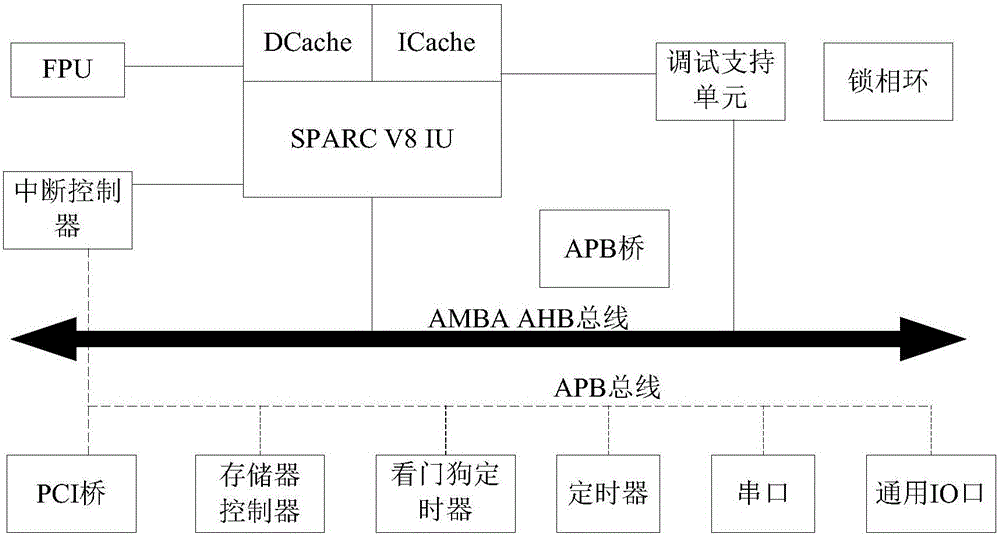

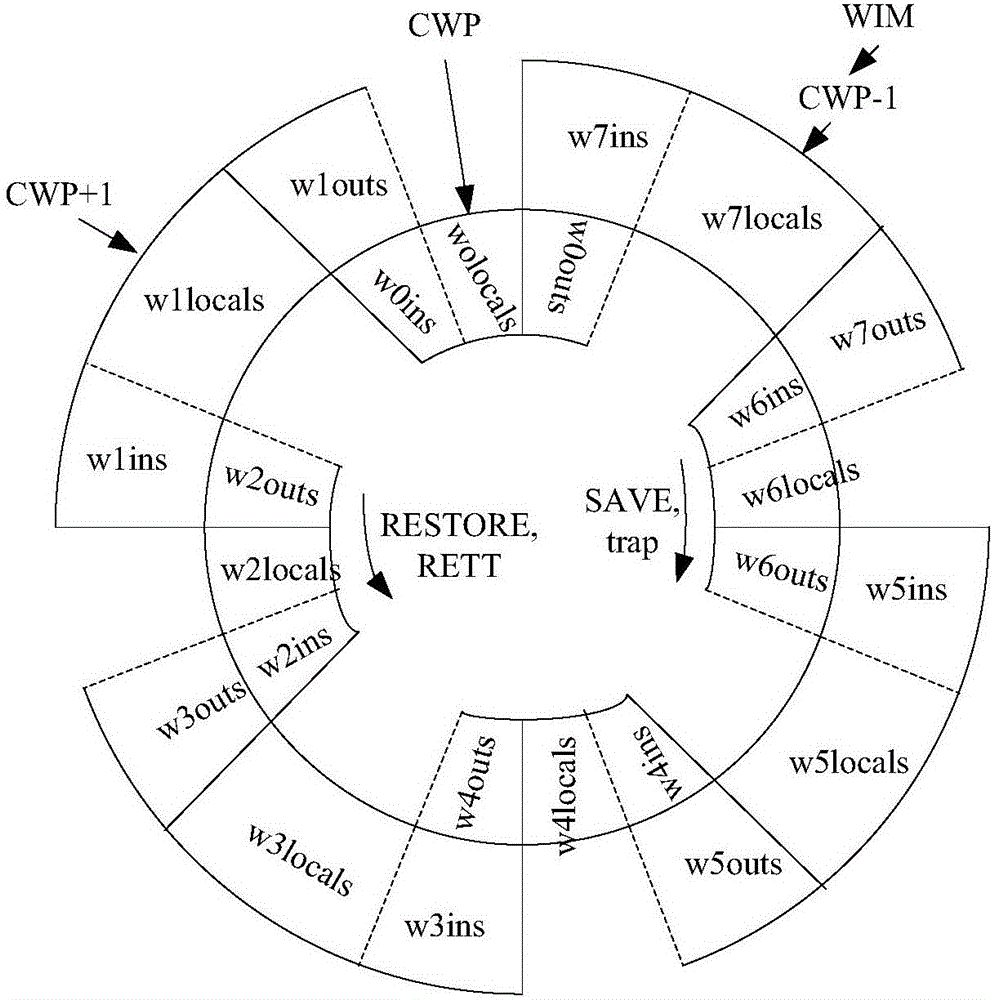

Multi-task master control system for remote sensing satellite image processing load

ActiveCN106843038ARealize monitoringRealize managementProgramme controlImage analysisSatellite image processingStructure of Management Information

The invention discloses a multi-task master control system for a remote sensing satellite image processing load. A CPU+2FPGA framework is adopted, wherein an embedded real-time operating system is transplanted into a CPU to serve as a master control management module for completing state monitoring and task scheduling of the remote sensing satellite image processing load, which has high flexibility, safety and stability; an FPGA can overcome the defects of the CPU with different interrupt priority levels and limited interrupt vector tables under multiple time sequence interfaces when used for integrating and issuing communication information, and can meet the requirements for real-time performance and low delay under a large data size when used for preprocessing images. The system structure design can effectively achieve the master control management function, meet the requirements for highly parallel processing of images and operation of complex floating-point numbers, and meet the requirements for safety, reliability and high flexibility of the system.

Owner:HUAZHONG UNIV OF SCI & TECH

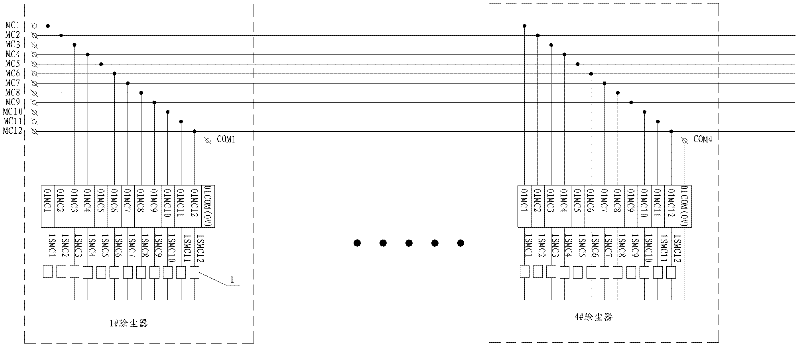

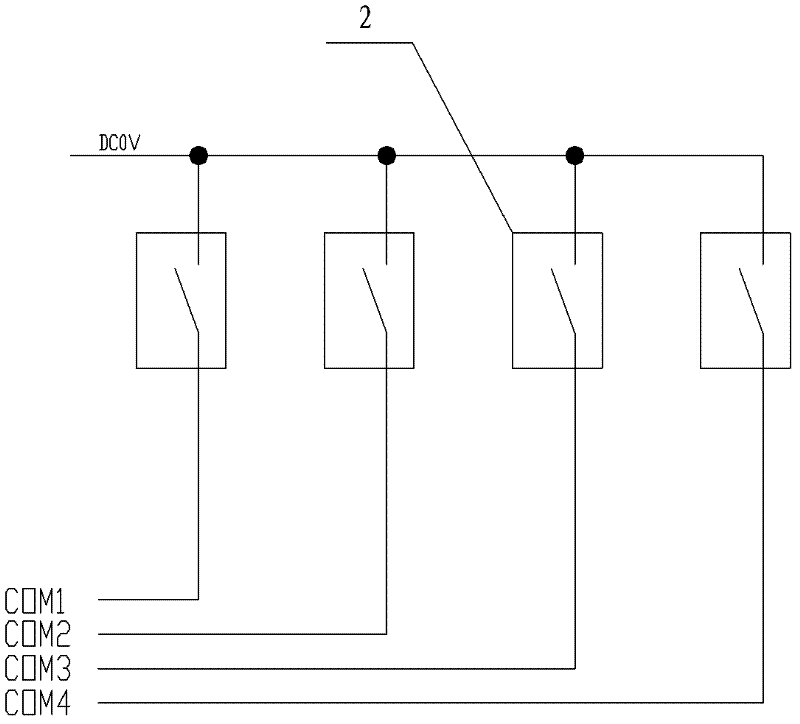

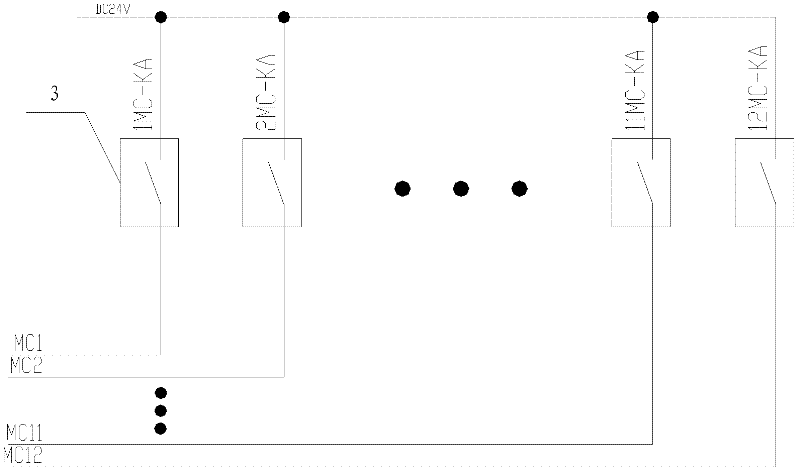

Automatic control method for small-sized bag type dust remover

InactiveCN102363090ARealize the memory functionRealize jump cleaningDispersed particle filtrationOptimal controlInterrupt priority level

The invention provides an automatic control method for a small-sized bag type dust remover. The automatic control method comprises an interval jump dust removing process of the dust remover, a dust discharging control process of the dust remover, a centralized overhaul control process and a centralized overhaul / automatic dust removing switch control process; the bag type dust remover is generally positioned in the interval jump dust removing process of the dust remover after the bag type dust remover is opened; interruption conditions of the centralized overhaul process are artificially set; and the interruption priority of the centralized overhaul control process is higher than other control processes. According to the automatic control method disclosed by the invention, any interval jump dust removal in the dust removing process of the small-sized bag type dust remover is realized; the optimal control over the dust removing process is realized; the memory function of the dust conveying and discharging process of the small-sized bag type dust remover is realized; and the reasonability and the safety of the dust conveying and discharging process are ensured.

Owner:浙江文国重工机械有限公司

Scheduling threads in a multiprocessor computer

Methods, systems, and computer program products are provided for scheduling threads in a multiprocessor computer. Embodiments include selecting a thread in a ready queue to be dispatched to a processor and determining whether an interrupt mask flag is set in a thread control block associated with the thread. If the interrupt mask flag is set in the thread control block associated with the thread, embodiments typically include selecting a processor, setting a current processor priority register of the selected processor to least favored, and dispatching the thread from the ready queue to the selected processor. In some embodiments, setting the current processor priority register of the selected processor to least favored is carried out by storing a value associated with the highest interrupt priority in the current processor priority register.

Owner:INT BUSINESS MASCH CORP

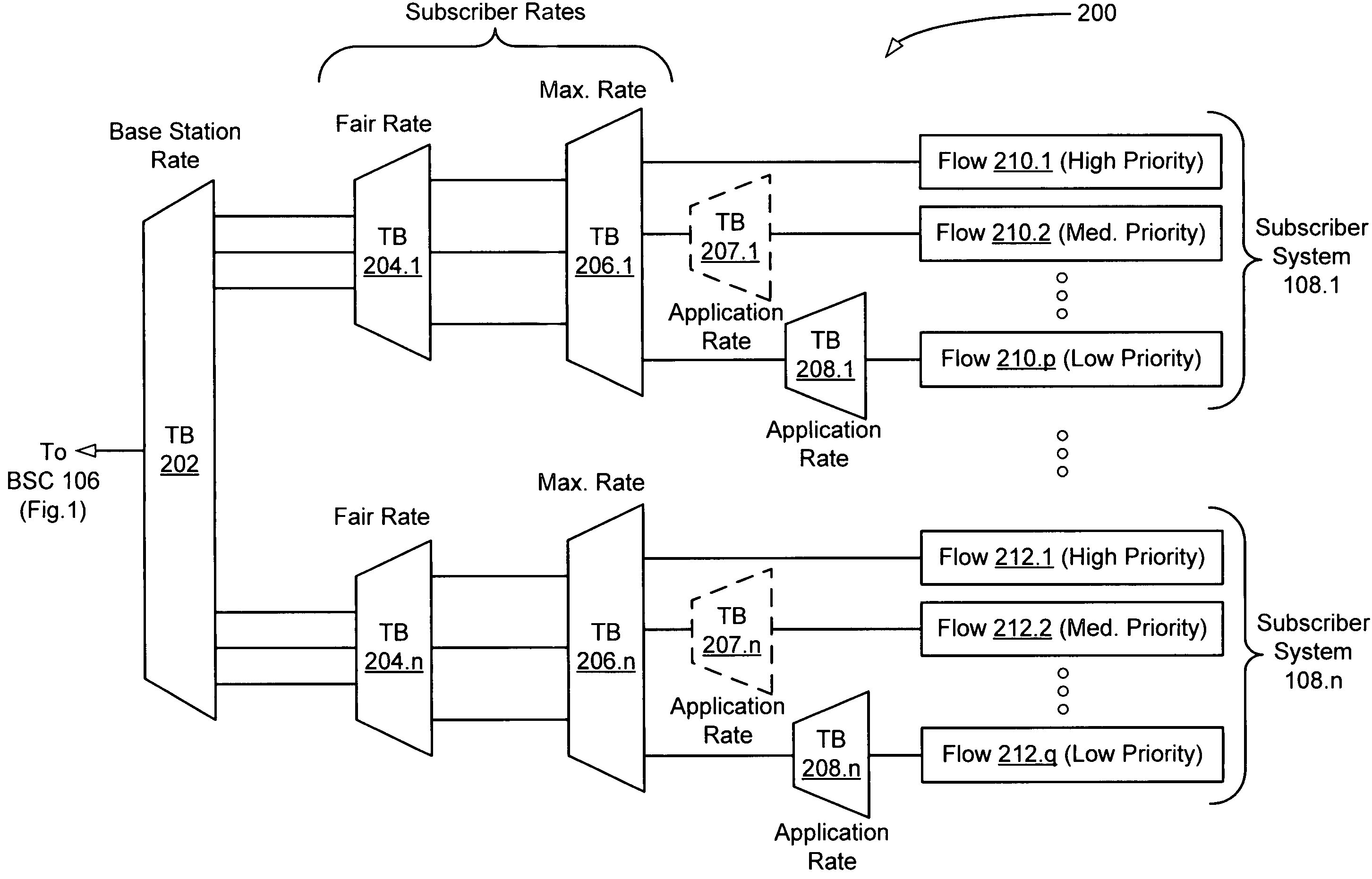

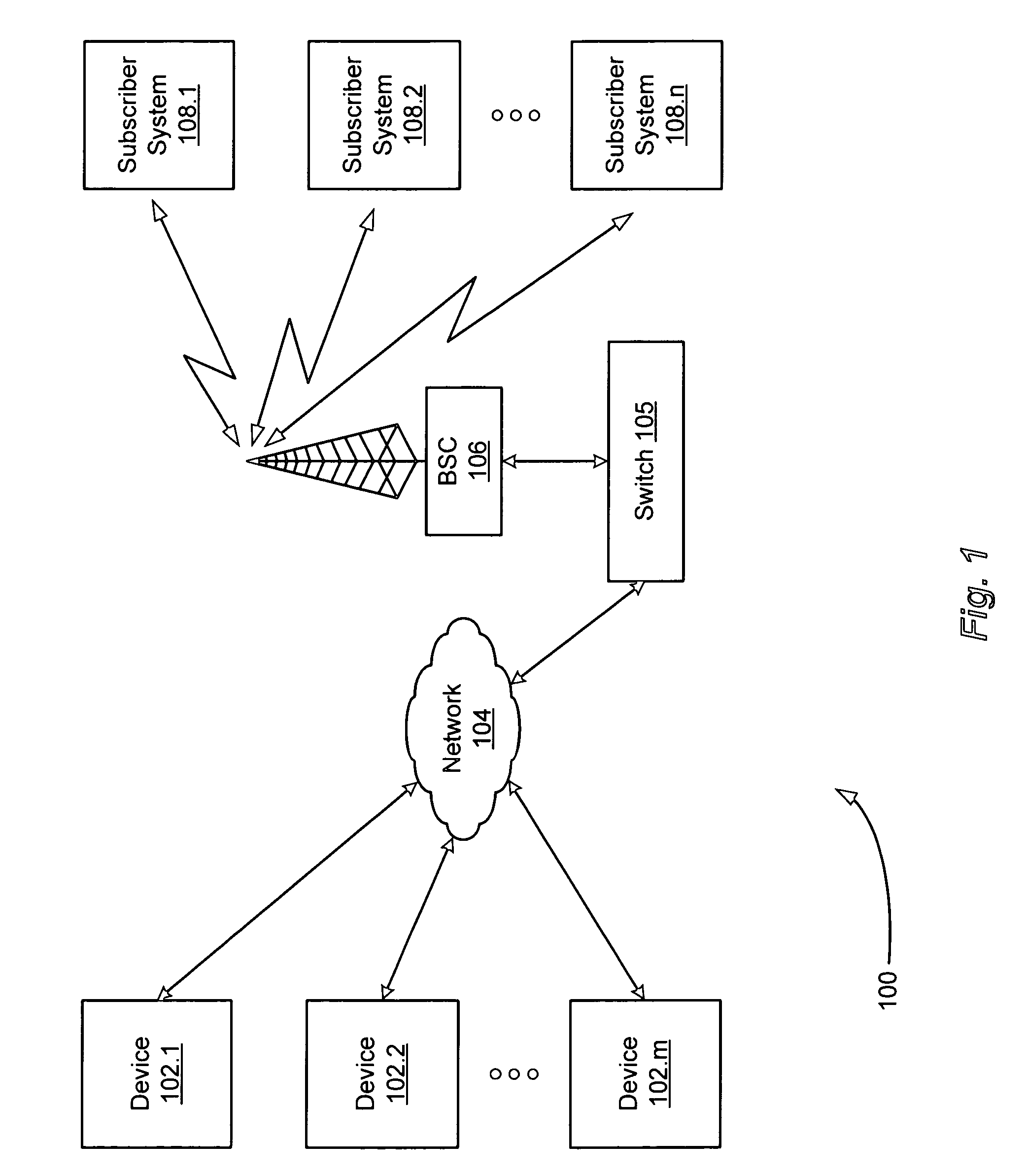

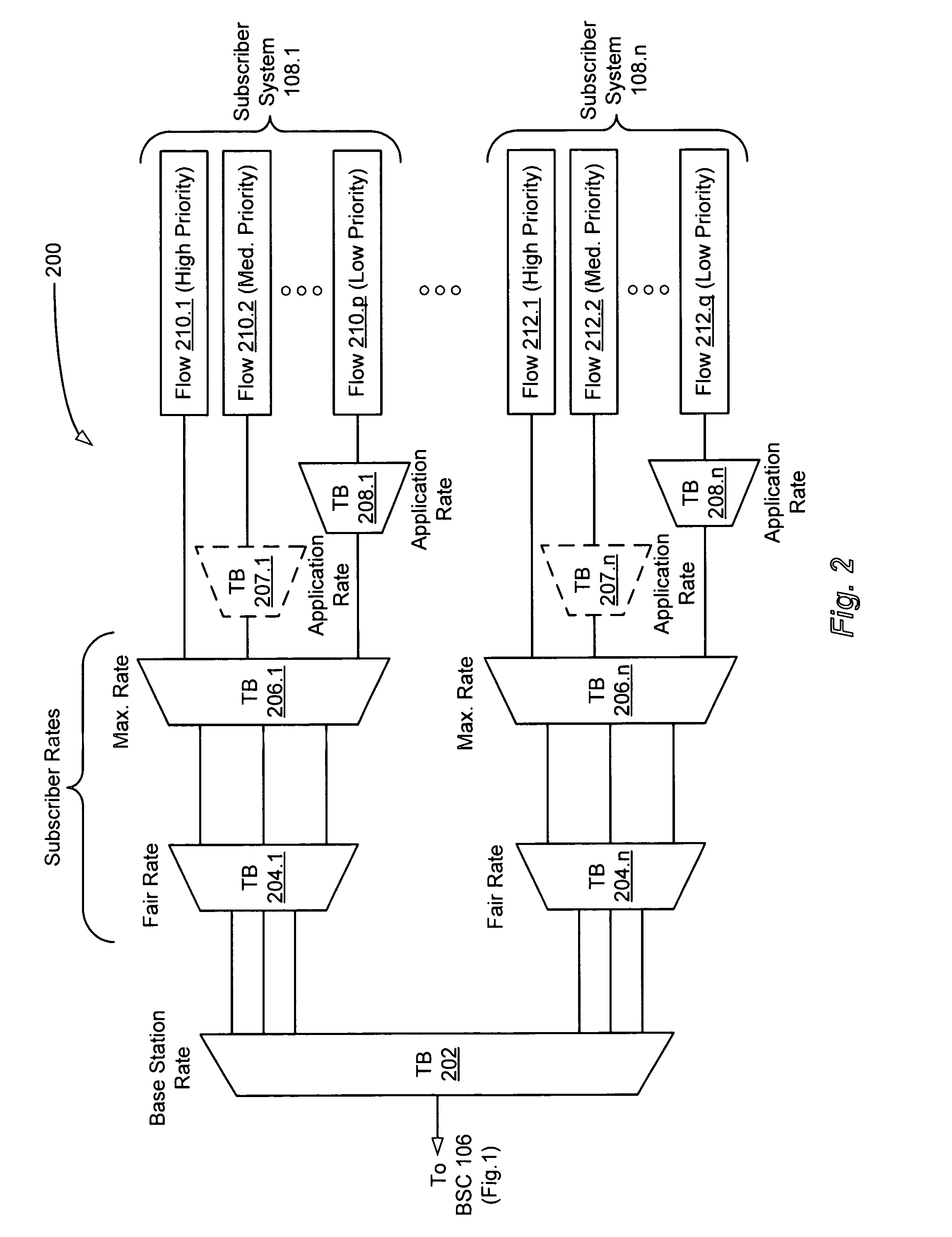

Hierarchical virtual queuing

InactiveUS7826358B2Unwanted latencyFair sharingError preventionTransmission systemsData streamPriority call

A system and method of providing high speed, prioritized delivery of data packets over broadband communications networks that avoids inducing unwanted latency in data packet transmission. The system employs a hierarchical, real-time, weighted token bucket prioritization scheme that provides for fair sharing of the available network bandwidth. At least one token bucket is employed at each level of the hierarchy to meter data flows providing service applications included in multiple subscribers' service plans. Each token bucket passes, discards, or marks as being eligible for subsequent discarding data packets contained in the data flows using an algorithm that takes into account the priority of the data packets, including strict high, strict medium, and strict low priorities corresponding to strict priority levels that cannot be overridden. The algorithm also takes into account weighted priorities of at least a subset of the low priority data packets. The priority levels of these low priority data packets are weighted to provide for fair sharing of the available network bandwidth among the low priority data flows, and to assure that none of the low priority data flows is starved of service.

Owner:ELLACOYA NETWORKS

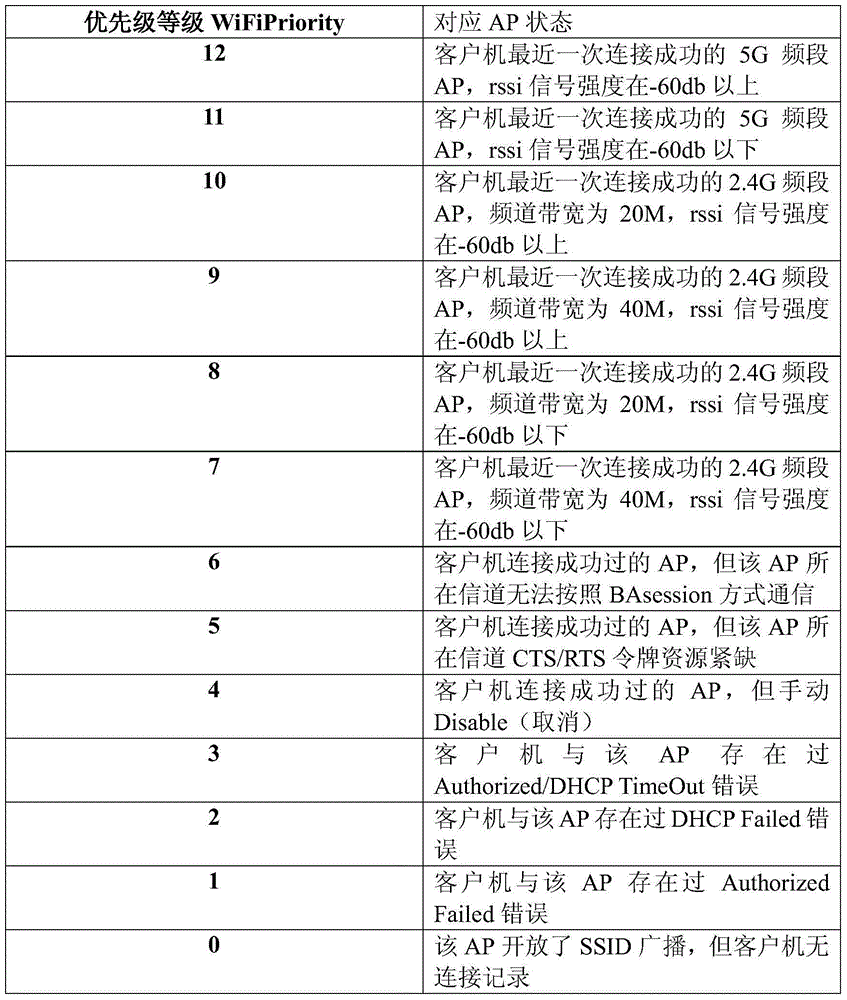

Method for controlling AP connection priority under WiFi environment

ActiveCN104796965AOptimize WiFi connection selectionReasonable WiFi connection selectionAssess restrictionNetwork topologiesCommunication qualityUser device

The invention relates to the field of wireless communication, and discloses a method for controlling AP connection priority under a WiFi environment. By means of the method, more optimized WiFi connection selected is provided for users. Twelve recommended priority levels are defined according to the severity degree of the interference problem in the WiFi practical environment, the recommended priority levels are used for guiding a current WiFi system to select appropriate AP trigger connection, APs of the twelfth priority level, the eleventh priority level, the tenth priority level, the ninth priority level, the eighth priority level and the seventh priority level can be used for normal connection communication, the specific priority levels are evaluated according to communication quality, the sixth priority level and the fifth priority level represents APs where normal connection can be conducted but communication quality problems happen, the specific priority levels are classified according to influences on the communication quality, the fourth priority level, the third priority level, the second priority level and the first priority level represent APs where connection processes are abnormal, and the specific priority levels are classified according to abnormity causes. The method is suitable for rapidly selecting optimal AP connection through user devices under the WiFi environment.

Owner:SICHUAN CHANGHONG ELECTRIC CO LTD

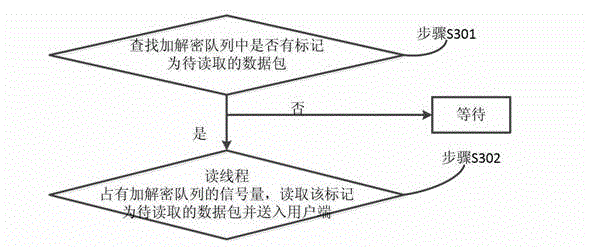

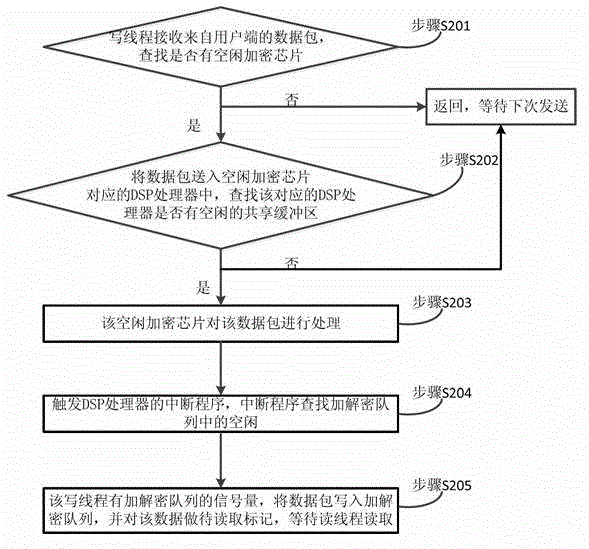

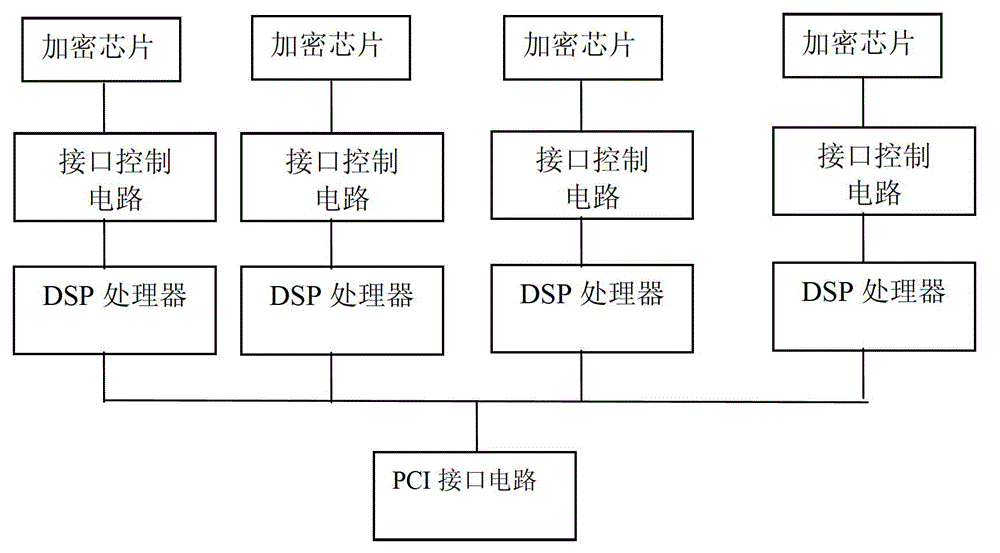

Encryption and decryption method for encrypt card

ActiveCN102724035AImprove efficiencyEffective use of encryption and decryption performanceEncryption apparatus with shift registers/memoriesCommunication interfacePacket loss

The invention provides an encryption and a decryption method for an encrypt card. The encrypt card comprises encryption chips, DSP (digital signal sensor) processors, interface control circuits and a PCI (programmable communication interface) circuit; the number of the DSP processors, the number of the interface control circuits and the number of the encryption chips are equal and are at least two, one DSP processor controls and is connected with one encryption chip by one corresponding interface control circuit; and at least two DSP processors are connected with the PCI circuit to achieve the data transmission of the encrypt card between computers. A non-preemption interruption mutual exclusion mechanism is adopted to avoid interruption emption based on interruption priority, reduce the phenomenon of packet loss and guarantee the correctness and order of the data packet processing procedure.

Owner:CHINA ELECTRIC POWER RES INST +3

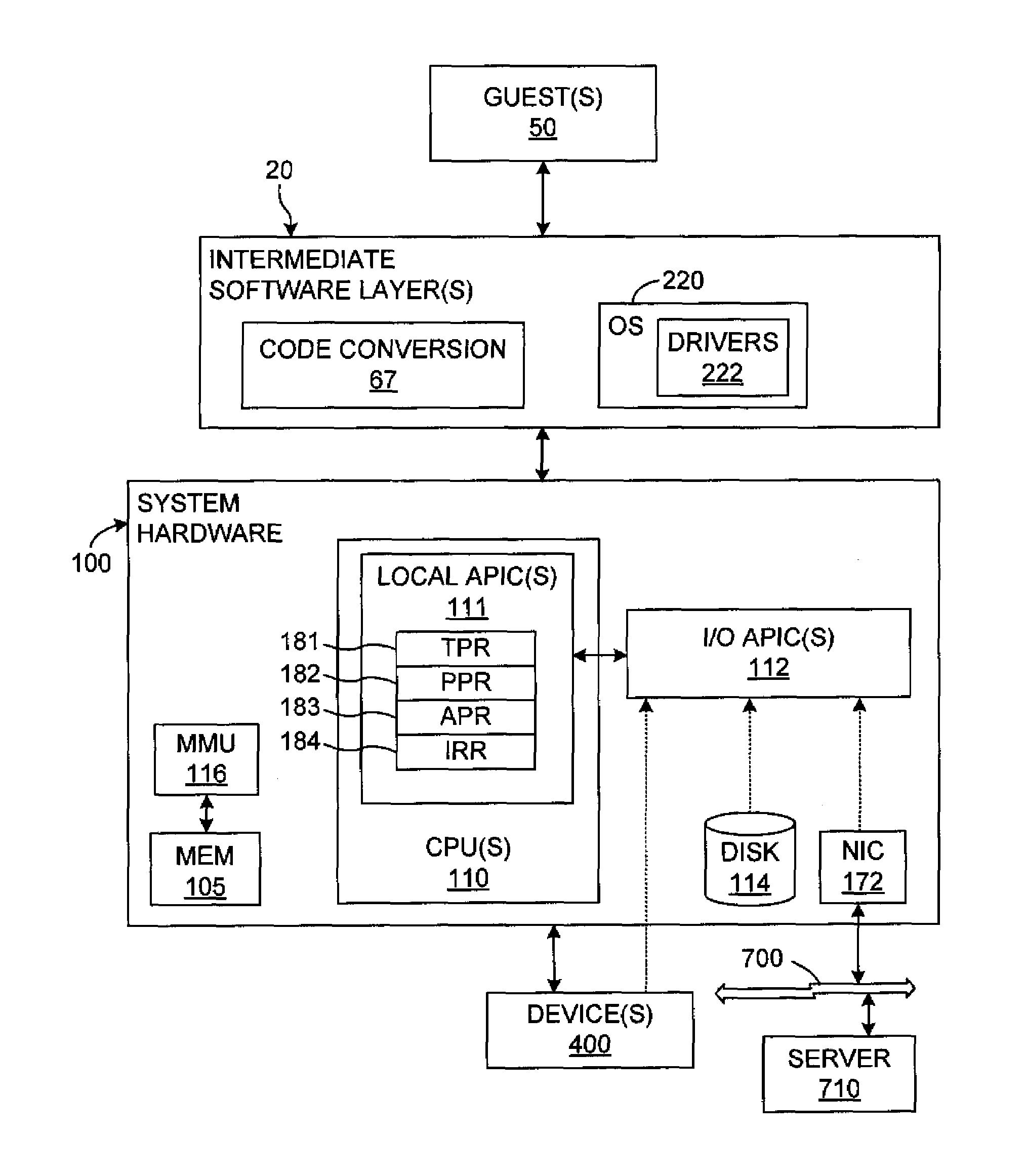

System and Method for Virtualizing Processor and Interrupt Priorities

ActiveUS20090300250A1Multiprogramming arrangementsSoftware simulation/interpretation/emulationVirtualizationProcessor scheduling

Dispatching of interrupts to a processor is conditionally suppressed, that is, only if an old priority value and a new priority value are either both less than or both greater than a maximum pending priority value. This conditional avoidance of dispatching is preferably implemented by a virtual priority module within a binary translator in a virtualized computer system and relates to interrupts directed to a virtualized processor by a virtualized local APIC.

Owner:VMWARE INC

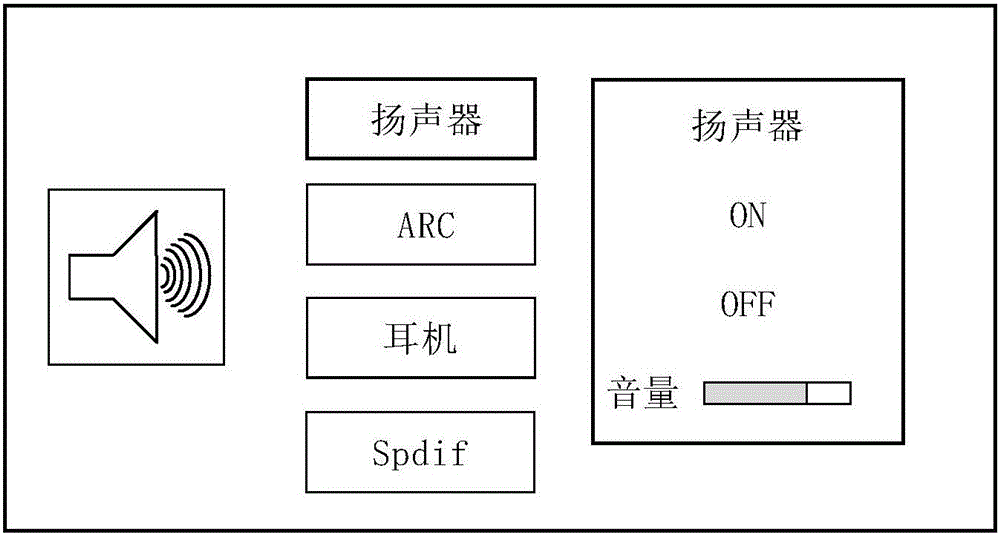

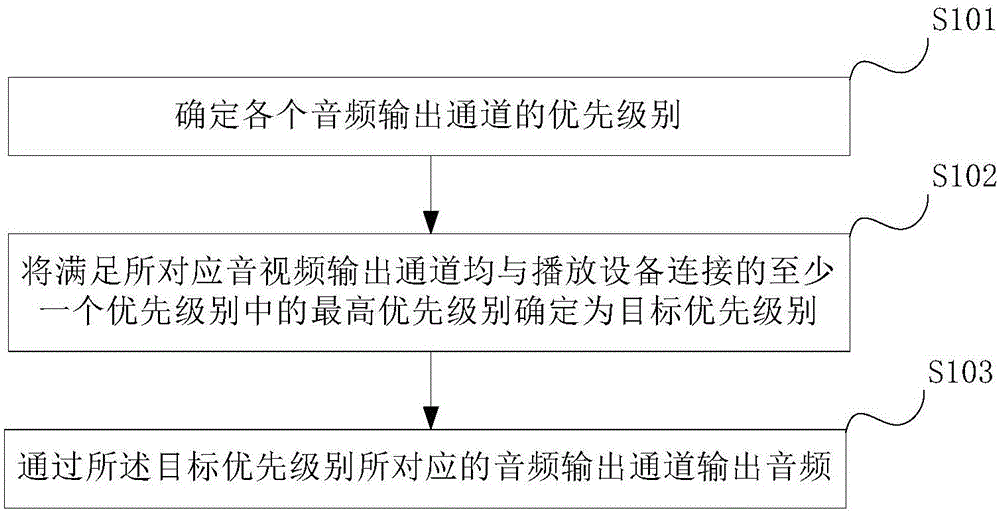

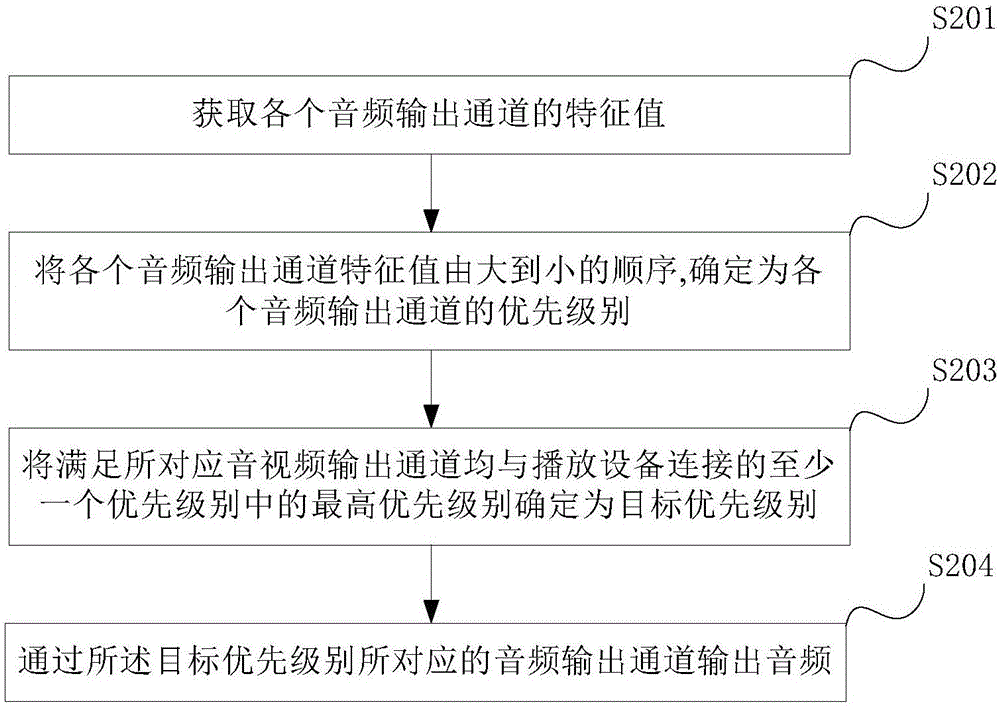

Method and device for selecting audio output channel and terminal equipment

InactiveCN106713978AImplement automatic selectionEasy to operateTelevision system detailsColor television detailsInteraction interfaceTerminal equipment

The invention provides a method and device for selecting an audio output channel and terminal equipment. According to the invention, by a set of algorithm, a target priority level is automatically determined, and by an audio output channel corresponding to the target priority level, an audio is output, so that automatic selection of a plurality of audio output channels is implemented. Various human-computer interaction interfaces and channel control algorithms do not need to be designed, and thus, a computation burden and operation time of a television terminal program can be reduced. Moreover, when a new audio output channel is added according to actual demands, only a priority level and a connection state of the newly added audio output channel need to be determined, thereby benefiting for improving flexibility in program design. According to the method, in a mode of setting various priority levels, various combination modes of the audio output channels can be provided; when the priority level and the connection state of each audio output channel are changed, the target priority level can be changed accordingly. According to the method for dynamically selecting the audio output channel, operability and flexibility of selecting the audio output channels can be improved.

Owner:HISENSE VISUAL TECH CO LTD

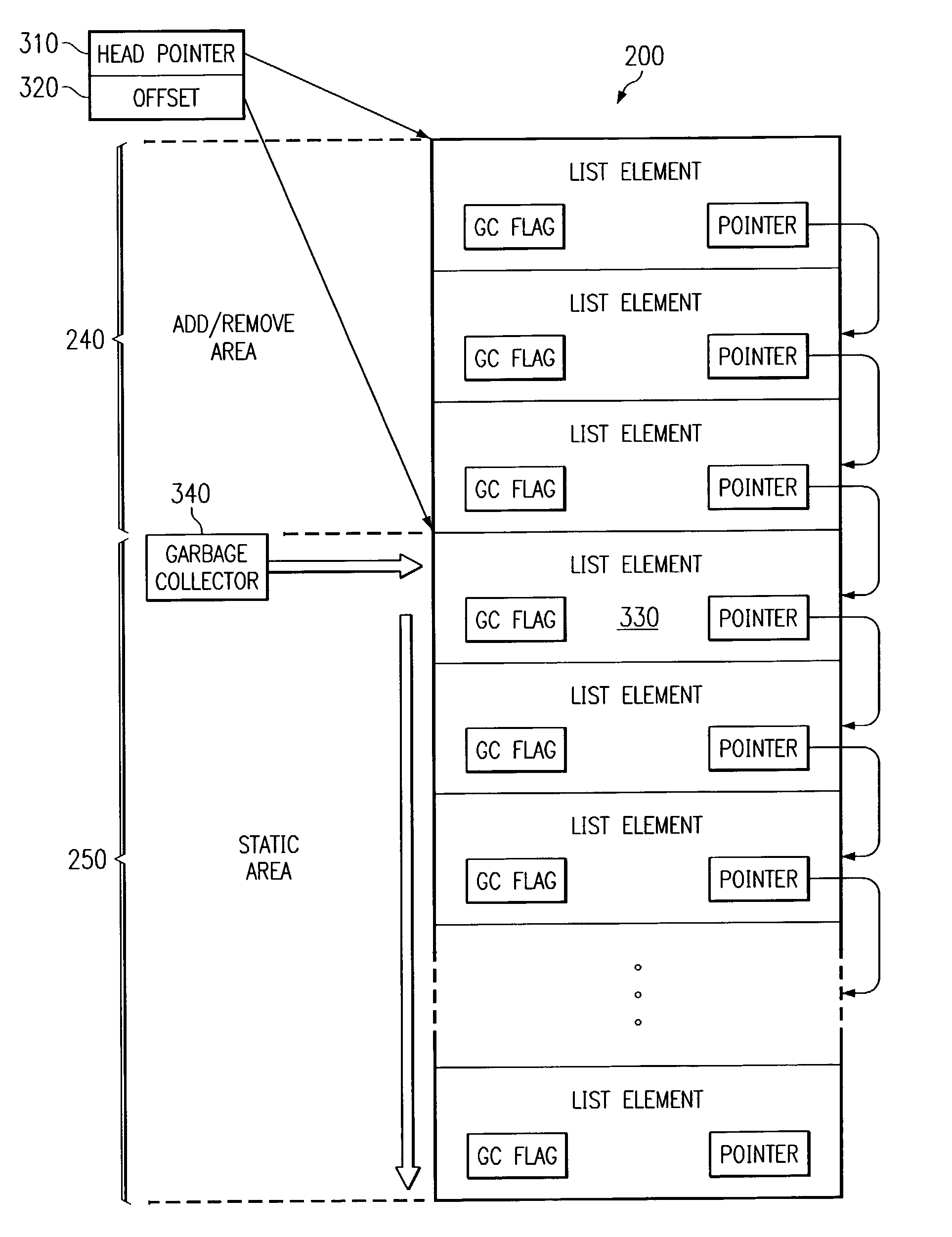

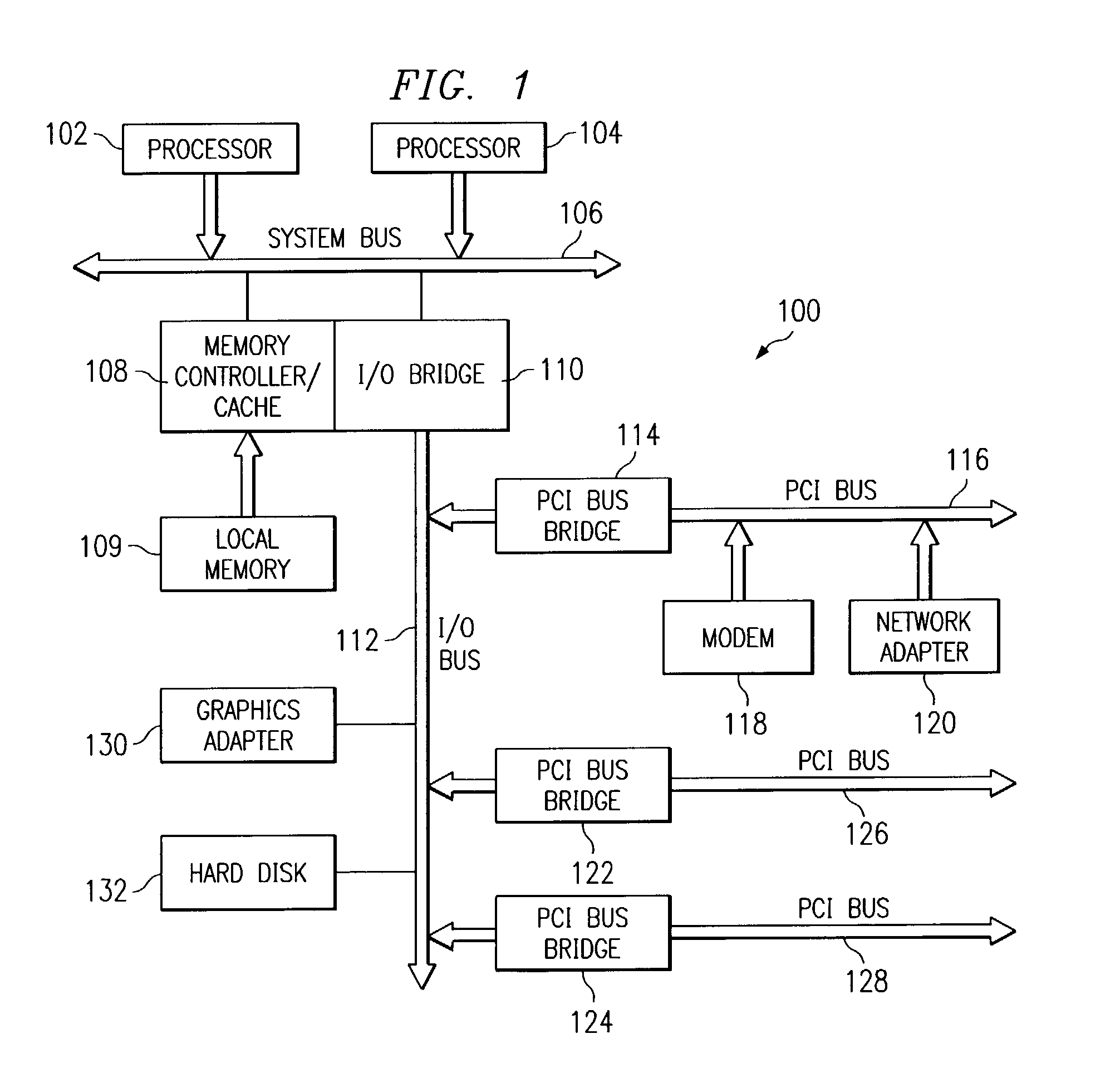

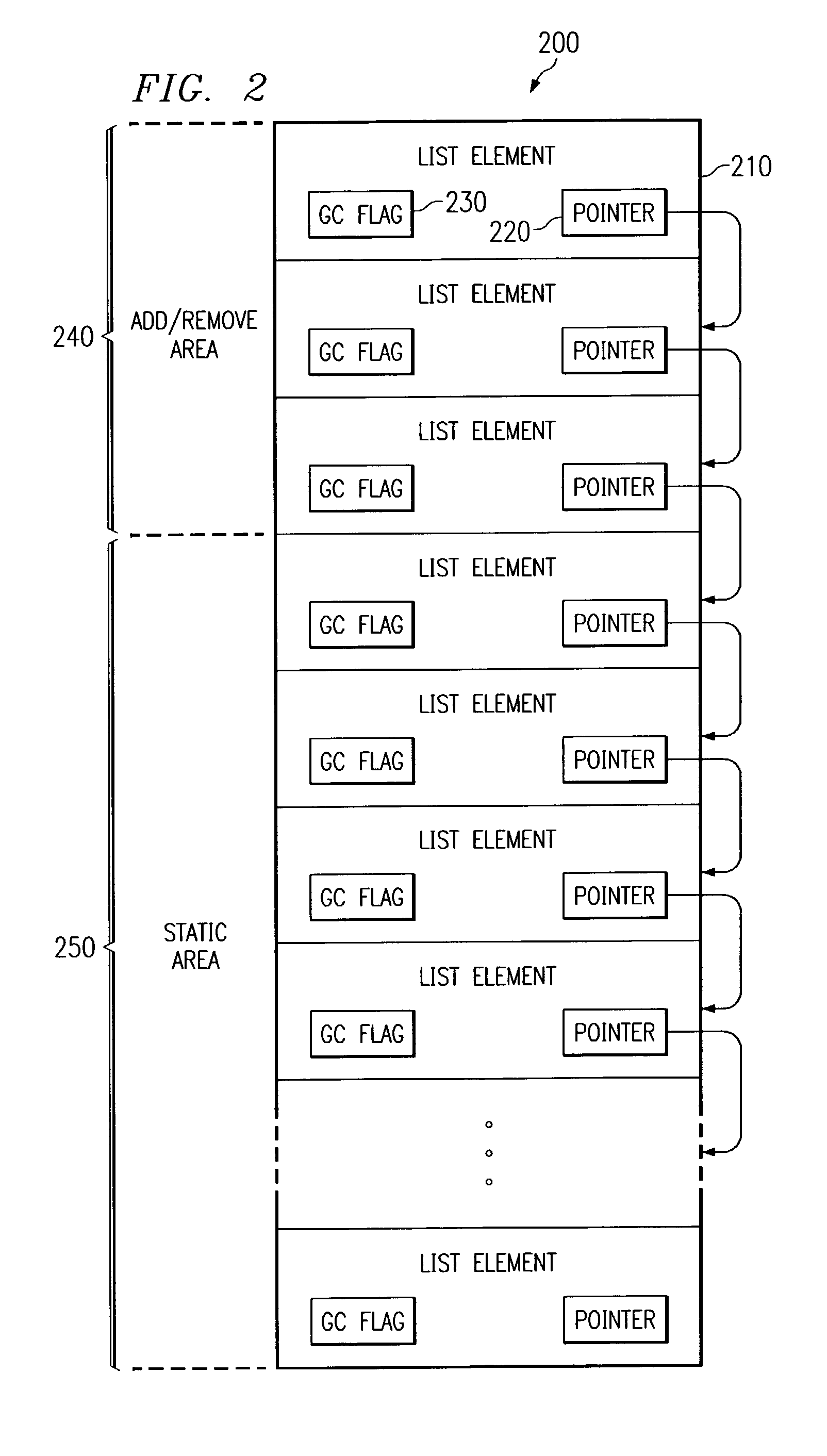

Apparatus and method for removing elements from a linked list

InactiveUS7249352B2Digital data processing detailsMemory adressing/allocation/relocationMulti processorWaste collection

Methods, apparatus and computer program products for removal of elements from a linked list while other elements of the linked list are allowed to be accessed during the removal operation. In one embodiment, the method, apparatus and computer program product include identifying an add / remove area of a linked list and a static area of the linked list. Elements may only be added or removed from the linked list in the add / remove area or by a garbage collector that performs garbage collection only on elements in the static area of the linked list. The garbage collector identifies an element after the last element in the add / remove area and performs garbage collection beginning with that element and moving through the static area. In an alternative embodiment, a “next element” pointer in a previous list element is set to point to the element being deleted's “next element” pointer. Any global references to the element being deleted must be modified. A message may then be issued to the processors of a multiprocessor system at a same interrupt priority as a reading process priority. Once the processors respond to the message, garbage collection may be performed on the element to be deleted.

Owner:IBM CORP

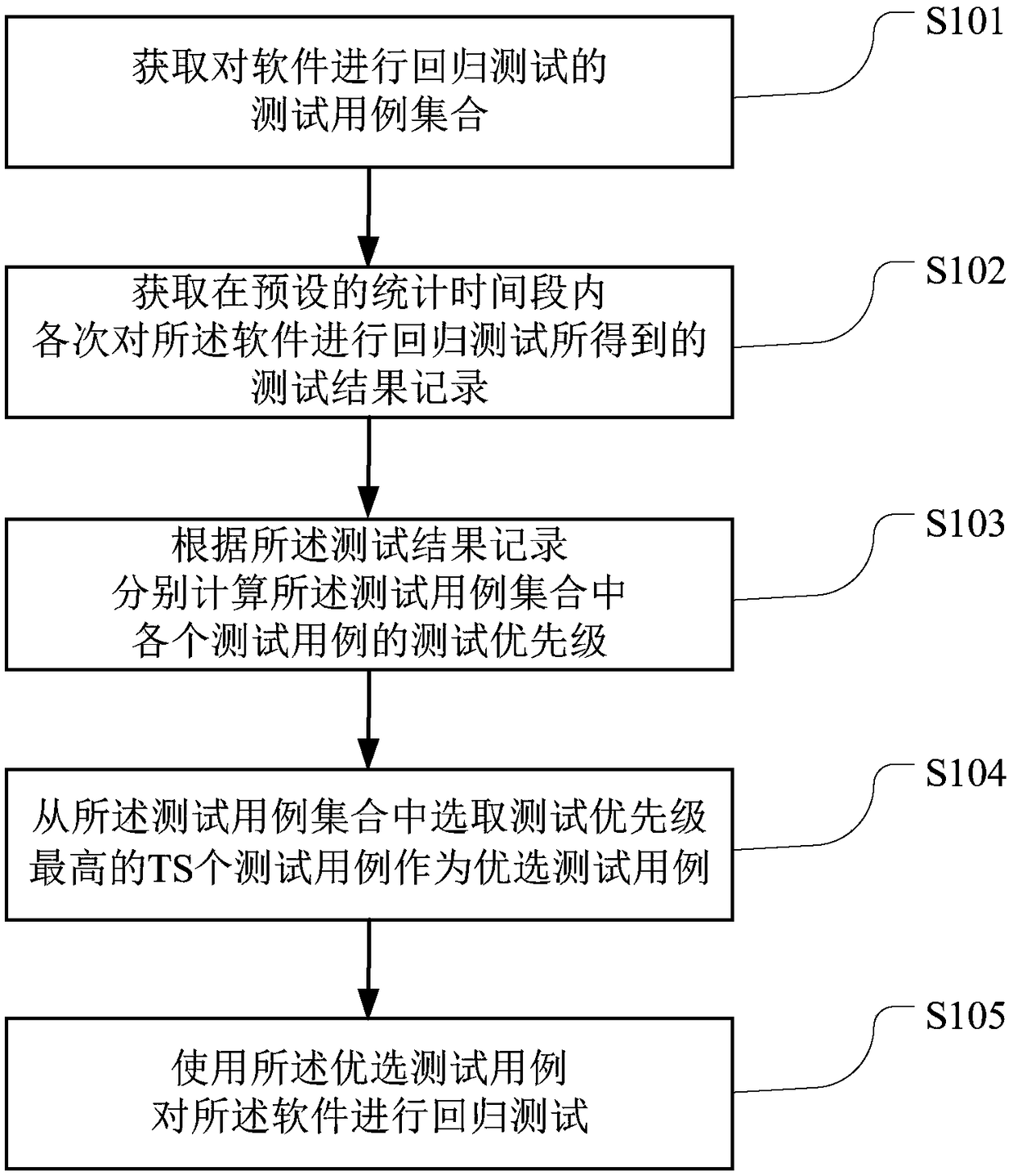

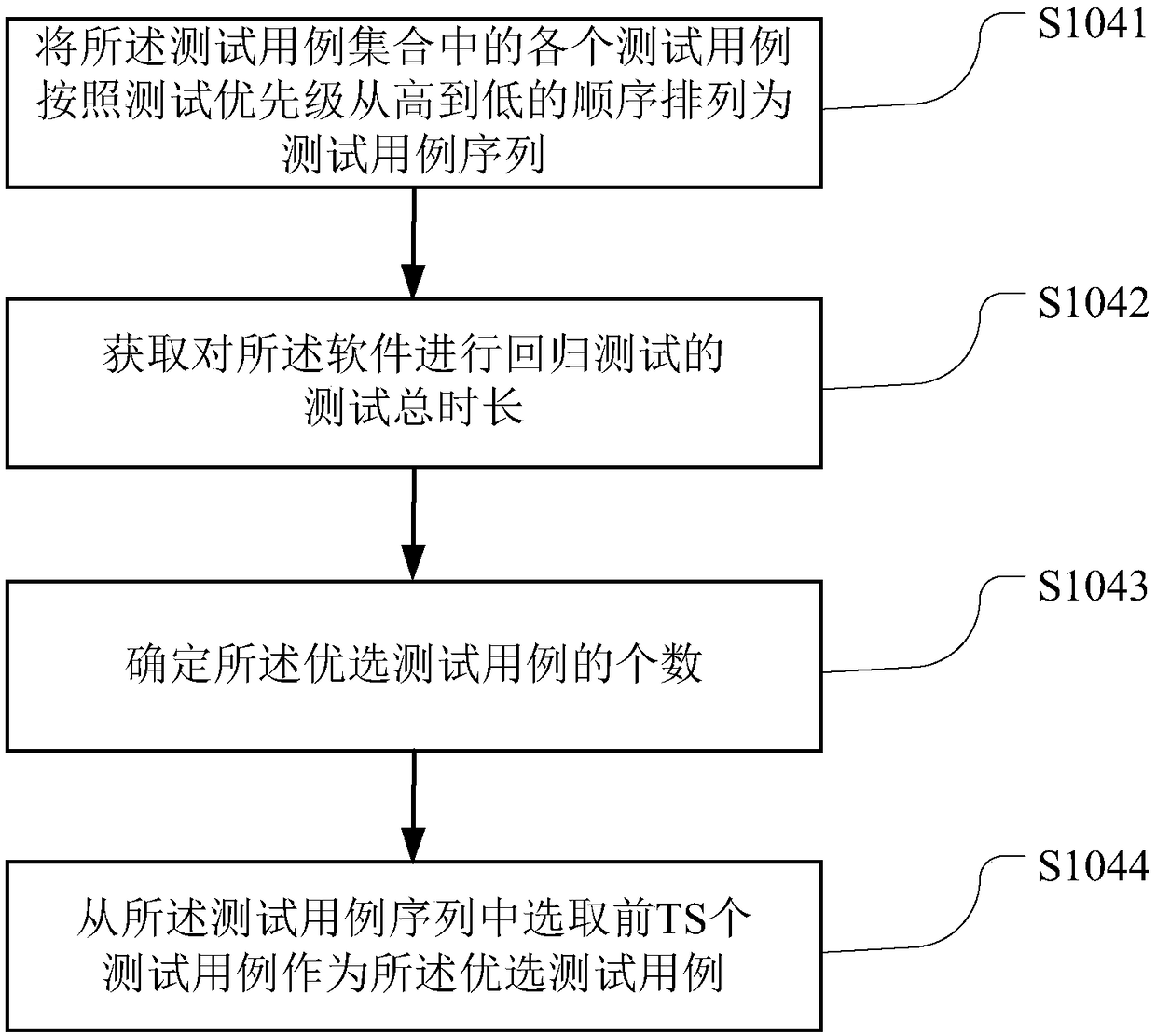

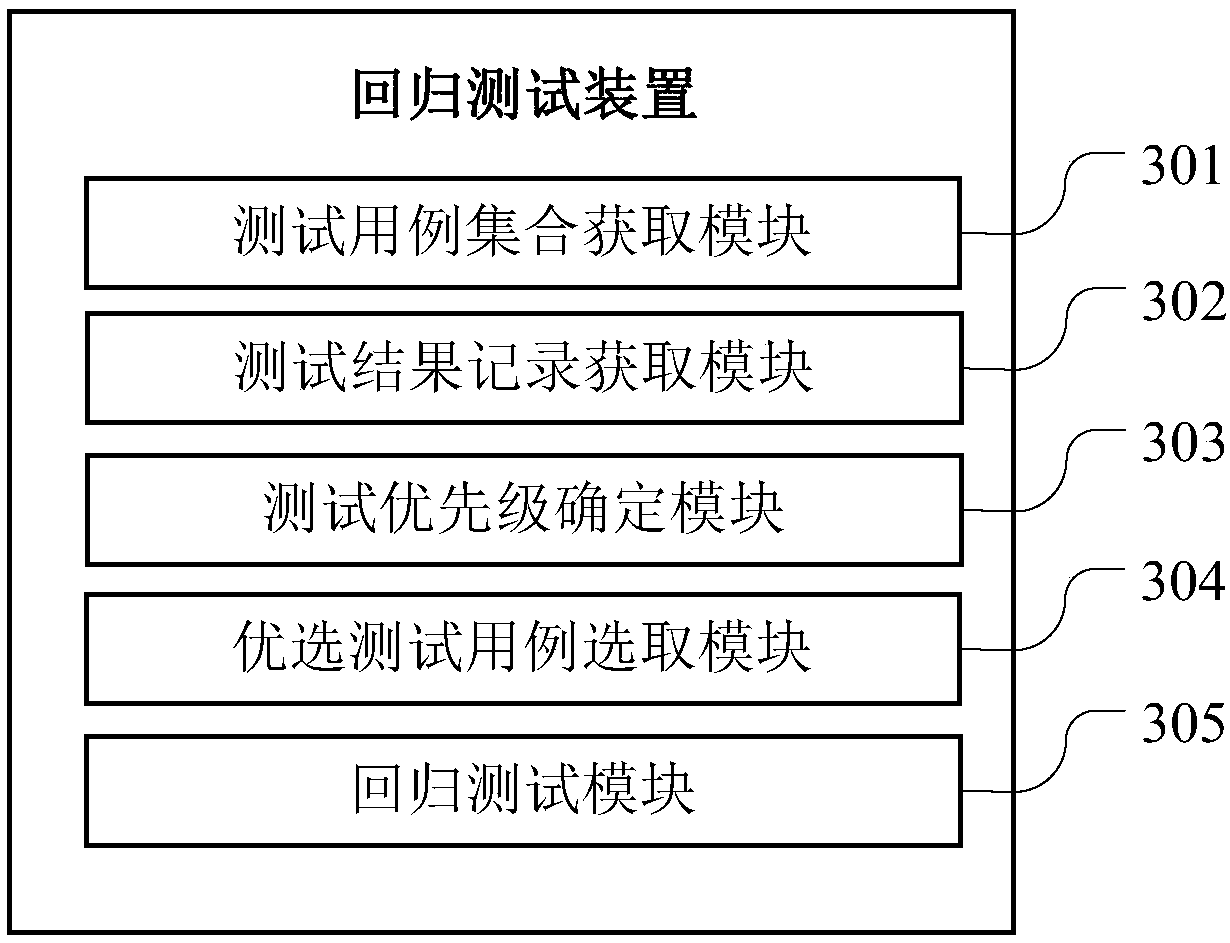

Regression testing method, computer readable storage medium and terminal equipment

ActiveCN108694123AEnsure defectsSoftware testing/debuggingEnergy efficient computingRegression testingTested time

The invention belongs to the technical field of a computer, and particularly relates to a regression testing method, a computer readable storage medium and terminal equipment. The method comprises thefollowing steps of obtaining a test case set used for performing regression testing on software; obtaining test result records obtained by performing regression testing on the software in each time in the preset statistics time period; respectively determining the test priority level of each test case in the test case set according to the test result records; selecting TS test cases with the highest test priority levels from the test case set to be used as the optimized test cases; and using the optimum test cases to perform regression testing on the software. The test priority level is introduced for evaluating the importance of each test case; under the condition that the regression test time is limited, only partial test cases with the highest test priority levels are selected to be used for performing regression testing on the software; and the discovery of possibly more software defects in the limited time is ensured.

Owner:CHINA PING AN LIFE INSURANCE CO LTD

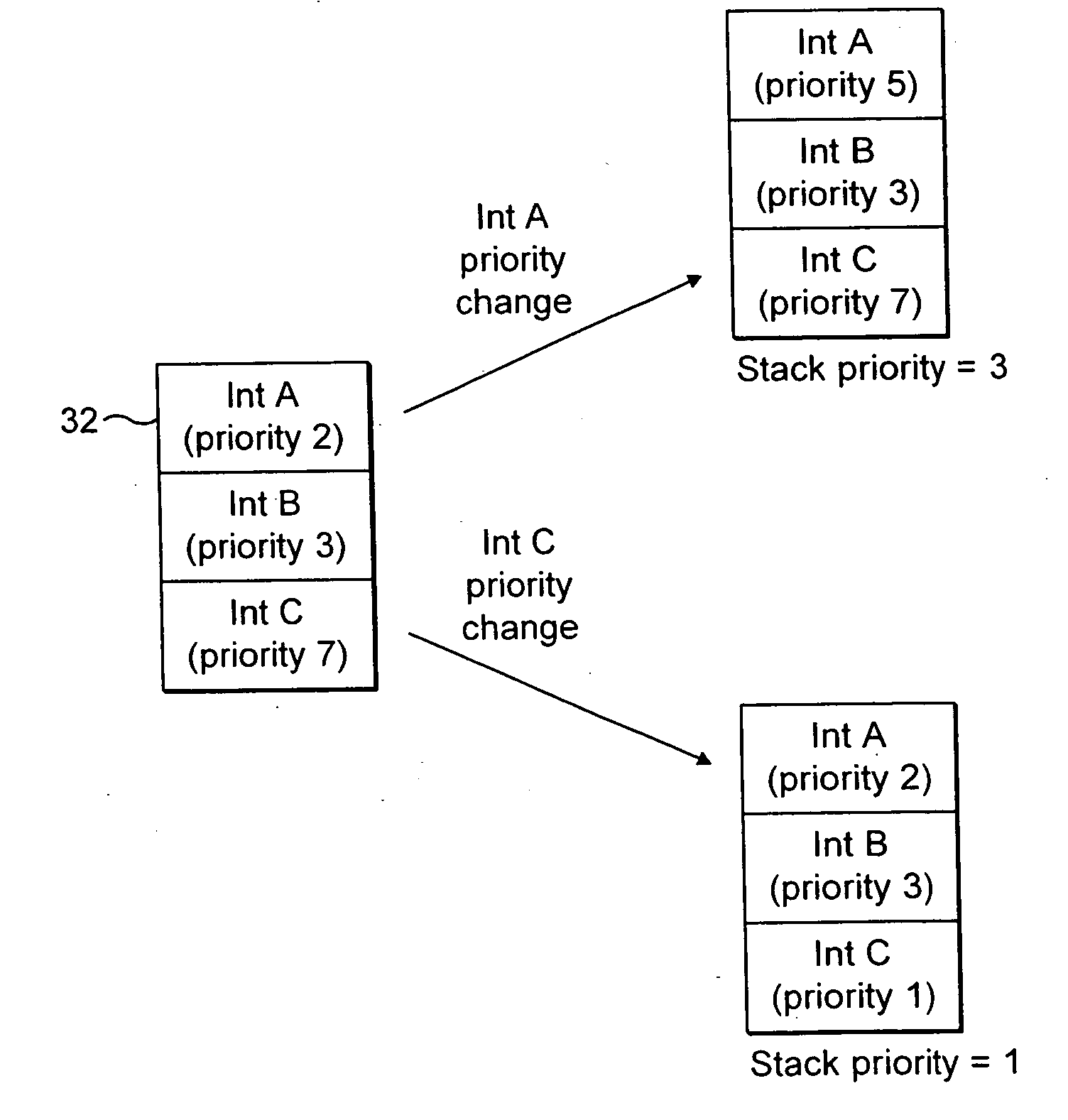

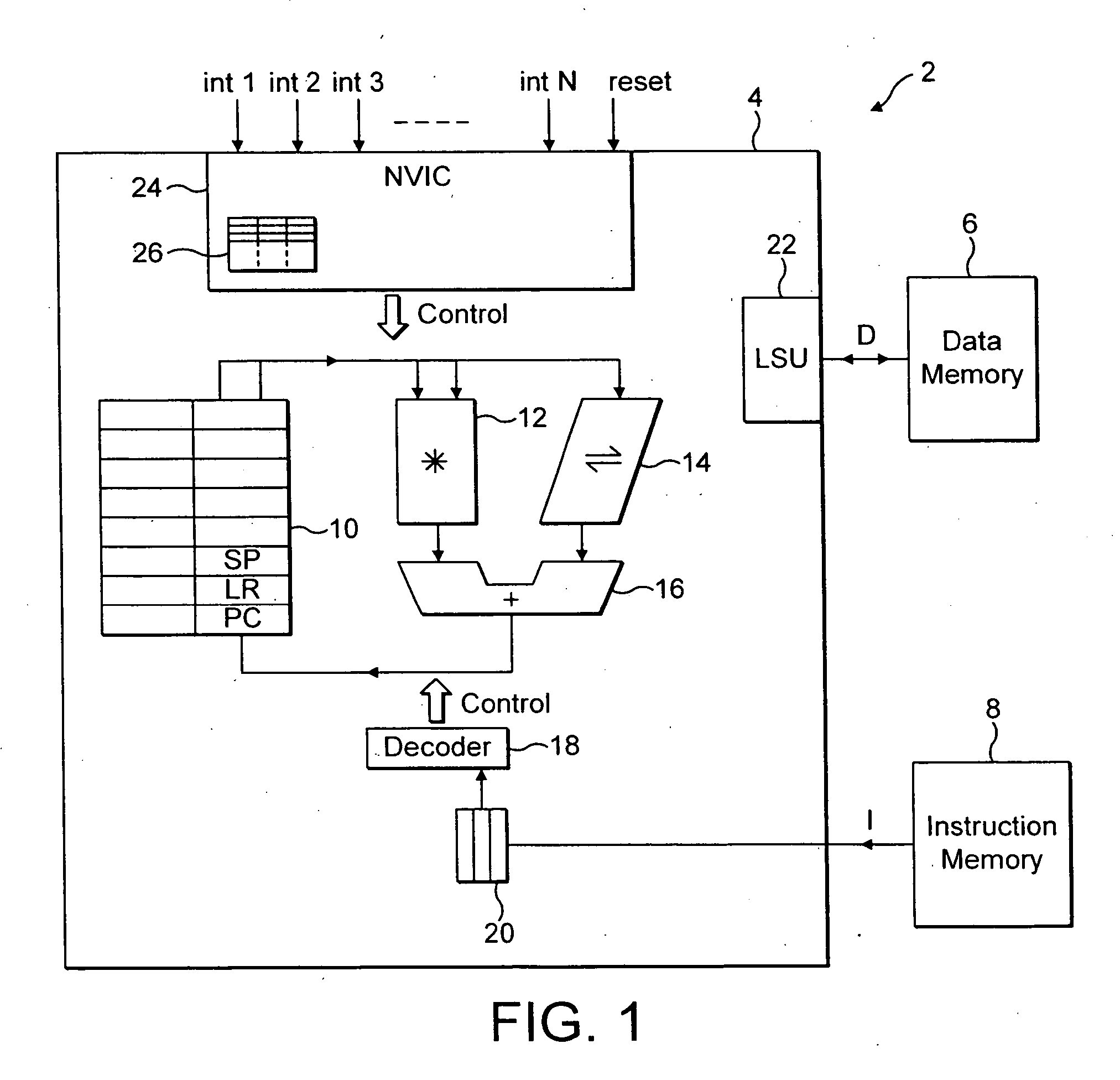

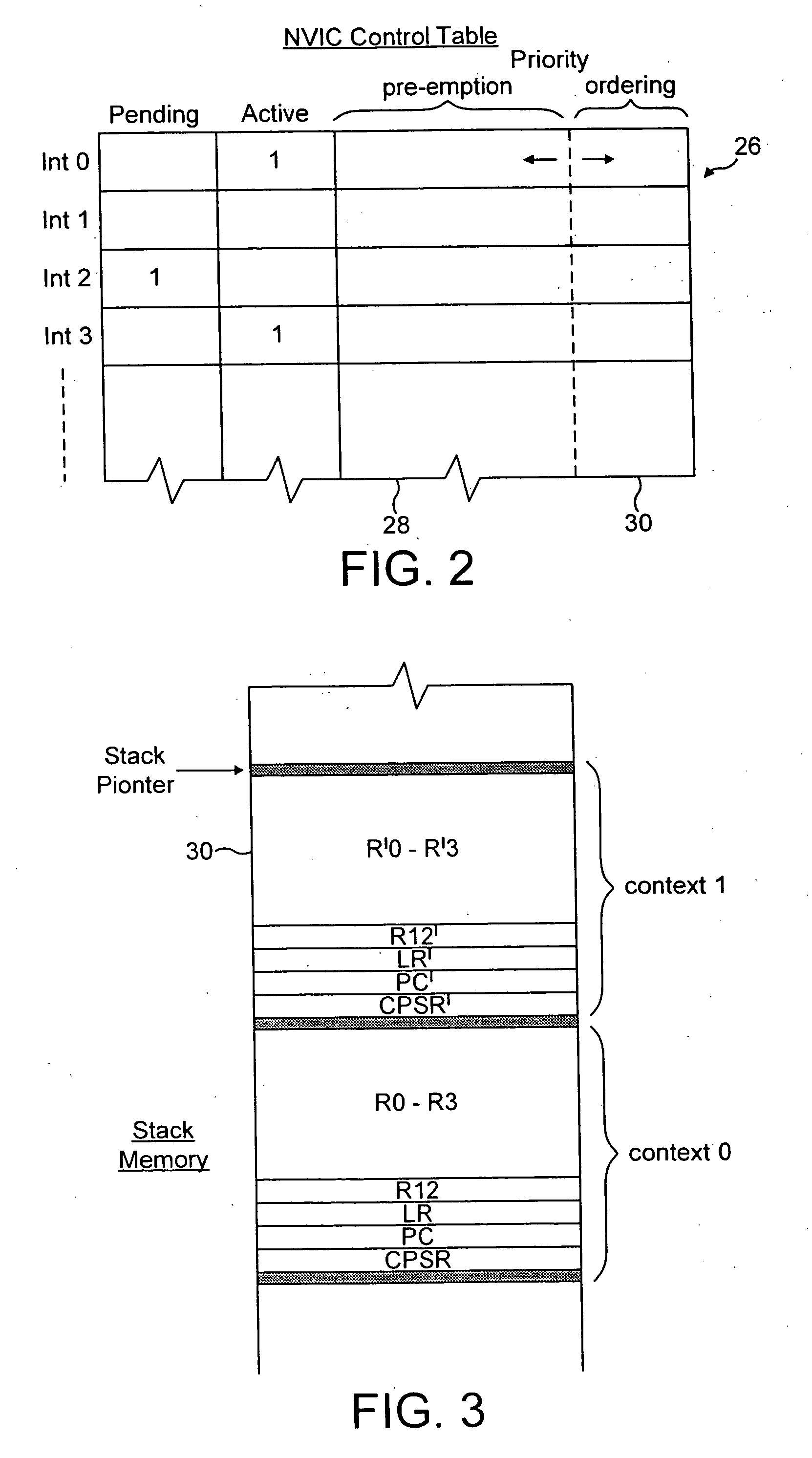

Interrupt priority control within a nested interrupt system

ActiveUS20050177667A1Data storage capacity is not exceededRaise priorityProgram initiation/switchingDigital computer detailsData processing systemPriority inversion

A data processing system 2 having a nested interrupt controller 24 supports nested active interrupts. The priority levels associated with different interrupts are alterable (possibly programmable) whilst the system is running. In order to prevent problems associated with priority inversions within nested interrupts, the nested interrupt controller when considering whether a pending interrupt should pre-empt existing active interrupts, compares the priority of the pending interrupt with the highest priority of any of the currently active interrupts that are nested together.

Owner:ARM LTD

Relay selecting method based on interrupt priority for unisource multi-relay cooperative communication system

InactiveCN103402237AEnsure fairnessImprove throughputHigh level techniquesWireless communicationCommunications systemChannel capacity

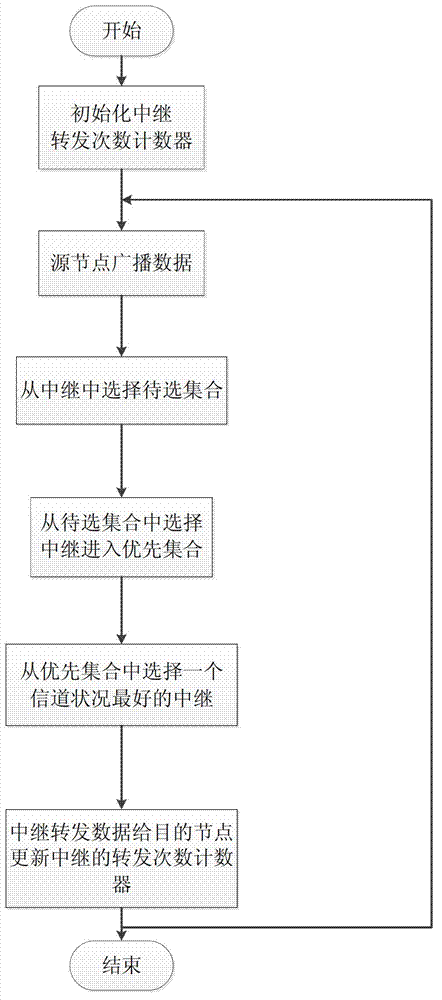

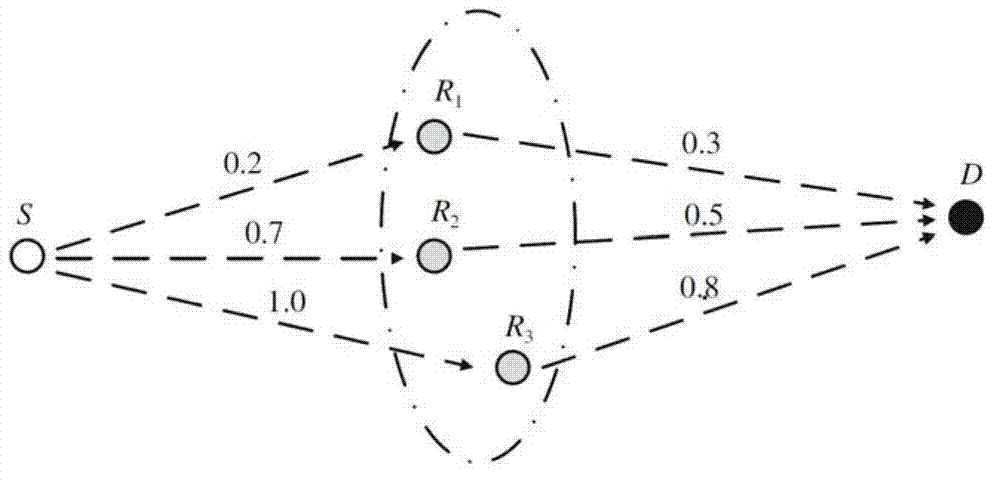

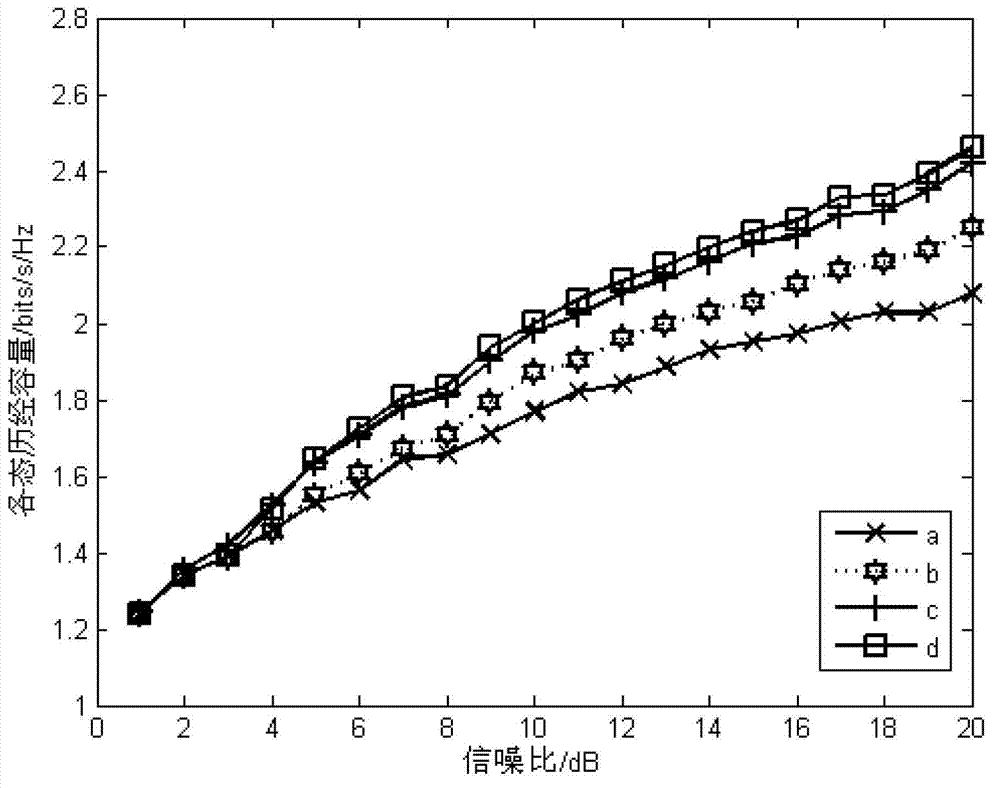

The invention discloses a relay selecting method based on interrupt priority for a unisource multi-relay cooperative communication system, which aims at overcoming a defect that an 'optimum interrupt' optimal fair selection strategy cannot ensure a larger system throughput. The method comprises steps of firstly, arranging an independent transmission times counter for each relay on a target node; then selecting a relay with the channel capacity being more than the interrupt capacity and adding the relay into a candidate set; selecting a relay with less transmission times from the candidate set and adding the relay into an optimal set, and then selecting a relay with the optimal channel quality from the optimal set to transmit; increasing the count of the corresponding transmission times counter after each transmission of each relay; repeating the steps in each cooperation period until the cooperation period ends. According to the method, the channel quality and fairness are comprehensively taken into consideration when the relays are selected, the system throughput is improved on the basis of ensuring high fairness, and the method has a good effect.

Owner:XI AN JIAOTONG UNIV