Multicore processor, and system and method for debugging multicore processor

A technology of multi-core processors and processor cores, applied in the field of multi-core processors, can solve problems such as unfavorable multi-core processors and compatibility with debugging systems

- Summary

- Abstract

- Description

- Claims

- Application Information

AI Technical Summary

Problems solved by technology

Method used

Image

Examples

Embodiment 1

[0038] The purpose of this embodiment is to provide a multi-core processor, the test access port TAP of each processor core is a standard form, and the port of the JTAG emulator for debugging is a standard JTAG port.

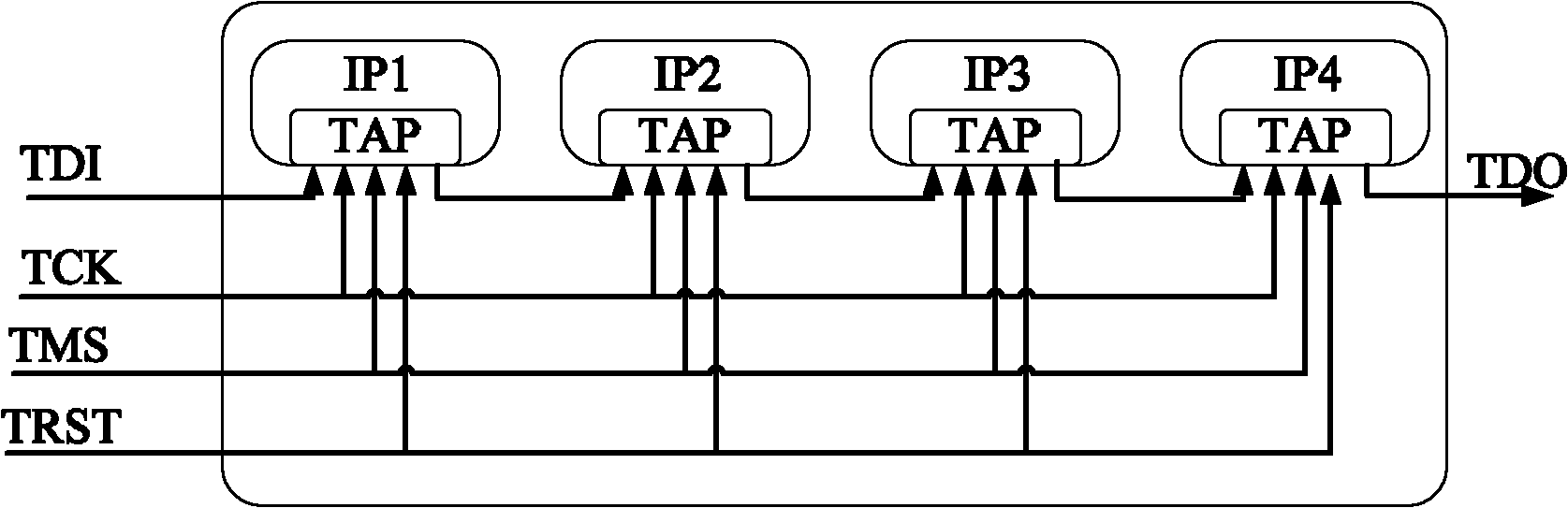

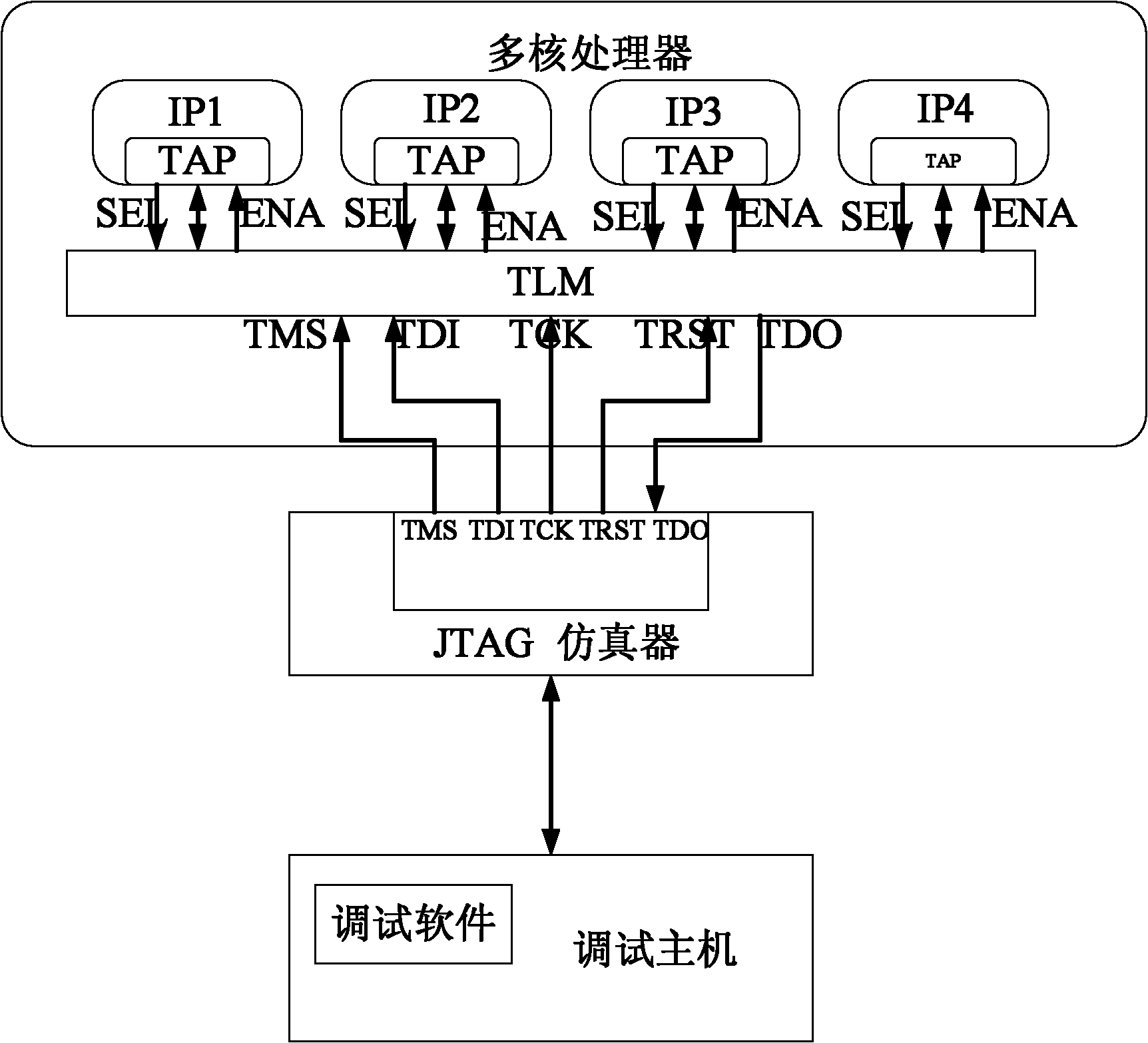

[0039] refer to Figure 4 , a multi-core processor, the communication between the test access port TAP of each processor core and the JTAG emulator is realized by a chip-level TAP support module. The chip-level TAP support module is located inside the chip, and is connected to the test access port TAP of each processor core, and the test access port TAP of each processor core is connected to the chip-level TAP support module in parallel. The chip-level TAP support module is provided with an external interface, and the external interface includes a TDI interface for receiving test data, a TDO interface for feeding back test data output to the emulator, a TCK interface for receiving a test clock signal, and a TCK interface for receiving test data. TMS interface f...

Embodiment 2

[0048] The multi-core processor in Embodiment 1 may have the following problems when debugging: if the processor core to be tested enters the debugging state, and other processor cores do not enter the debugging state, it is possible to make the debugging result reduced reliability. Because, when debugging a certain processor core, operations such as I / O (input and output), reading and writing memory of other processor cores may cause the variable value of the processor core in the debugging state to change, so that The reliability of the commissioning results has been questioned. At the same time, there is another situation, that is, when the system clock supply of a certain processor core is insufficient or the system power supply is insufficient, if it is forced to debug, the reliability of the debugging results will be questioned because of the above-mentioned situation , the processor core cannot be debugged in real time.

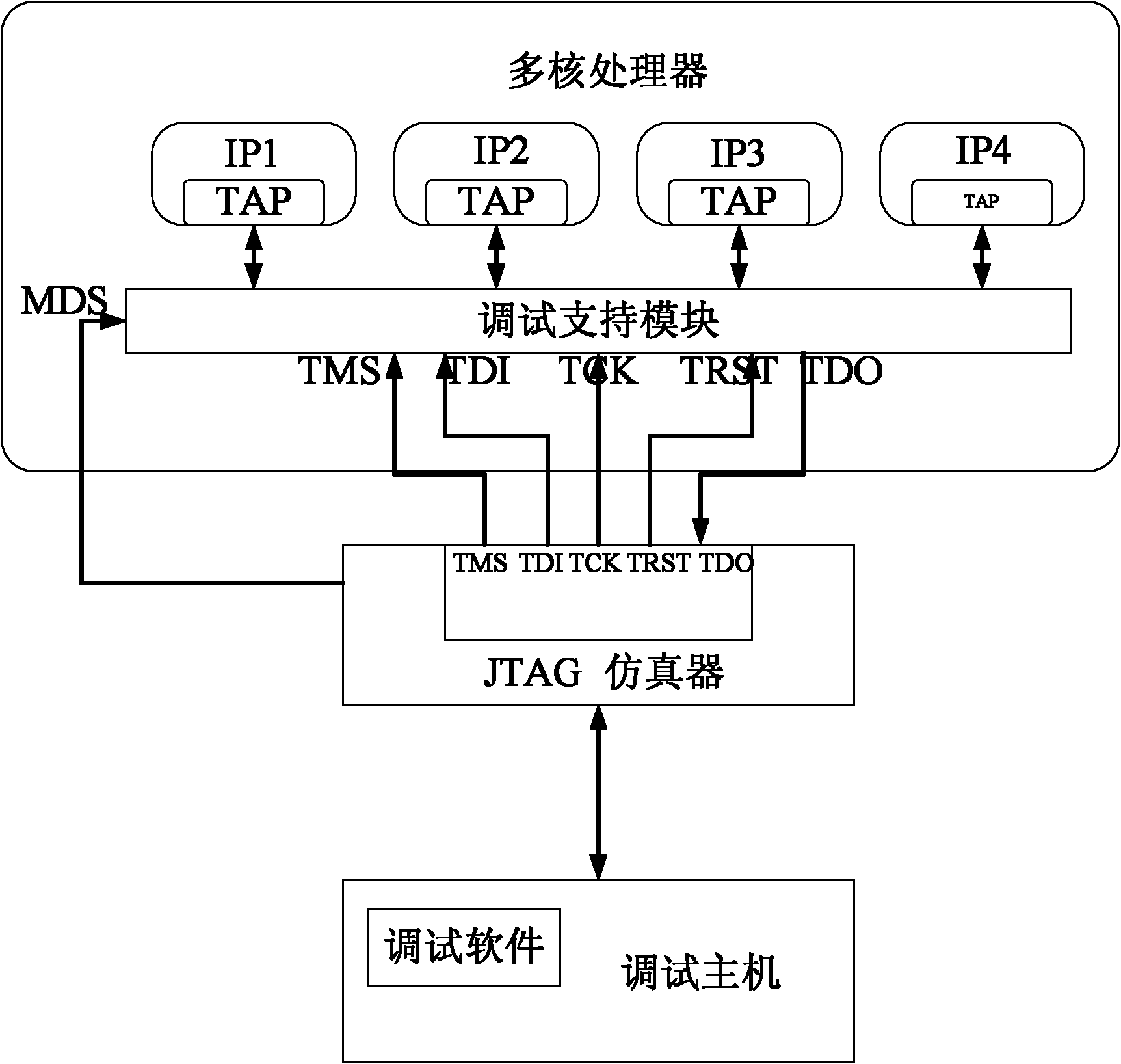

[0049]Therefore, on the basis of Embodiment 1,...

Embodiment 3

[0057] Please refer to Figure 4 A debugging system for a multi-core processor includes a debugging host, an emulator and a multi-core processor. The debugging host is connected with the emulator, and is used to transmit information such as debugging data and debugging instructions to the multi-core processor through the emulator, and then debug the multi-core processor. The emulator is a standard JTAG emulator, which is connected with the multi-core processor by a standard TDI, TDO, TMS, TCK and / or TRST interface, and the multi-core processor has the method described in embodiment 1 and / or embodiment 2. structure and function.

[0058] Please refer to Figure 9 , a debugging method for a multi-core processor, comprising steps:

[0059] Step A, the debugging host cyclically visits the test access port controller until the debug response signal sent by the test access port controller is obtained;

[0060] Step B, the debugging host configures the test access terminal contro...

PUM

Login to View More

Login to View More Abstract

Description

Claims

Application Information

Login to View More

Login to View More