Chip picking and position aligning confirmation method for ink dot-free test

An ink dot and testing machine technology, which is applied in the field of non-ink dot test pick sheet alignment confirmation, can solve the problems of error-prone, multi-sized chips, and difficulty in the latter, so as to reduce the difficulty of confirmation, prevent drift, and simplify the process flow. Effect

- Summary

- Abstract

- Description

- Claims

- Application Information

AI Technical Summary

Problems solved by technology

Method used

Image

Examples

Embodiment Construction

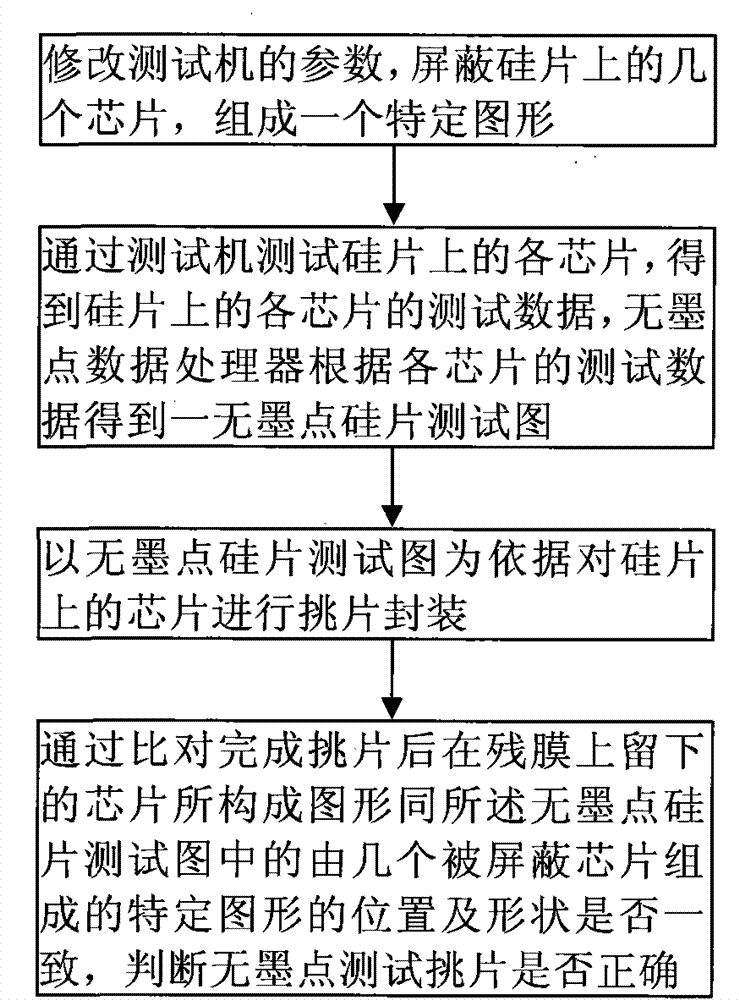

[0017] An embodiment of the alignment confirmation method of the ink-free dot test picking piece of the present invention is as follows: figure 1 shown, including the following steps:

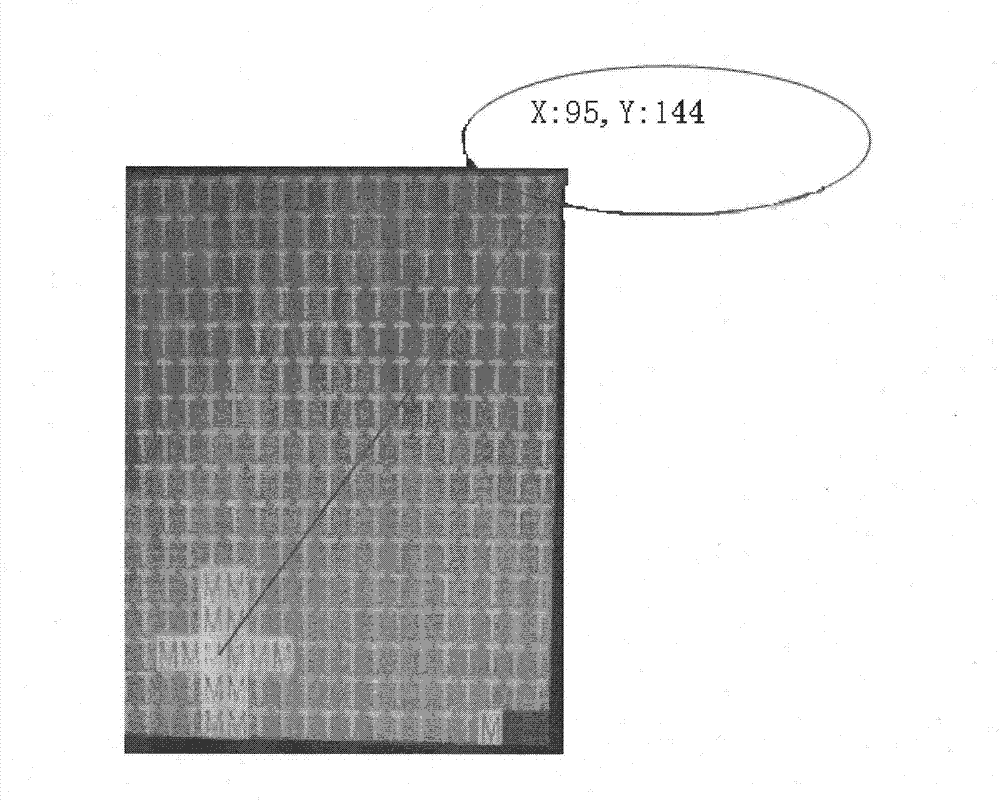

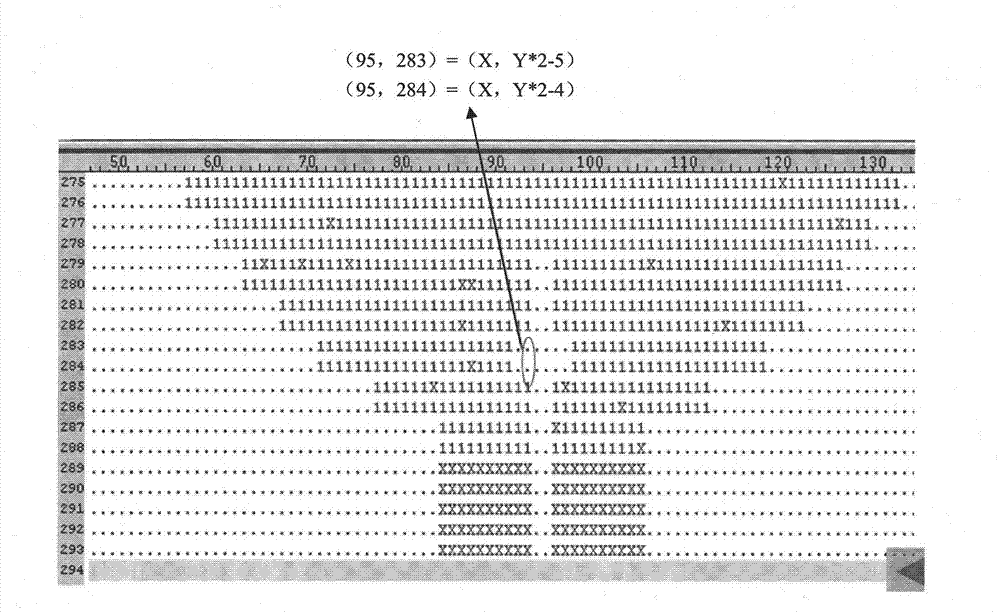

[0018] 1. Modify the parameters of the testing machine to mask several chips on the silicon wafer above the NOTCH (notch) of the silicon wafer to form a specific figure: a cross, such as figure 2 As shown, the coordinates of the two chips at the center of the cross are: X=95, Y=144. This specific graphic can be a cross, a rhombus, a triangle, an F, and the like.

[0019] Two. test each chip on the silicon wafer by a testing machine, obtain the test data of each chip on the silicon wafer, output to the data processor without ink dots, and the data processor without ink dots obtains a no ink dot data processor according to the test data of each chip Ink-dot silicon wafer test chart, the obtained no-ink-dot silicon wafer test chart will have the specific pattern composed of several shielded chi...

PUM

Login to View More

Login to View More Abstract

Description

Claims

Application Information

Login to View More

Login to View More