Multi-channel direct memory access (DMA) controller with arbitrator

A technology of DMA controller and arbiter, applied in instruments, electrical digital data processing, etc., can solve the problems of slow transmission speed, no arbitration strategy, unable to cope with the simultaneous initiation of DMA transmission by multiple channels, etc., to improve the speed and expand the application. range effect

- Summary

- Abstract

- Description

- Claims

- Application Information

AI Technical Summary

Problems solved by technology

Method used

Image

Examples

Embodiment Construction

[0043] The present invention will be further described in detail below in conjunction with the accompanying drawings and specific embodiments.

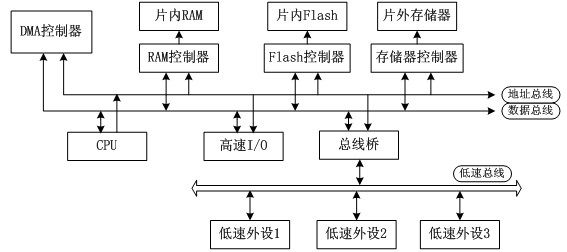

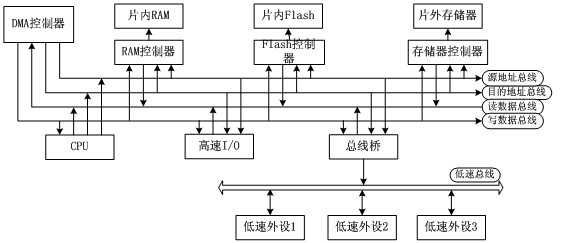

[0044] figure 2It is the overall block diagram of the improved DMA system of the present invention. As shown in the figure, there are two sets of buses in the system, the data lines of the two sets of buses are respectively used as the read data bus and the write data bus, and the address lines of the two sets of buses are respectively used as the source address bus and the destination address bus.

[0045] figure 2 It also shows the structure of the whole system, including CPU, DMA controller, on-chip and off-chip memory, high-speed I / O, bus bridge and low-speed peripherals, among which:

[0046] The CPU is connected to the high-speed bus, processes the DMA transfer request sent by the DMA controller, and grants the DMA controller the right to use the bus.

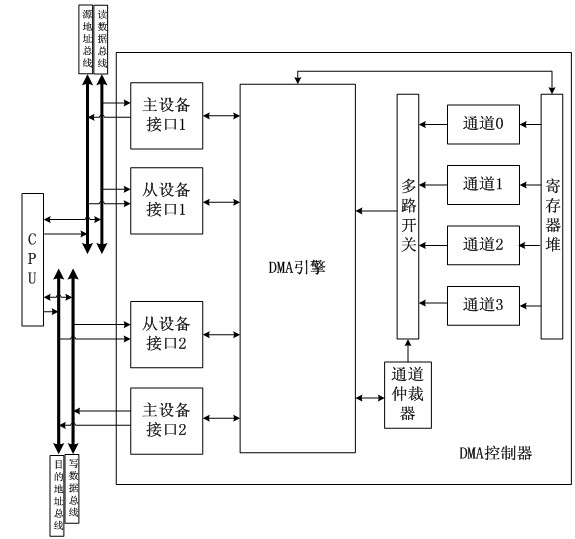

[0047] The DMA controller is connected to the high-speed bus, processes...

PUM

Login to View More

Login to View More Abstract

Description

Claims

Application Information

Login to View More

Login to View More