Dynamic memory controller and method for increasing bandwidth utilization rate of dynamic memory

A technology of dynamic memory and controller, which is applied in the direction of instrumentation, electrical digital data processing, etc., can solve the problem of low bandwidth utilization of dynamic memory, and achieve the goal of improving bandwidth utilization, reducing delay, and reducing writing or reading delay Effect

- Summary

- Abstract

- Description

- Claims

- Application Information

AI Technical Summary

Problems solved by technology

Method used

Image

Examples

Embodiment Construction

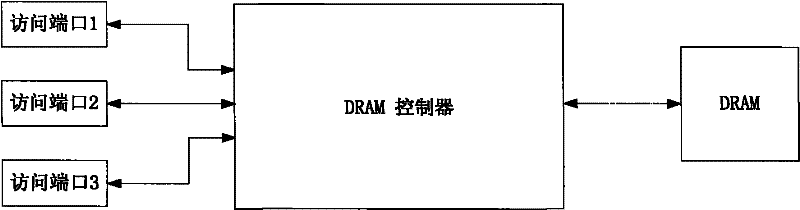

[0051] The purpose of the present invention is to provide a dynamic memory controller design method, which can effectively improve the read and write efficiency of the access port to the dynamic memory, and has strong scalability and portability.

[0052] The invention provides a method for improving the bandwidth utilization rate of a dynamic memory. The DRAM controller receives and stores the access requests of each access port while sending operation instructions to the DRAM. After sending the operation instructions being sent, the stored next an operation instruction.

[0053] Furthermore, when the DRAM controller sends an operation command to the DRAM, it does not need to wait for the data to be written in the sent operation command to be completely written into the DRAM or for the data to be requested by the sent operation command to be completely read from the DRAM.

[0054] Further, the DRAM controller sends the received request data returned by the DRAM to the corresp...

PUM

Login to View More

Login to View More Abstract

Description

Claims

Application Information

Login to View More

Login to View More - R&D

- Intellectual Property

- Life Sciences

- Materials

- Tech Scout

- Unparalleled Data Quality

- Higher Quality Content

- 60% Fewer Hallucinations

Browse by: Latest US Patents, China's latest patents, Technical Efficacy Thesaurus, Application Domain, Technology Topic, Popular Technical Reports.

© 2025 PatSnap. All rights reserved.Legal|Privacy policy|Modern Slavery Act Transparency Statement|Sitemap|About US| Contact US: help@patsnap.com