Manufacturing method for silicon epitaxial wafer of low-voltage TVS (transient voltage suppressor)

A technology of silicon epitaxial wafer and manufacturing method, applied in semiconductor/solid-state device manufacturing, electrical components, circuits, etc., can solve problems such as long-term reliability impact and damage of devices, and achieve the effect of ensuring protection voltage and reducing compensation degree

- Summary

- Abstract

- Description

- Claims

- Application Information

AI Technical Summary

Problems solved by technology

Method used

Image

Examples

Embodiment Construction

[0010] The present invention will be described in detail below in conjunction with the accompanying drawings and specific embodiments.

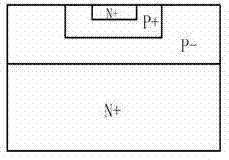

[0011] The low-voltage ESD protection device is the key device of the transient voltage suppressor (TVS), which adopts a new composite punch-through device structure (such as figure 1 ). First, a P-type high-resistance epitaxial layer is epitaxially grown on the N+ substrate, and a P+ well is formed on the epitaxial layer, and then an N+ region is formed on the well by diffusion, so that the depletion layer is depleted under reverse bias. Extend to N + substrate region, forming N + P + P - N + Four layers of structure. A thin base region width is formed through process control to reduce the breakdown voltage of the PN junction to meet the voltage requirements of low-voltage ESD devices. In addition, the lightly doped epitaxial layer P- can prevent reverse biased N + P + An avalanche breakdown occurs. Moreover, this structure is easy...

PUM

Login to View More

Login to View More Abstract

Description

Claims

Application Information

Login to View More

Login to View More - R&D

- Intellectual Property

- Life Sciences

- Materials

- Tech Scout

- Unparalleled Data Quality

- Higher Quality Content

- 60% Fewer Hallucinations

Browse by: Latest US Patents, China's latest patents, Technical Efficacy Thesaurus, Application Domain, Technology Topic, Popular Technical Reports.

© 2025 PatSnap. All rights reserved.Legal|Privacy policy|Modern Slavery Act Transparency Statement|Sitemap|About US| Contact US: help@patsnap.com