Dual-edge-triggered state-retention scan flip-flop (DET-SRSFF)

A technology of double edge triggering and scanning triggering, which is applied in pulse technology, pulse generation, electrical components, etc., can solve the problems of increased power consumption, unsatisfactory high level, and PMOS tube cannot be completely turned off, and achieves a simplified structure. , the effect of low power consumption advantage

- Summary

- Abstract

- Description

- Claims

- Application Information

AI Technical Summary

Problems solved by technology

Method used

Image

Examples

Embodiment Construction

[0043] The specific implementation manners of the present invention will be further described in detail below in conjunction with the accompanying drawings and embodiments. The following examples are used to illustrate the present invention, but are not intended to limit the scope of the present invention.

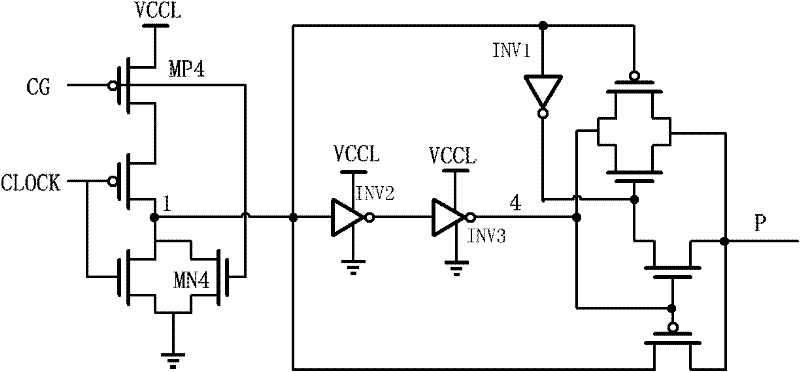

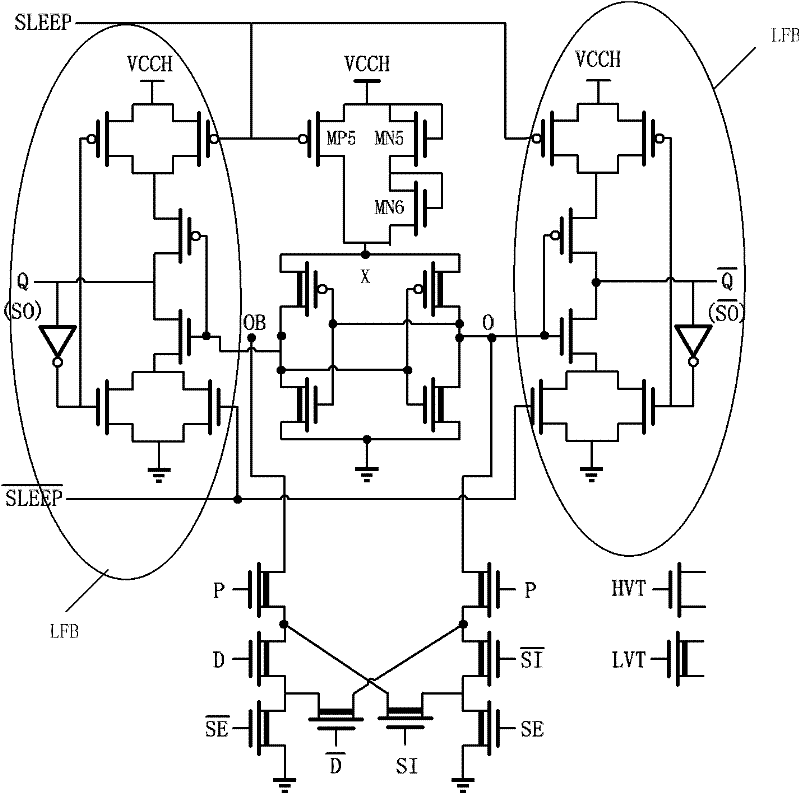

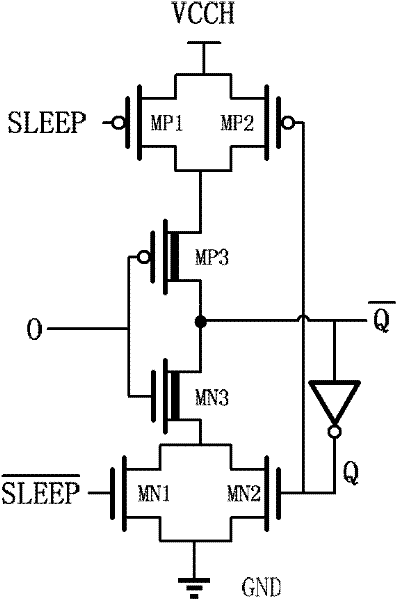

[0044] The present invention is to the pulse generating circuit of the DET-SRSFF of Fig. 1 (a) and the static latch and the input and output circuit of the DET-SRSFF of Fig. 1 (b) (specifically, the LFB circuit as the output structure is wherein figure 2 ) were improved respectively.

[0045] The improvement to Figure 1(b) is as follows: From Figure 1(b), we can see that the static latch part only disconnects the power supply VCCH due to the gate control tube, so the latched level will only appear high level loss without low level loss. Therefore, the LFB does not need to consider the situation that the NMOS cannot be completely turned off. MN1 and MN2 can be deleted, a...

PUM

Login to View More

Login to View More Abstract

Description

Claims

Application Information

Login to View More

Login to View More