Method and system for generating systems-on-a-chip (SoC) verification platform

A verification platform and template generation technology, applied in special data processing applications, instruments, electrical and digital data processing, etc., can solve problems such as poor reusability of verification platforms, save development cycles, and ensure correct results.

- Summary

- Abstract

- Description

- Claims

- Application Information

AI Technical Summary

Problems solved by technology

Method used

Image

Examples

Embodiment 1

[0036] There are many verification methods for SoC chip verification, such as RVM (Reference Verification Methodology) verification method, VMM (Verification Methodology Manual) verification method, etc. The verification platforms corresponding to different verification methods are also different. Among them, VMM is a verification methodology based on SystemVerilog, which utilizes the advantages of SystemVerilog's object-oriented programming to the greatest extent, and improves the verification productivity through a series of mechanisms. This embodiment will be described by taking the VMM verification platform as an example.

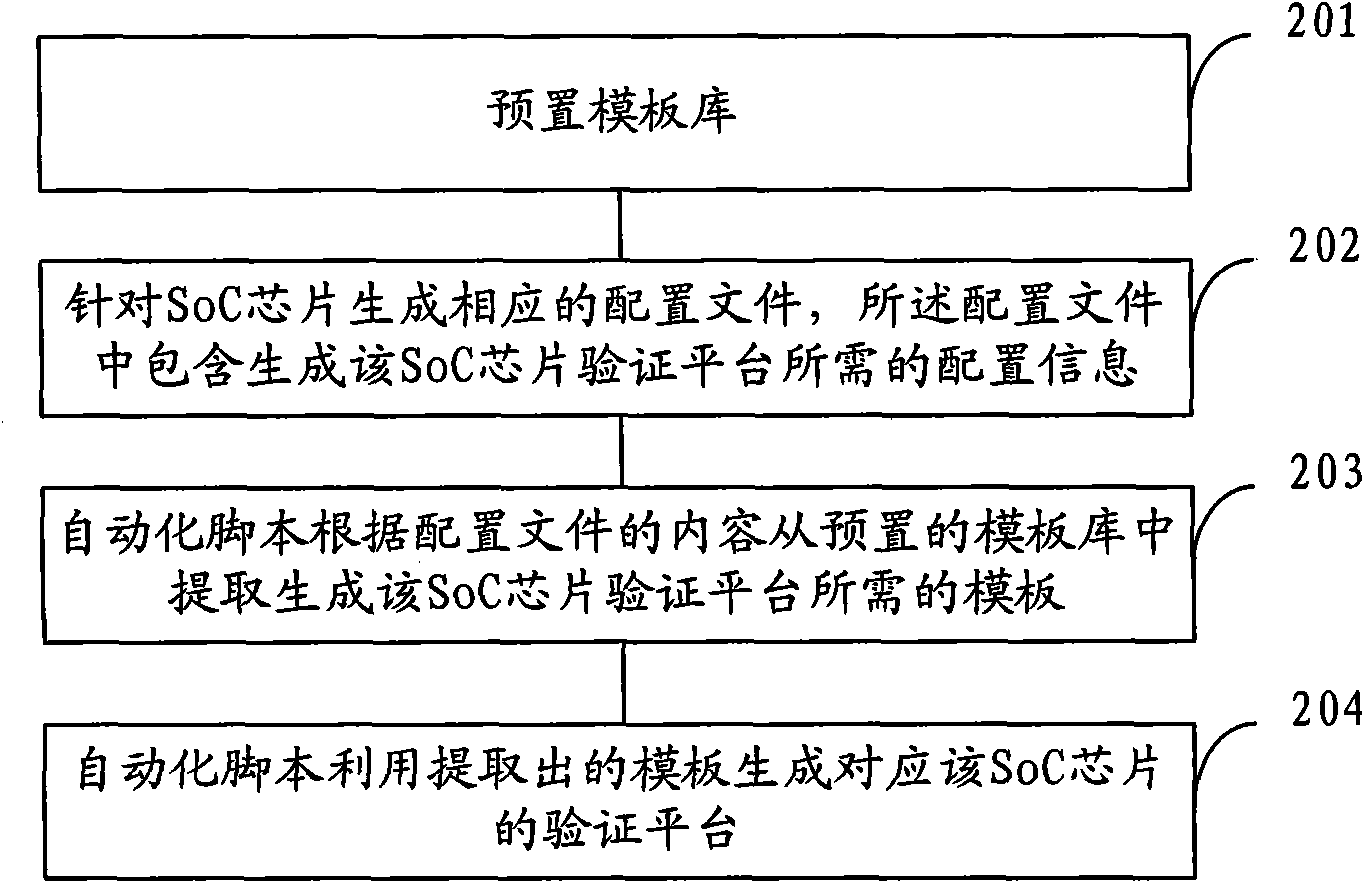

[0037] refer to figure 1 , is a schematic diagram of components of the VMM verification platform in Embodiment 1 of the present invention.

[0038] The VMM verification platform adopts a layered test platform structure, which is divided into signal layer, command layer, function layer, stimulus generation layer and test layer from bottom to top. The v...

Embodiment 2

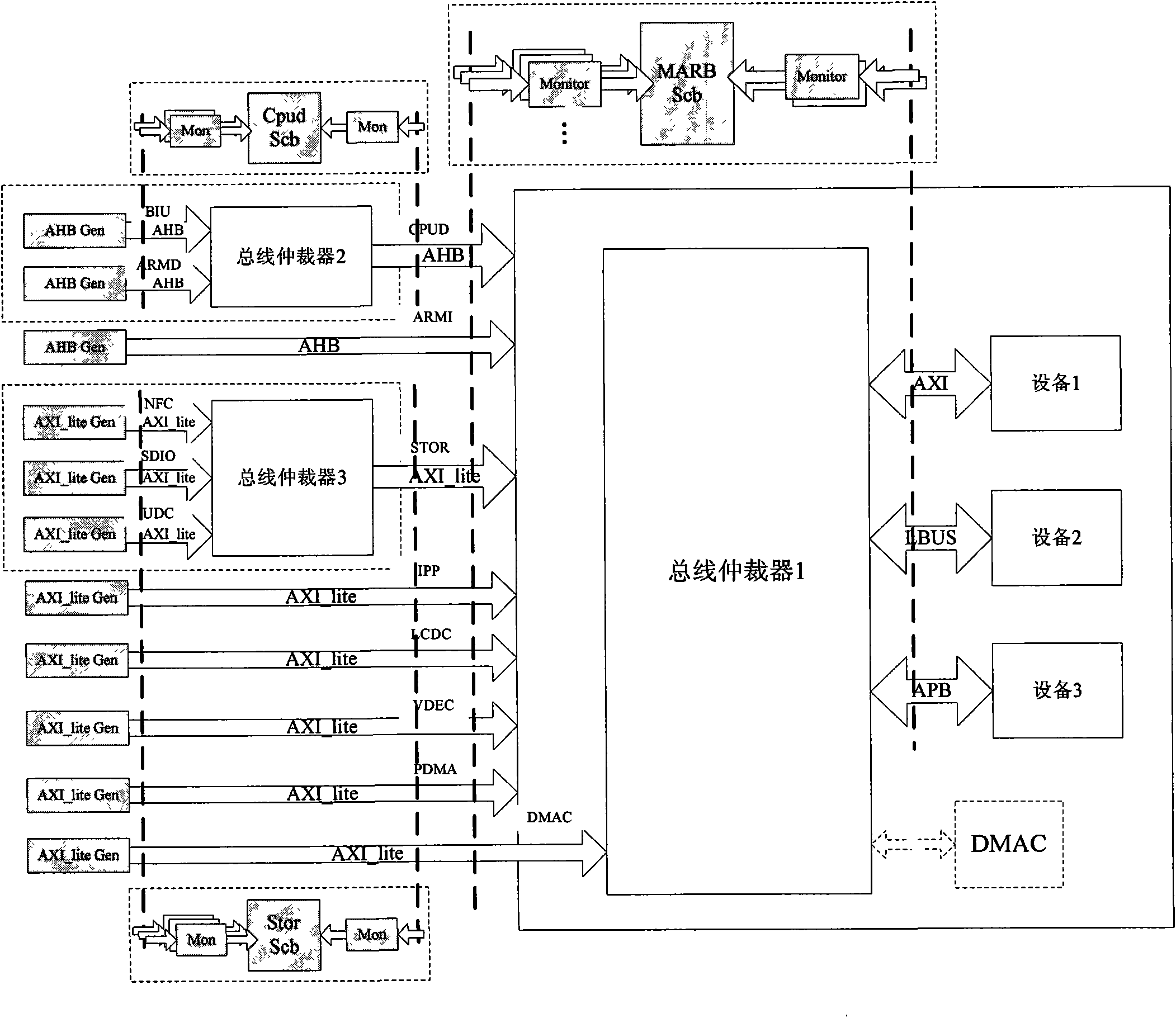

[0061] The present invention is applicable to SoC bus verification and other function verification of SoC chips. This embodiment will take the establishment of a SoC bus verification platform as an example for illustration.

[0062] According to different bus protocols, the SoC bus structure includes AMBA, AHB, AXI, APB and the mixed bus structure of these protocols. Different SoC chips have different system buses, and the templates involved are not exactly the same. For example, different chips may have an AHB bus architecture, an AXI bus architecture, or a mixed architecture of AHB and AXI; in addition, the number of masters is not exactly the same, and there may be four masters , there may also be 8 main devices; in addition, the algorithm modules are different, they may be different functional modules, or they may have the same function but use IP from different manufacturers or IP developed by themselves, and so on. These uncertainties cause different SoC chips to use di...

Embodiment 3

[0070] refer to Figure 4 , is a structural diagram of a system for generating a SoC verification platform described in Embodiment 3 of the present invention.

[0071] The system mainly includes:

[0072] Script generating unit 41, for writing the same part of different SoC verification platforms into automated scripts;

[0073] The template library 42 is used to preset different parts of different SoC verification platforms into different templates, including generating each template required by the verification platform;

[0074] The configuration unit 43 is used to generate a corresponding configuration file for the SoC chip, and the configuration file includes the configuration information required to generate the SoC chip verification platform;

[0075] The template calling unit 44 is used for automated scripts to extract from the template library 41 according to the content of the configuration file the required templates generated by the SoC chip verification platform...

PUM

Login to View More

Login to View More Abstract

Description

Claims

Application Information

Login to View More

Login to View More