Porous silicon preparing device for gross-area device transfer

A porous silicon, full-area technology, applied in semiconductor/solid-state device manufacturing, electrical components, electrolytic components, etc., can solve problems such as damage to device integrity, cracking, and inability to guarantee silicon wafer corrosion, etc., to achieve convenient operation, simple structure, To achieve the effect of overall transfer

- Summary

- Abstract

- Description

- Claims

- Application Information

AI Technical Summary

Problems solved by technology

Method used

Image

Examples

Embodiment Construction

[0018] The present invention will be described in detail below in conjunction with the accompanying drawings.

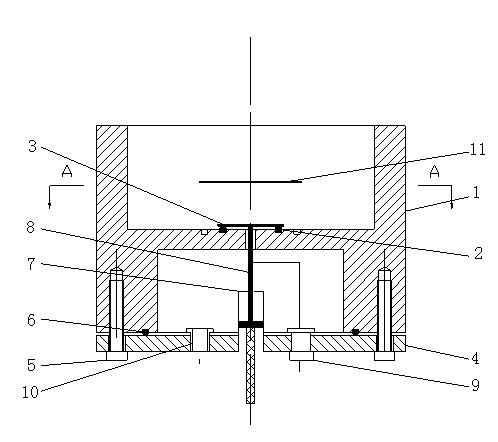

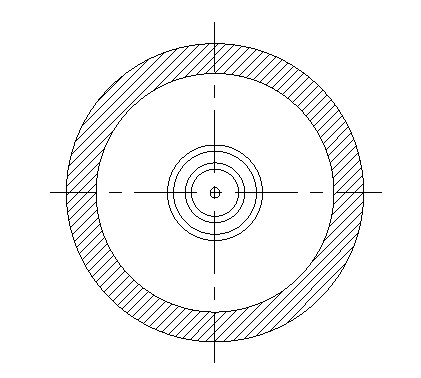

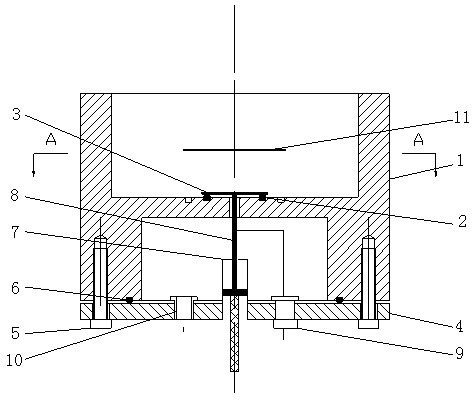

[0019] The tank body 1 uses PTFE rods of Ф150mm×100mm and processes two grooves of Ф120mm×50mm and Ф90mm×40mm at both ends through machining, among which the groove of Ф120mm×50mm is the corrosion tank and the other is the vacuum chamber . A Ф5mm through hole is drilled at the center of the partition in the two grooves for the metal probe 8 to pass through. At the bottom of the corrosion tank, a plurality of grooves with different diameters and widths are processed with the axis of the tank body as the center, and fluorine rubber rings 2 of corresponding sizes are used to realize anodic oxidation treatment of silicon wafers of different sizes. On the end face of the vacuum chamber, a groove with an inner diameter of Ф98.8mm and a width of 3.1mm is processed with the axis of the groove as the center of the circle, and the rubber sealing ring 6 of the corresponding si...

PUM

Login to View More

Login to View More Abstract

Description

Claims

Application Information

Login to View More

Login to View More - R&D

- Intellectual Property

- Life Sciences

- Materials

- Tech Scout

- Unparalleled Data Quality

- Higher Quality Content

- 60% Fewer Hallucinations

Browse by: Latest US Patents, China's latest patents, Technical Efficacy Thesaurus, Application Domain, Technology Topic, Popular Technical Reports.

© 2025 PatSnap. All rights reserved.Legal|Privacy policy|Modern Slavery Act Transparency Statement|Sitemap|About US| Contact US: help@patsnap.com