Method for implementing low power hybrid Cache of embedded device

A technology of embedded devices and implementation methods, applied in energy-saving ICT, sustainable buildings, memory address/allocation/relocation, etc., can solve problems such as unable to meet the capacity of embedded devices, achieve high cost performance, avoid performance loss, reduce The effect of power consumption

- Summary

- Abstract

- Description

- Claims

- Application Information

AI Technical Summary

Problems solved by technology

Method used

Image

Examples

Embodiment 1

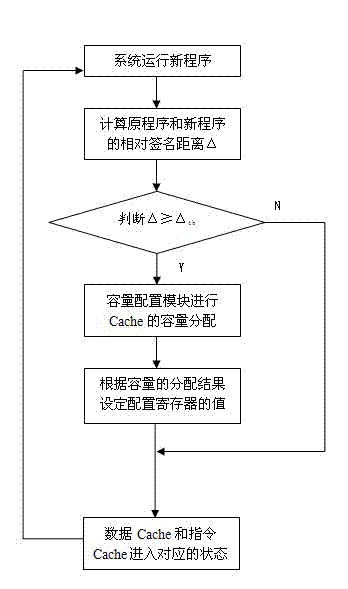

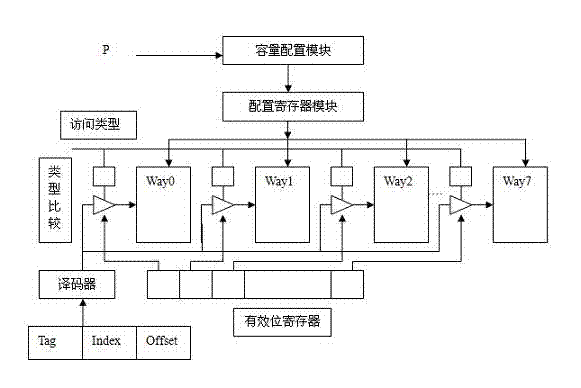

[0054] In this example, if figure 1 As shown, when an embedded device system used to establish electronic medical records runs a new program, it determines whether to enter the following low-power hybrid Cache by calculating the relative signature distance between the original program and the new program, and adding the comparison. for:

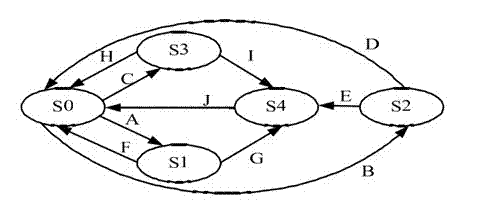

[0055] The first step is to set the instruction Cache and data Chche respectively figure 2 The states shown are: initial state S0, reserve large capacity state S1, capacity competition state S2, reserve small capacity state S3, and capacity adjustment state S4. Each state is defined as before.

[0056] The second step is to establish the following counters

[0057] A. The instruction access counter I-AC and the data access counter D-AC are respectively used to count the instruction Cache and data Cache access times in each state within the predetermined time slice;

[0058] B. The effective way counter I-MC of the instruction Cache and t...

PUM

Login to View More

Login to View More Abstract

Description

Claims

Application Information

Login to View More

Login to View More