Method for repairing establishing timing sequence

A repair method and timing technology, applied in special data processing applications, instruments, electrical digital data processing, etc., can solve problems such as lowering operating frequency and increasing chip area, and achieve the goal of improving performance, reducing design area, and reducing circuit complexity. Effect

- Summary

- Abstract

- Description

- Claims

- Application Information

AI Technical Summary

Problems solved by technology

Method used

Image

Examples

Embodiment Construction

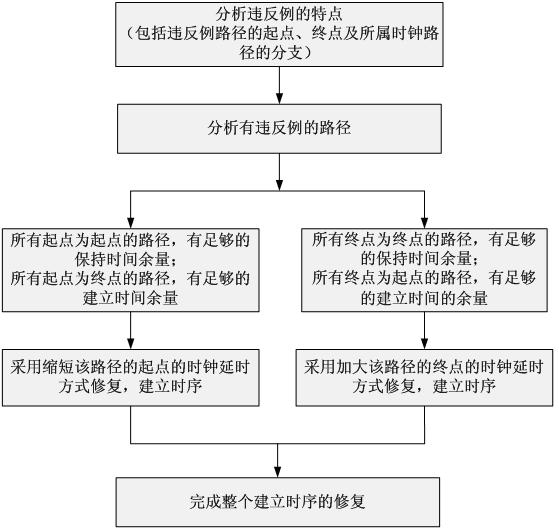

[0030] The content proposed by the present invention will be described in detail below in conjunction with the accompanying drawings. figure 1 It is a basic flowchart of a method for establishing timing repair involved in the present invention, including various implementation steps of the present invention.

[0031] (1) Analyze the characteristics of timing violations, and find out the start and end points of the violations and their clock path branches.

[0032] When the characteristics of the violation meet one of the following conditions, the timing repair method provided by the present invention can be used for repair:

[0033] ①A large number of violations occur on the interface between two physical partitions, and their related registers or latches belong to the same clock domain within their respective physical partitions;

[0034] ② A large number of violations occur on two completely independent clock branches;

[0035] ③ A large number of violations occur on memor...

PUM

Login to View More

Login to View More Abstract

Description

Claims

Application Information

Login to View More

Login to View More