Debugging method and debugging system of SOC chip

A debugging method and technology for debugging systems, which are applied in the detection of faulty computer hardware, instruments, and functional testing, etc., and can solve problems such as expensive kits

- Summary

- Abstract

- Description

- Claims

- Application Information

AI Technical Summary

Problems solved by technology

Method used

Image

Examples

Embodiment Construction

[0017] In order to understand the above-mentioned purpose, features and advantages of the present invention more clearly, the present invention will be further described in detail below in conjunction with the accompanying drawings and specific embodiments.

[0018] In the following description, many specific details are set forth in order to fully understand the present invention, but the present invention can also be implemented in other ways different from those described here, therefore, the present invention is not limited to the specific embodiments disclosed below limit.

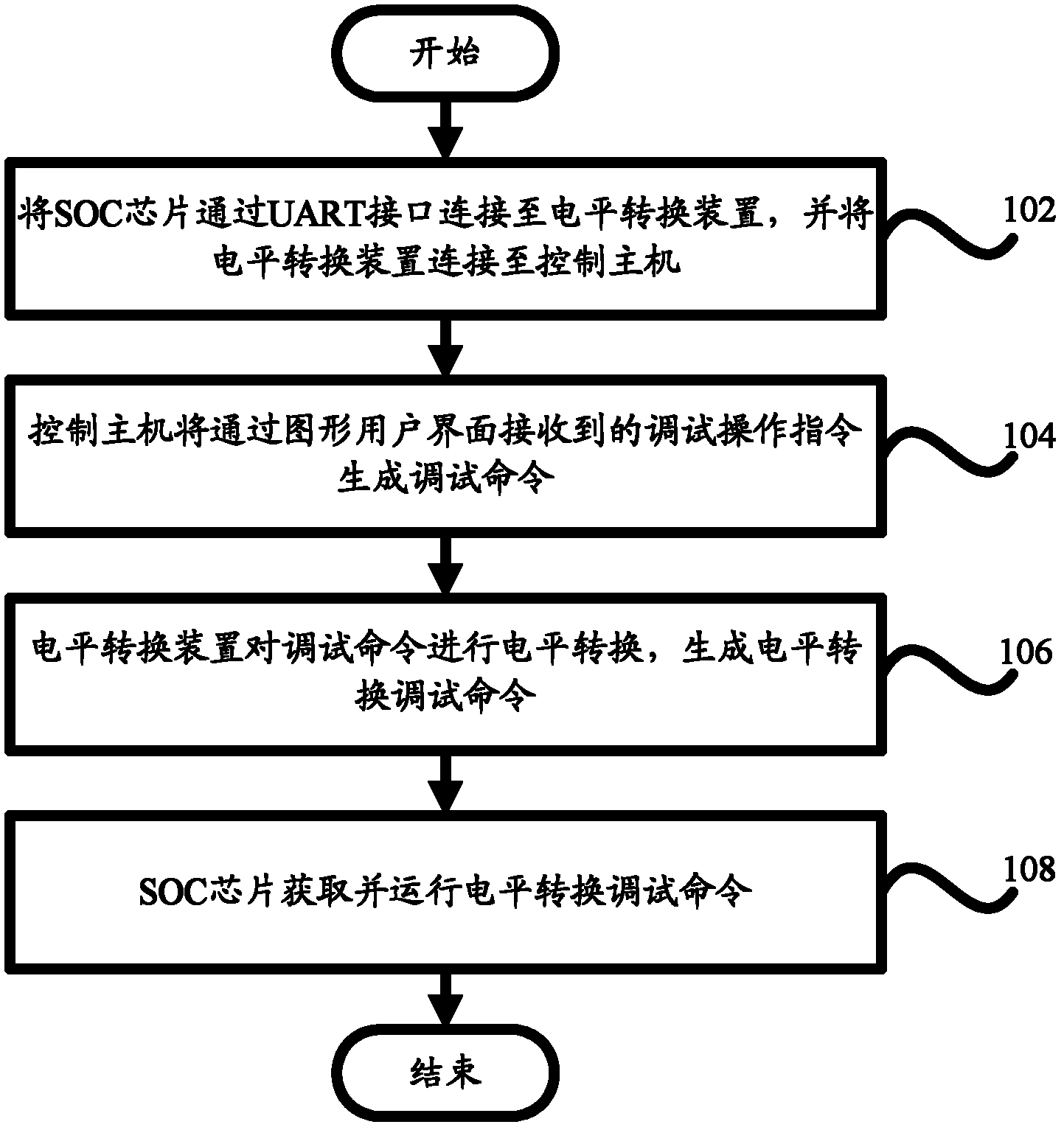

[0019] figure 1 A flow chart of a debugging method for an SOC chip according to an embodiment of the present invention is shown.

[0020] like figure 1 As shown, the debugging method of the SOC chip according to the embodiment of the present invention includes: step 102, the SOC chip is connected to the level conversion device through the UART interface, and the level conversion device is connected ...

PUM

Login to View More

Login to View More Abstract

Description

Claims

Application Information

Login to View More

Login to View More