Memory interface access control method and device

A memory access and interface control technology, applied in memory systems, instruments, memory address/allocation/relocation, etc., can solve the problem of low effective bandwidth of DDRX, achieve the effect of improving overall performance, improving access efficiency, and increasing throughput bandwidth

- Summary

- Abstract

- Description

- Claims

- Application Information

AI Technical Summary

Problems solved by technology

Method used

Image

Examples

Embodiment 1

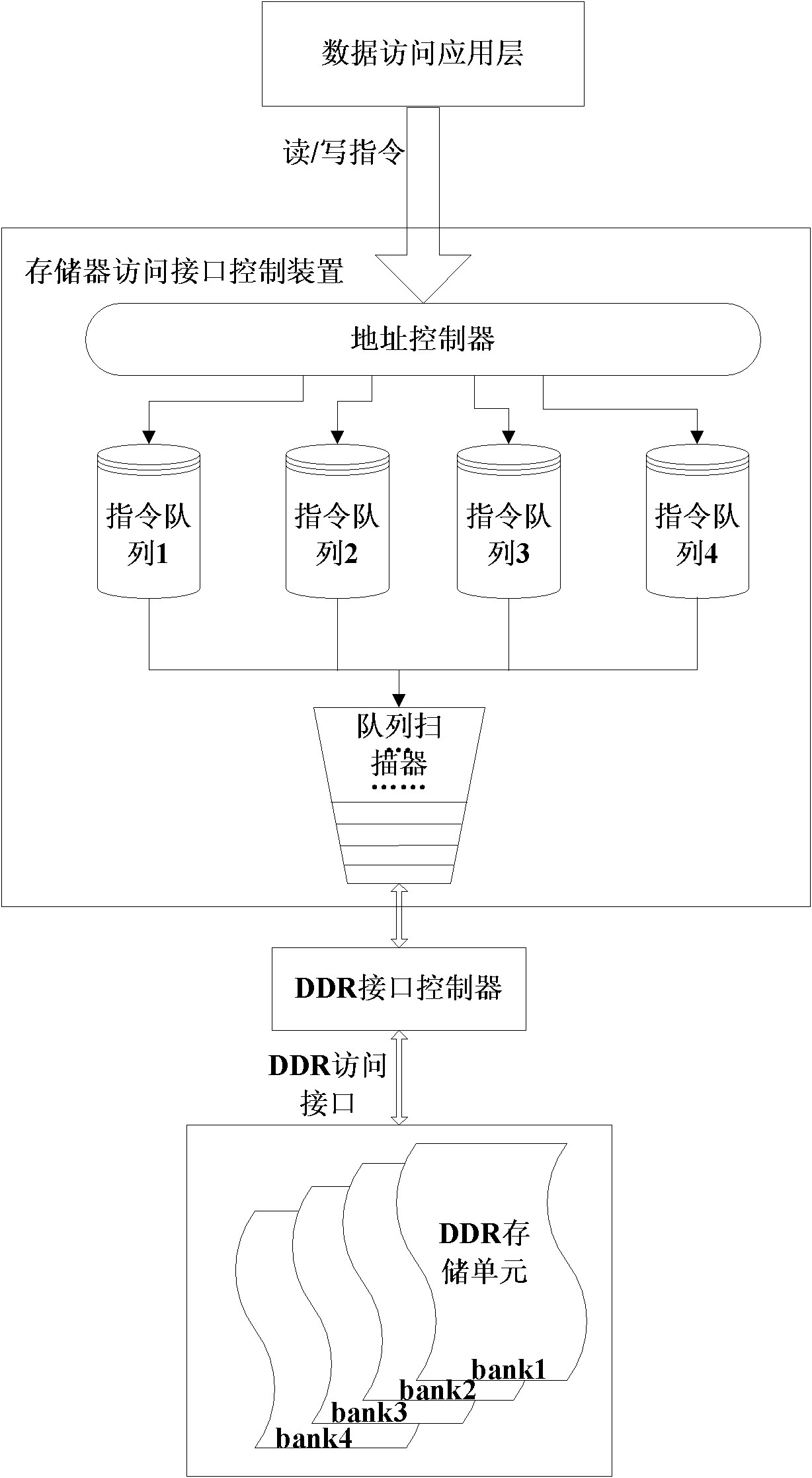

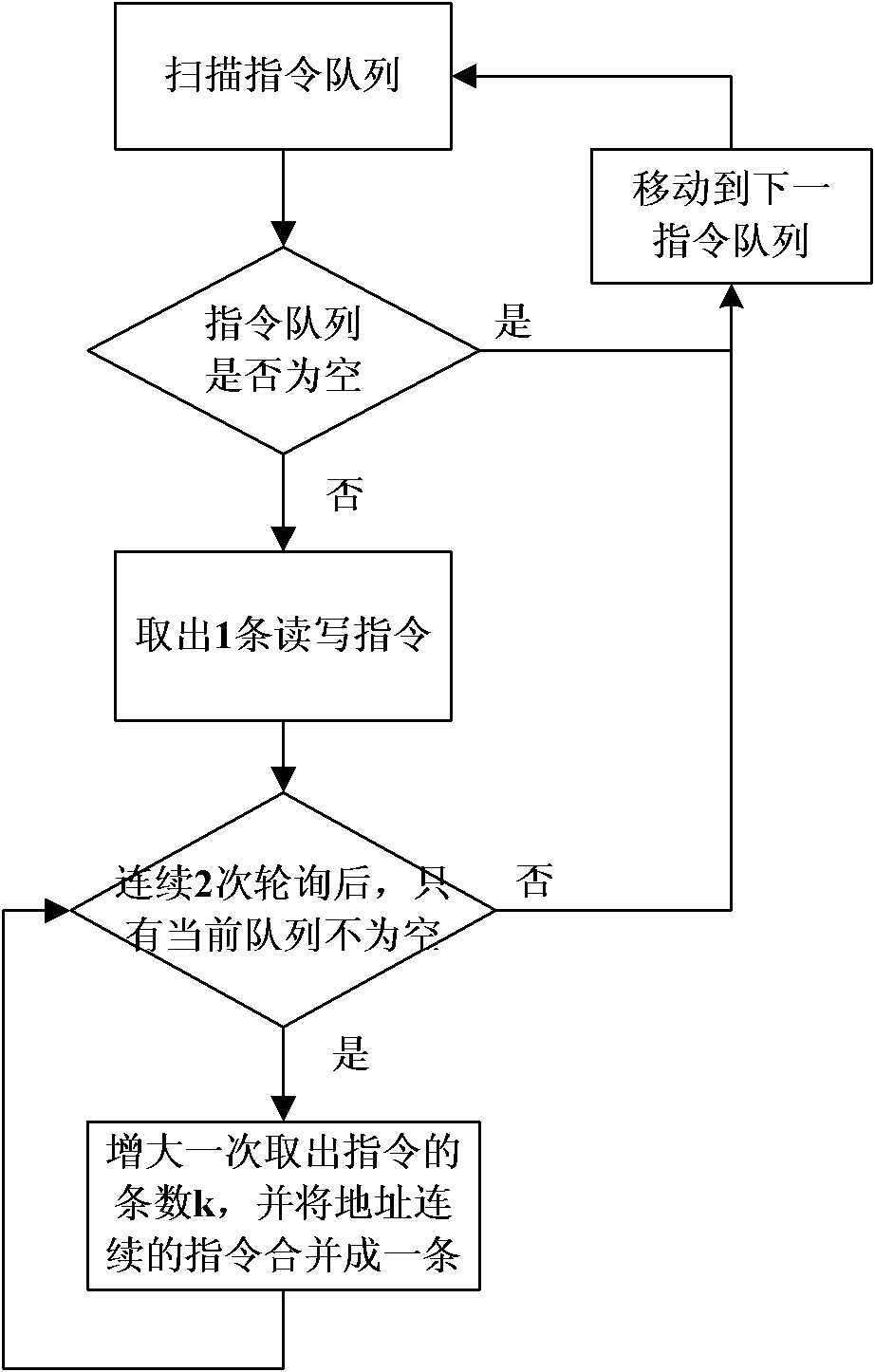

[0058] The memory interface access control device provided by the embodiment of the present invention is set between the data storage application layer and the DDRX interface controller, the read and write instructions are sent from the data storage application layer as required, and the DDRX interface controls the access interface that converts the read and write instructions into DDRX . After the device of the invention processes the read and write instructions issued by the data storage application layer, the processed read and write instructions are sent to the DDRX interface controller.

[0059] like figure 2 As shown, the memory interface access control device according to the embodiment of the present invention mainly includes three parts: an address controller, an instruction queue, and a queue scanner.

[0060] The address controller is mainly used to remap the addresses in the read and write instructions sent by the data storage application layer. The specific map...

Embodiment 2

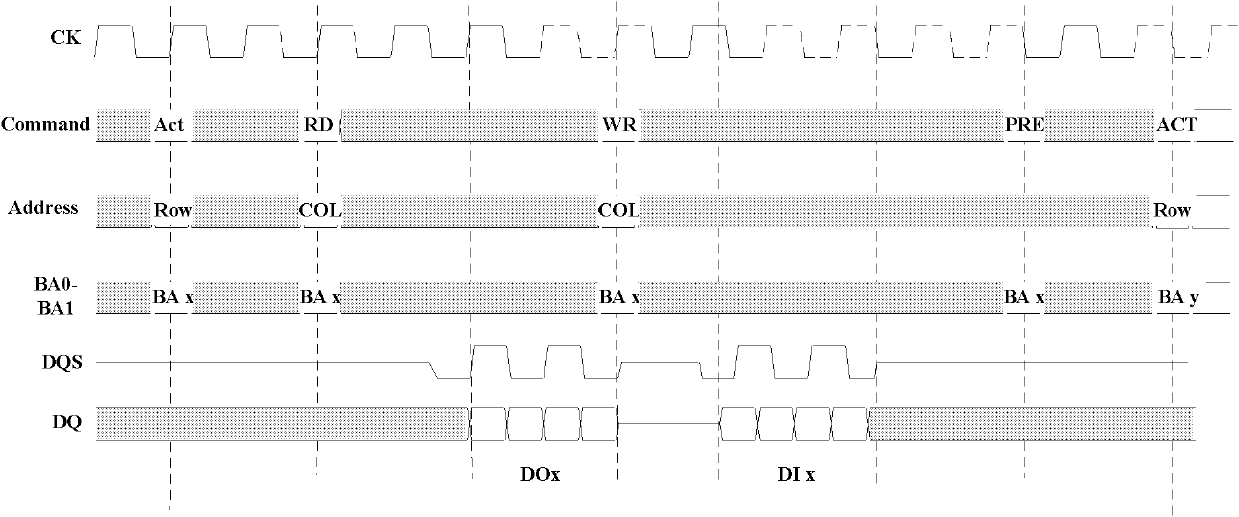

[0078] Figure 4 A DDRII device is shown as an example to describe an embodiment of this patent. The storage access of the application layer initiates read and write requests through three sets of signals, including: write command signal composed of wr_en, cmd, wr_data, wr_addr; read command signal composed of rd_en, cmd, rd_addr; read data valid indication composed of rd_data and data_valid Signal. The write command signal and the read command signal pass through the corresponding wr_cmd_fifo and rd_cmd_fifo to guide the access command flow of the application layer, which is convenient for the command controller to schedule.

[0079] The access address processed by cmd_fifo needs to be mapped. Its function is to map the address table in the application layer to different BANKs in the DDRII memory, so that the accessed data is evenly mapped in 8 different BANKs. The mapped address and the corresponding command are combined into an access command field, which is imported into...

PUM

Login to View More

Login to View More Abstract

Description

Claims

Application Information

Login to View More

Login to View More