Method for improving graphic precision of substractive process printed circuit board (PCB) by adopting dynamic etching compensation method

A subtraction method and compensation method technology, which is applied in the field of using the dynamic etching compensation method to improve the precision of the subtraction method PCB pattern, can solve the problems of the large difference in the size of the finished pattern, the difficulty of meeting the precision requirements of the isolated line and the line width, and the low precision ability. , to achieve the effect of effectively improving work efficiency, avoiding multiple modification of film, and improving production efficiency

- Summary

- Abstract

- Description

- Claims

- Application Information

AI Technical Summary

Problems solved by technology

Method used

Image

Examples

Embodiment Construction

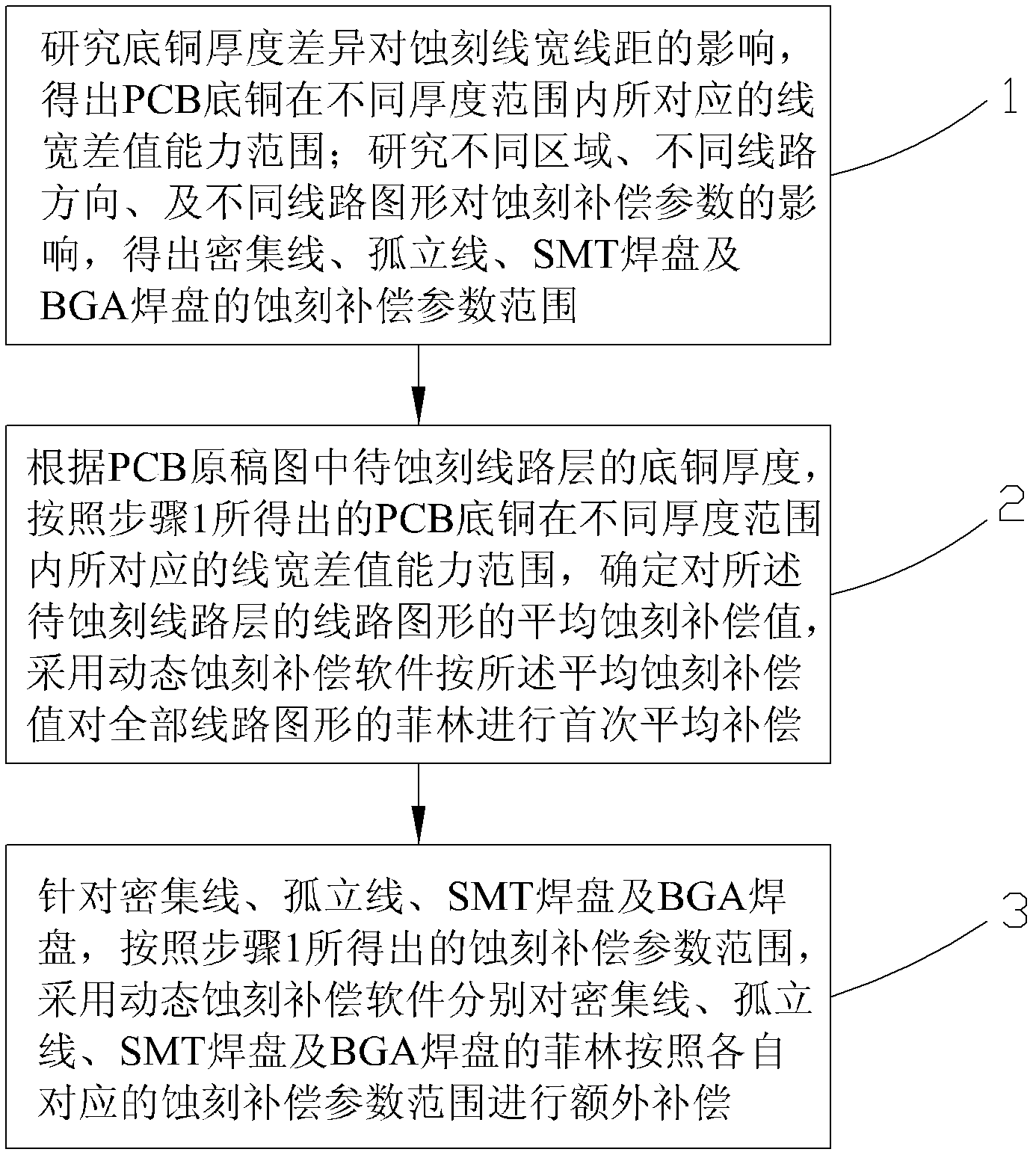

[0020] The present invention adopts the dynamic etching compensation method to improve the method for subtractive method PCB pattern precision, comprises the following steps:

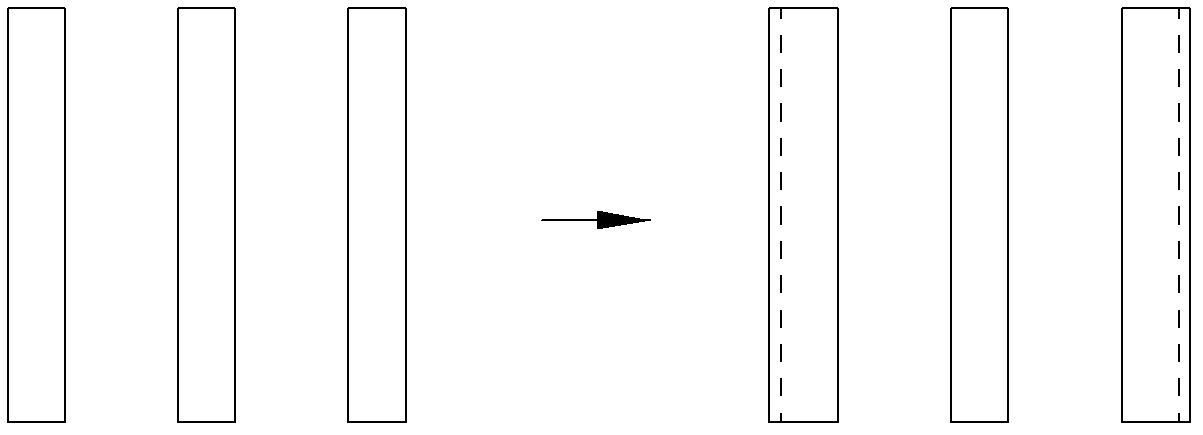

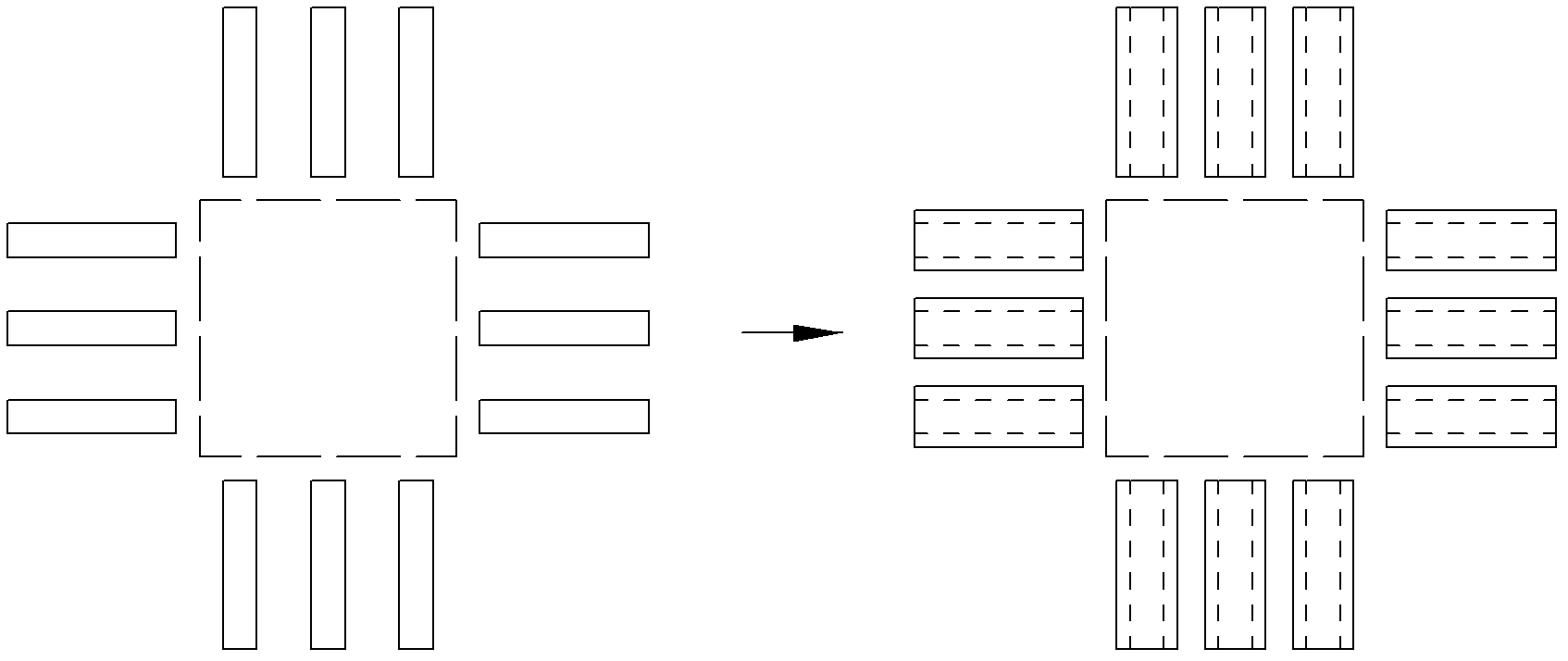

[0021] Step 1: Study the influence of bottom copper thickness difference on etching line width and line spacing, and obtain the corresponding line width difference capability range of PCB bottom copper in different thickness ranges; study different areas, different line directions, and different line patterns. Based on the influence of etching compensation parameters, the range of etching compensation parameters for dense lines, isolated lines, SMT pads and BGA pads is obtained.

[0022] The inventor designed a large number of experiments to study the line etching data of different bottom copper thicknesses. According to statistical data, the thicker the bottom copper, the greater the gap in line width, which is basically a positive correlation. When the bottom copper thickness differs by 10 μm, each lin...

PUM

Login to View More

Login to View More Abstract

Description

Claims

Application Information

Login to View More

Login to View More