Driving circuit unit, gate driving circuit and display device

A gate drive circuit and drive circuit technology, applied in static indicators, instruments, etc., can solve the problems of increasing the rise time of the output signal pulse, increasing the total power consumption of the circuit, reducing the drive current, etc. The effect of widening the effective pulse width and reducing the total power consumption

- Summary

- Abstract

- Description

- Claims

- Application Information

AI Technical Summary

Problems solved by technology

Method used

Image

Examples

Embodiment 1

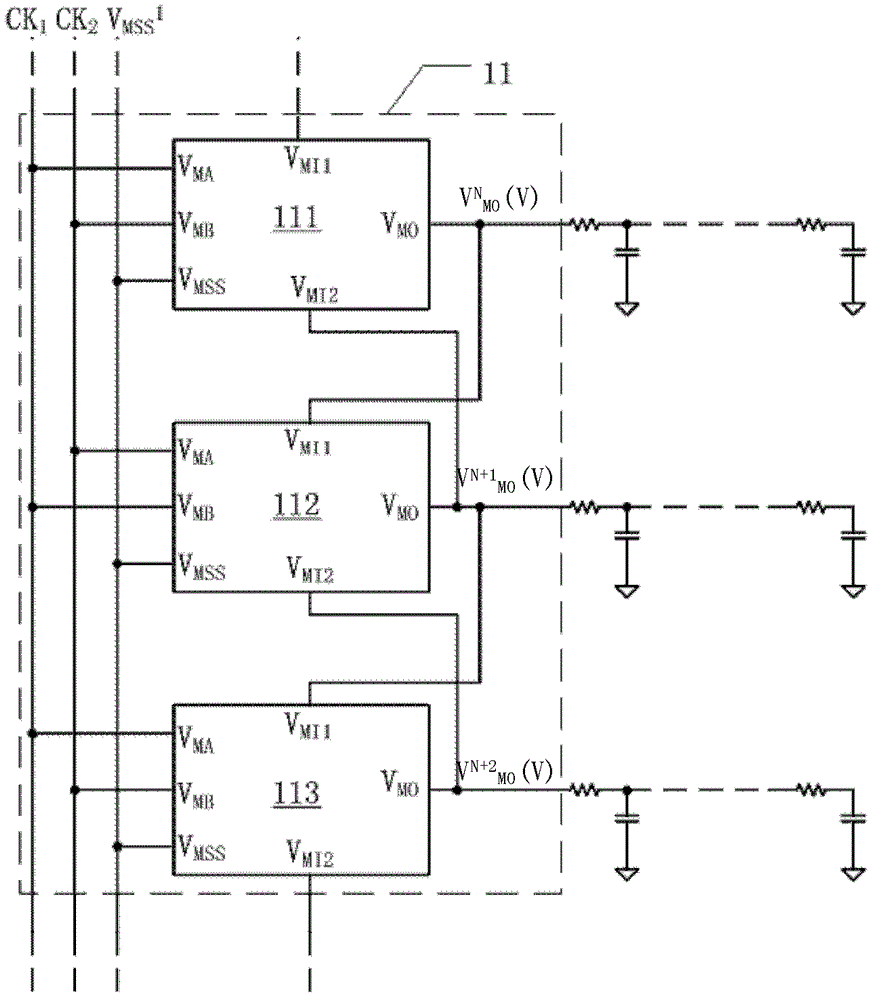

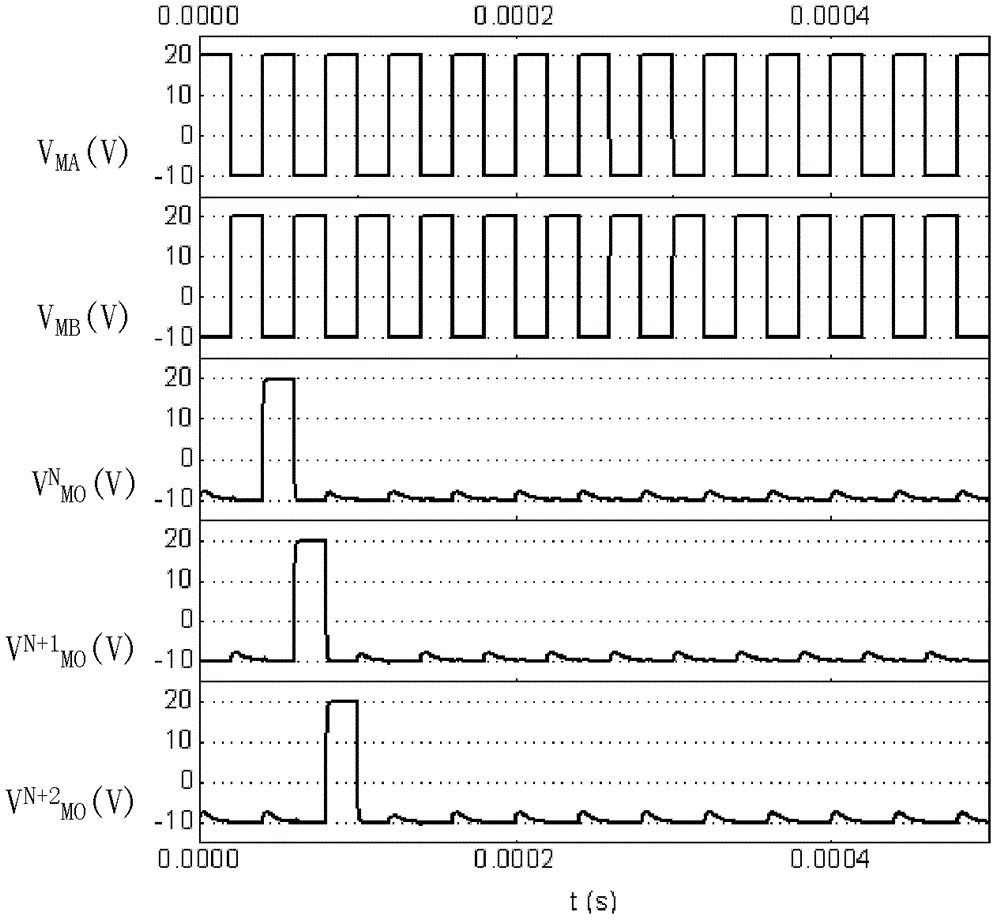

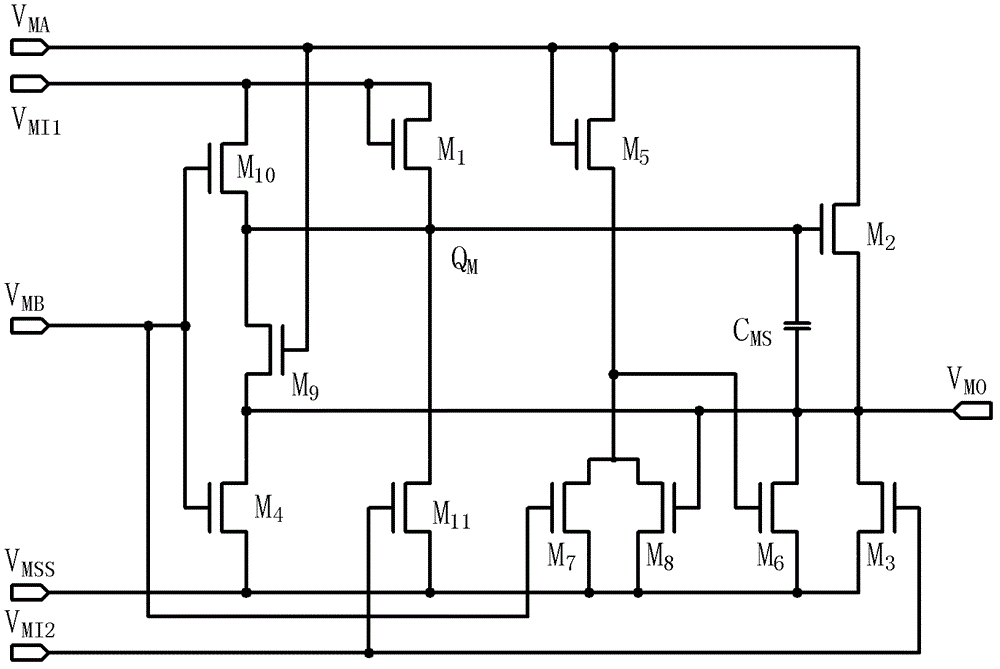

[0055] Such as Figure 7 As shown, the drive circuit unit includes five modules: an input module 71 , a drive module 72 , a discharge module 73 , a clock feedthrough suppression module 74 and a low level maintenance module 75 . Figure 8 is the timing diagram of the drive circuit unit. Detailed description below Figure 7 The operation of the circuit shown.

[0056] The first input signal V I1 is the output signal V of the N-1th stage drive circuit unit N-1 O , the second input signal V I2 is the output signal V of the N+1th level drive circuit unit N+1 O , the third input signal V I3 is the output signal V of the N+2th stage drive circuit unit N+2 O . Among them, the N-1th stage output signal V N-1 O , Nth stage output signal V N O , output signal V of stage N+1 N+1 O and output signal V of the N+2 stage N+2 O Both are pulse signals with a pulse width of T / 2, and they are overlapped sequentially for a time of T / 4. The first clock signal V A , the third cl...

Embodiment 2

[0078] Figure 9 Shown is the structure of the drive circuit unit of the second embodiment, including an input module 91, a drive module 92, a discharge module 93, a clock feedthrough suppression module 94 and a low level maintenance module 95, wherein the drive module 92, the discharge module 93, The clock feedthrough suppression module 94 and the low-level maintenance module 95 still use the circuit modules described in Embodiment 1, which will not be repeated here.

[0079] Such as Figure 9 As shown, the input module circuit unit 91 includes a first transistor T 1 , the fourth input signal V I4 , where the fourth input signal V I4 Input the output signal V of the N-2 drive circuit unit N-2 O . Figure 9 The timing diagram of the drive circuit unit is shown in Figure 10 shown. This embodiment and embodiment one (namely Figure 7 The difference in the circuit structure of the shown drive circuit unit) is: the first transistor T in the input module 91 1 The gate an...

Embodiment 3

[0081] Figure 11 Shown is the structure of the drive circuit unit of the third embodiment, including an input module 111, a drive module 112, a discharge module 113, a clock feedthrough suppression module 114 and a low level maintenance module 115, wherein the input module 111, the drive module 112, The clock feedthrough suppression module 114 and the low-level maintenance module 115 still use the circuit modules described in Embodiment 1, which will not be repeated here.

[0082] Such as Figure 11 As shown, the unit circuit of the discharge module 113 includes: a third transistor T 3 , two input signals (the second clock signal V B , the third input signal V I3 ). Figure 11 The timing diagram of the drive circuit unit is shown in Figure 12 shown. Figure 12 The timing sequence of the driving circuit unit shown is similar to that of the second embodiment, and will not be repeated here. Compared with the second embodiment, the advantage of this embodiment is: because...

PUM

Login to View More

Login to View More Abstract

Description

Claims

Application Information

Login to View More

Login to View More