Patents

Literature

81 results about "Clock feedthrough" patented technology

Efficacy Topic

Property

Owner

Technical Advancement

Application Domain

Technology Topic

Technology Field Word

Patent Country/Region

Patent Type

Patent Status

Application Year

Inventor

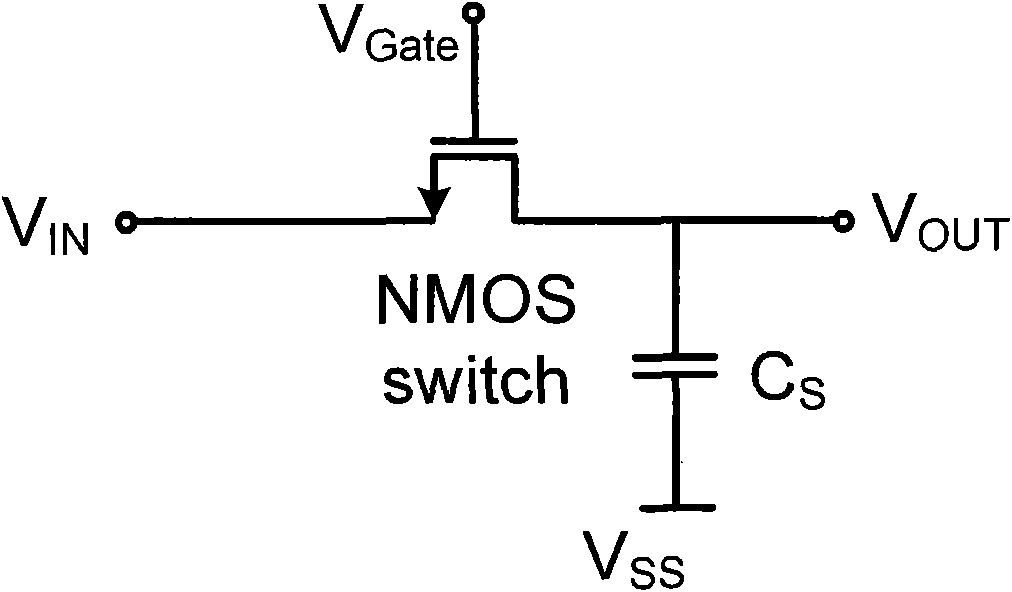

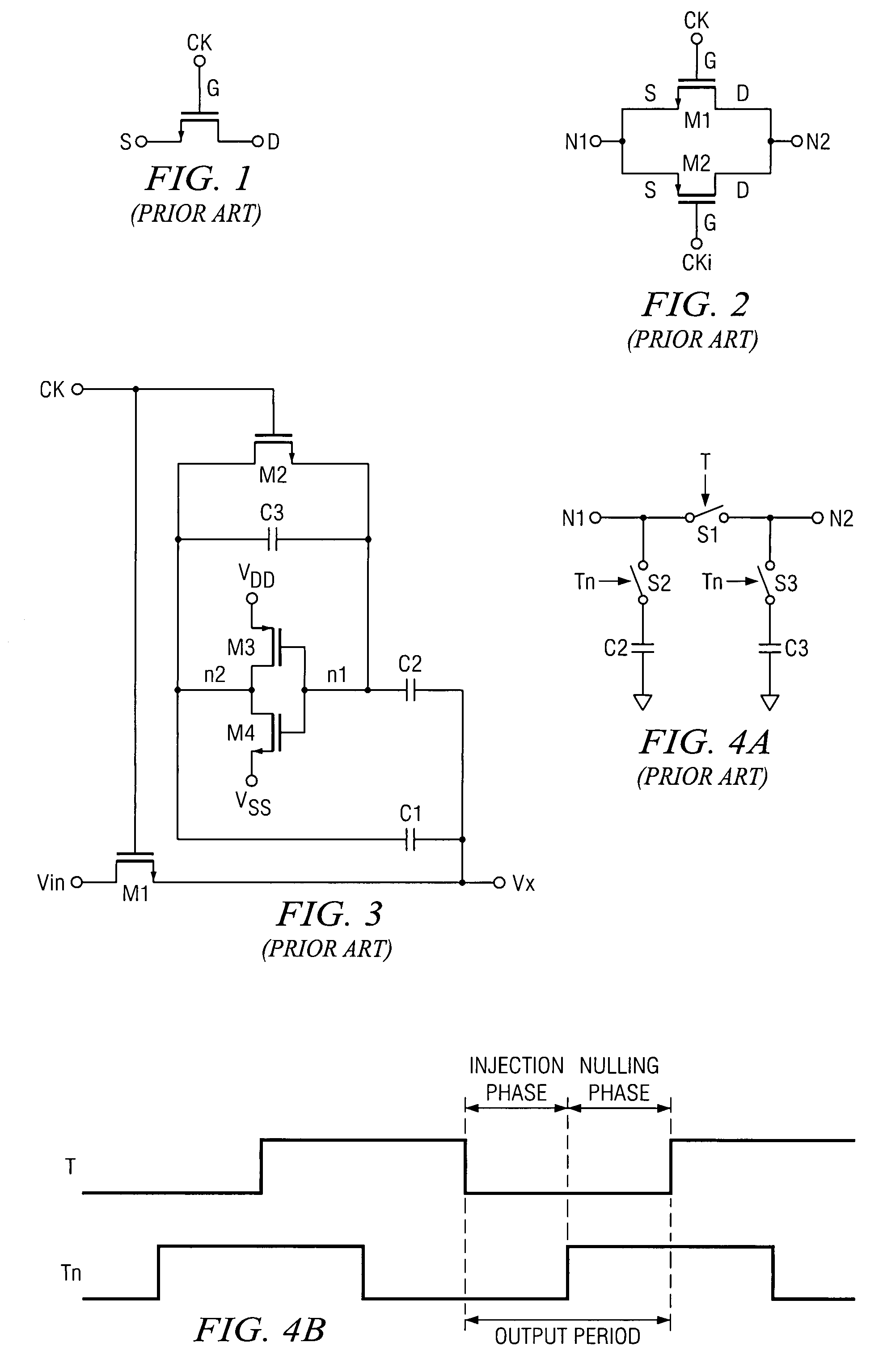

In analog electronics, Clock feedthrough is the result of the coupling between control signals on the analog switch and analog signal passing through the switch. In digital electronics, clock feedthrough is the coupling of the clock signal to the nodes where coupling is not intended. Such coupling happens because of the gate-to-source capacitance, interconnects parasitic capacitance or because of the substrate coupling. Clock feedthrough is generally considered harmful. Methods to reduce clock feedthrough include...

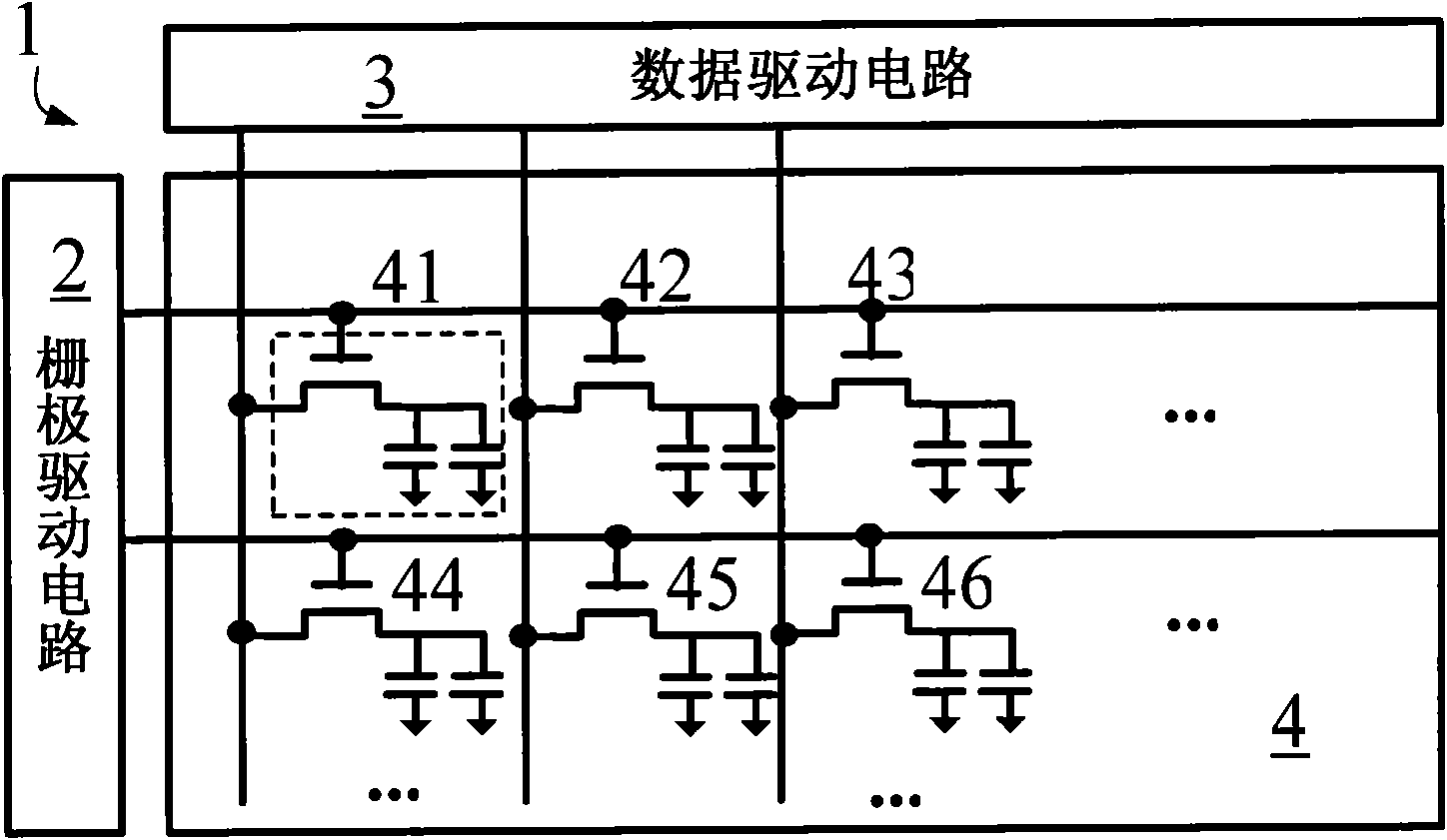

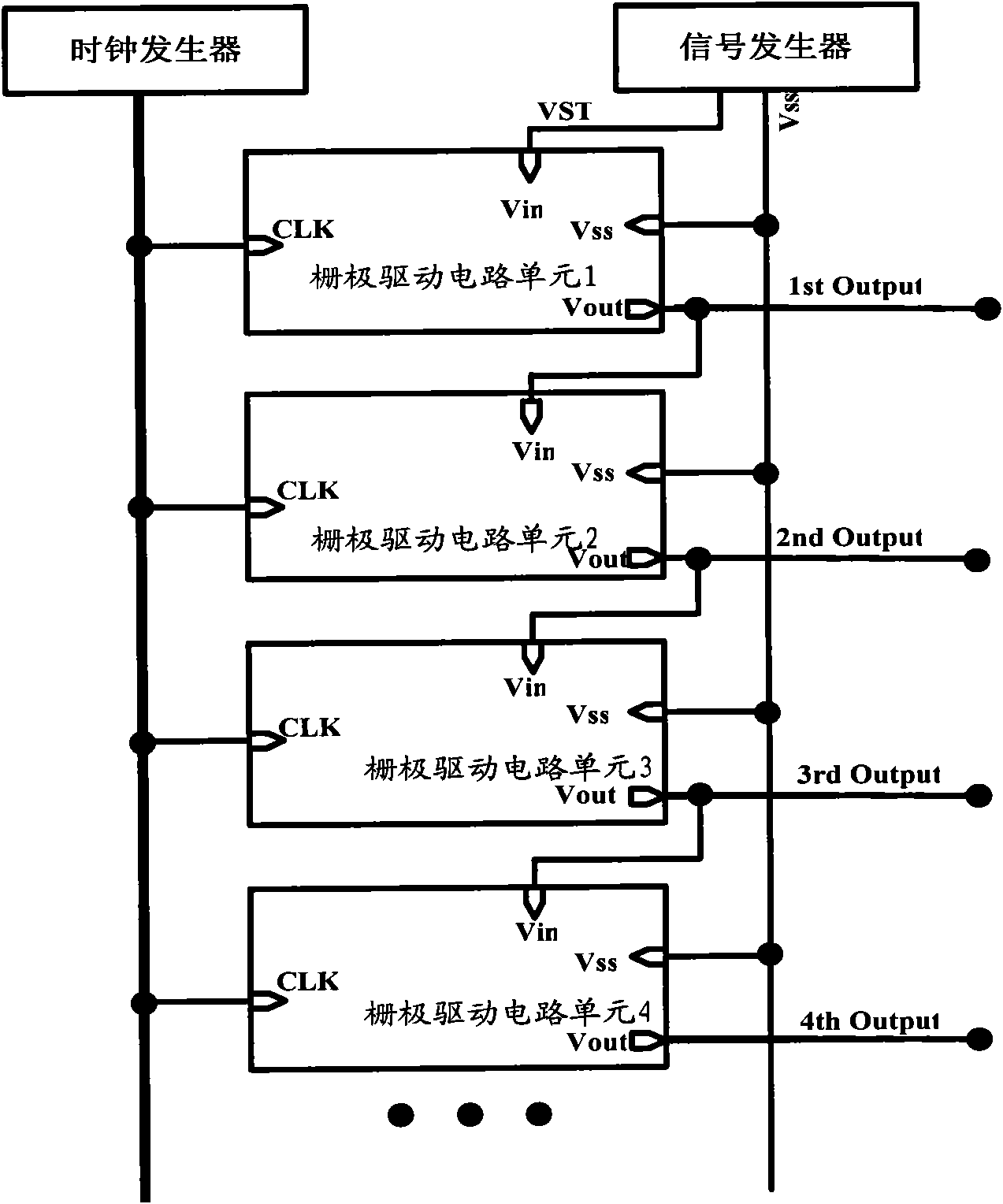

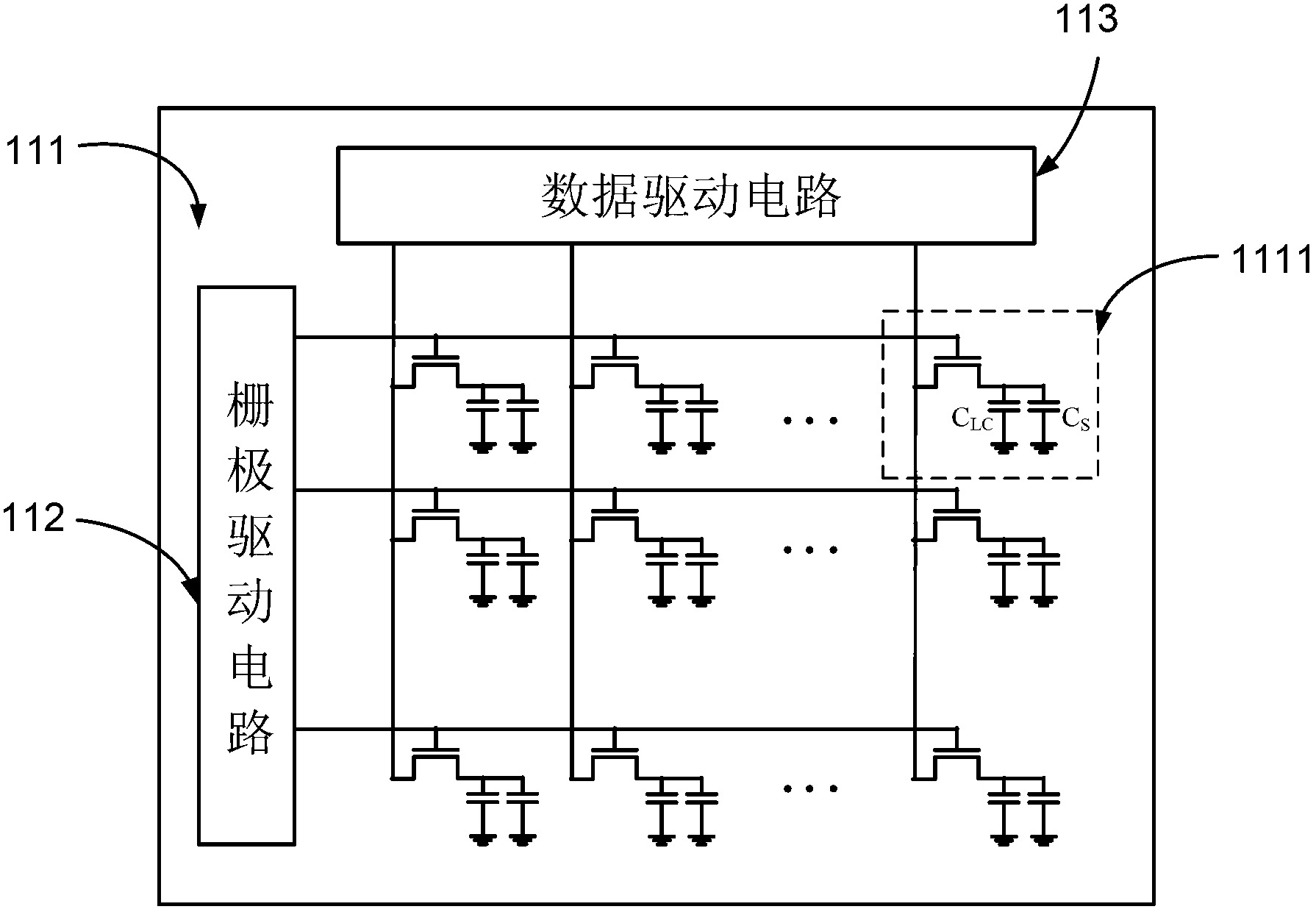

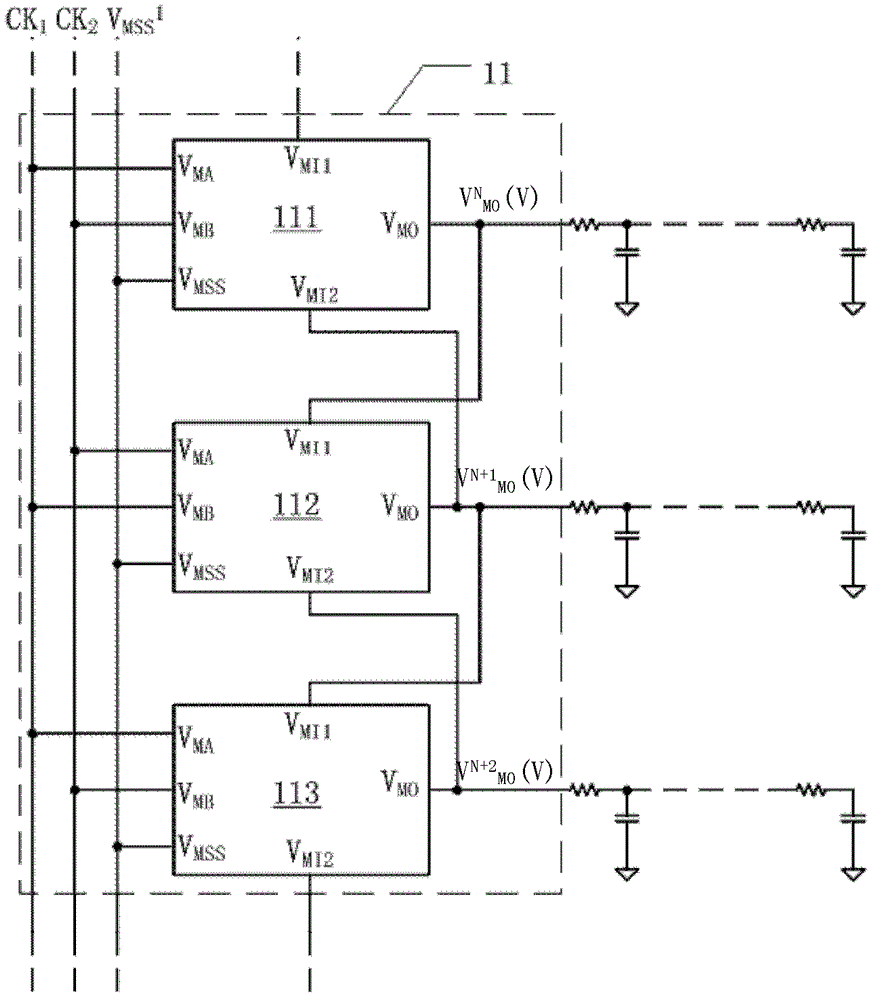

Grid electrode driving circuit unit, a grid electrode driving circuit and a display device

InactiveCN101783124AReduce complexityReduce areaStatic indicating devicesDigital storageDisplay deviceDriving circuit

The invention discloses a grid electrode driving circuit unit, a grid electrode driving circuit and a display device. The grid electrode driving circuit unit comprises a first clock signal control module, an input signal control module, a third clock signal control module and a fourth clock signal control module, wherein the first clock signal control module comprises a driving unit and a clock feed-through inhabiting unit, the driving unit transfers a first clock signal to an output port after being switched on, the clock feed-through inhabiting unit couples the control end of the driving unit to a signal output interface under the control of the first clock signal, the input signal control module provides the driving voltage for the driving unit under the control of an input pulse signal, the third clock signal control module provides the shutdown voltage for the driving unit under the control of a third clock signal, the third clock signal lags two phases behind the first clock signal, the fourth clock signal control module pulls down the voltage of the signal output interface under the control of a fourth clock signal, and the fourth clock signal is one phase ahead the first clock signal. The invention has the advantages of simple design, small power consumption and high stability.

Owner:PEKING UNIV SHENZHEN GRADUATE SCHOOL +1

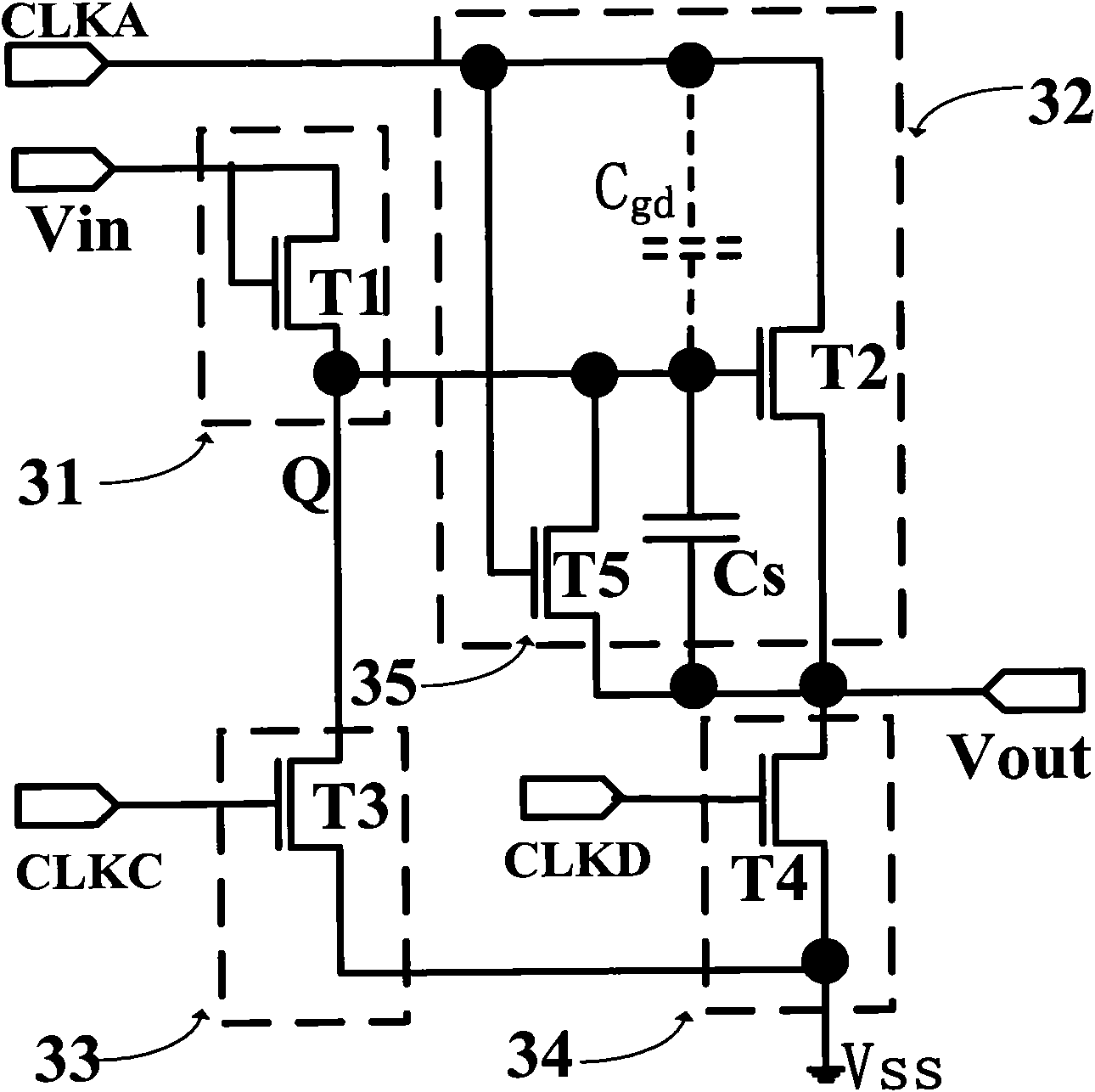

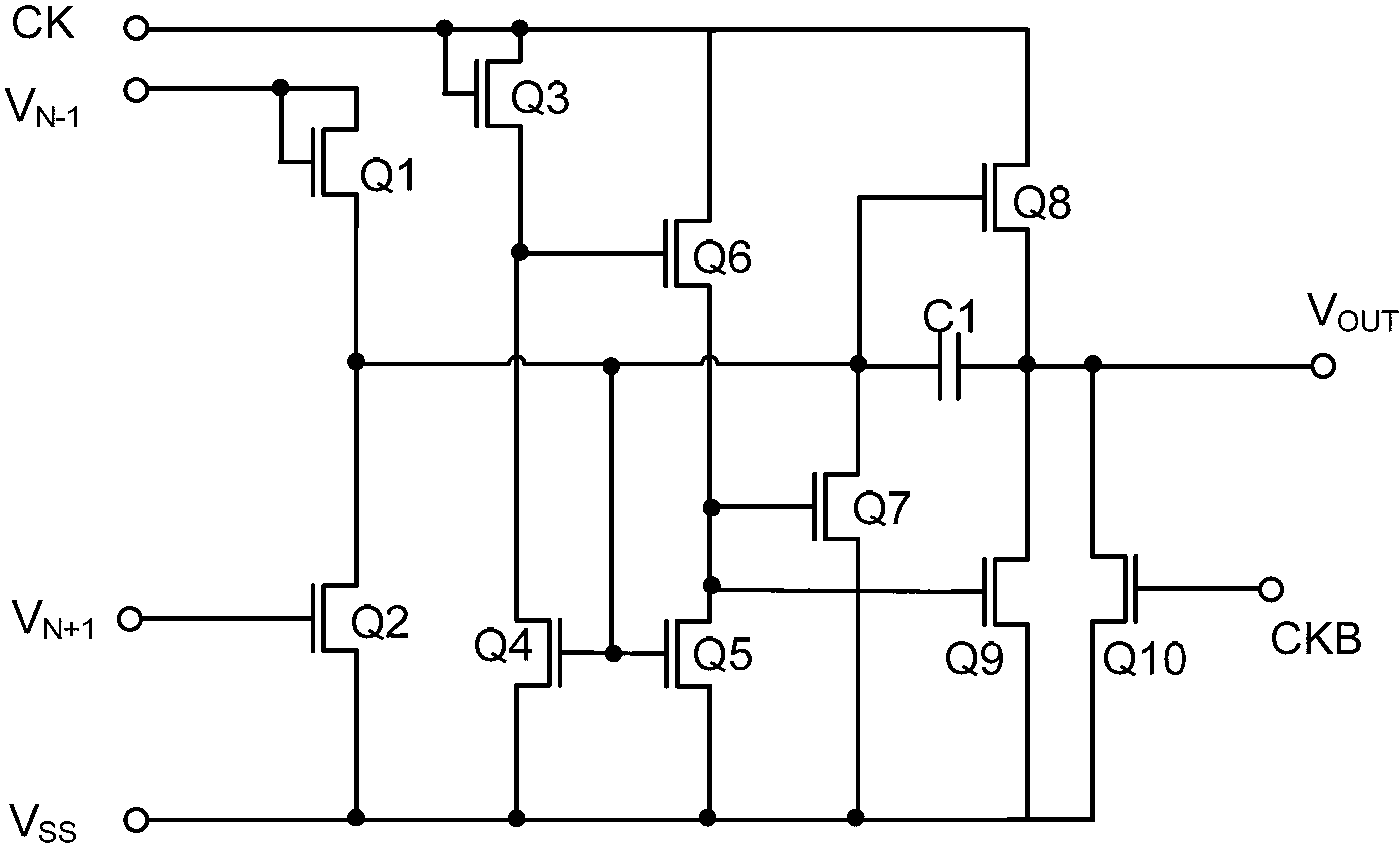

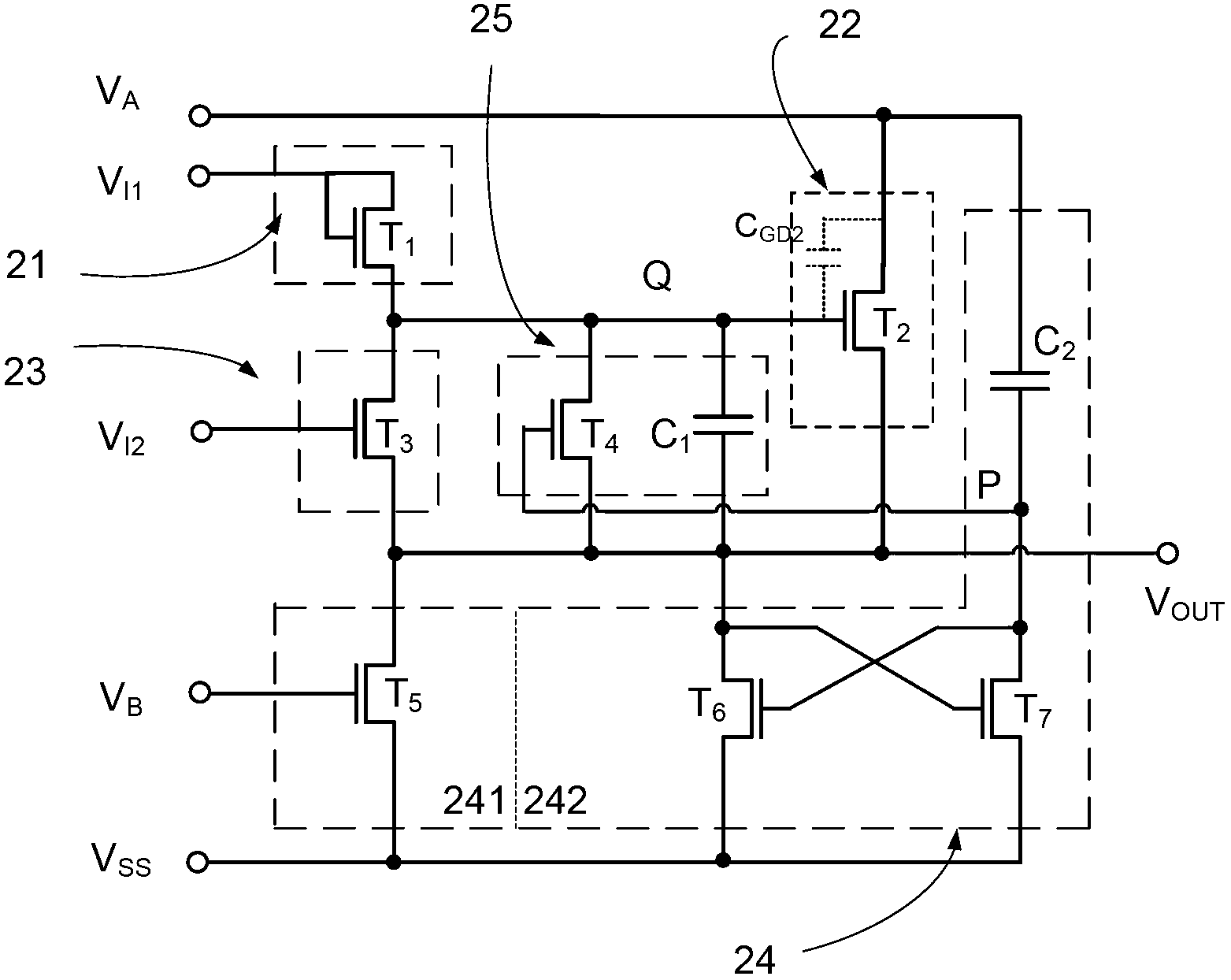

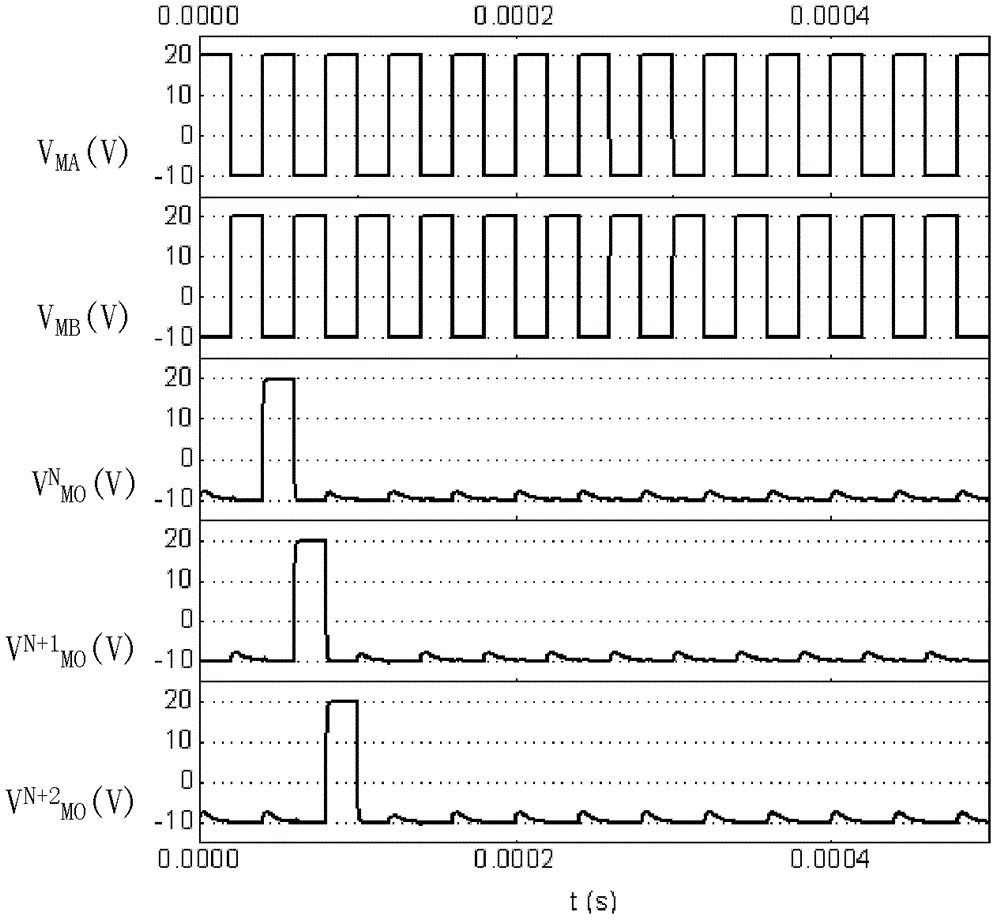

Shift register cell, gate driving circuit, data driving circuit and display

ActiveCN103077689AShorten the timeShorten rise timeStatic indicating devicesDigital storageShift registerElectricity

The invention discloses a shift register cell, a gate driving circuit, a data driving circuit and a display, wherein the shift register cell comprises a first signal input end, a second signal input end, a first clock signal input end, a pull-down control signal input end, a signal output end (VOUT), an input module (21), a driving module (22), a driving control end pull-down delay module (23), a clock feed through inhibition module (25) and a low-level retention module (24). According to the invention, the signal output end can quickly discharge by a charging transistor in the driving module by prolonging discharging time for a driving control end in the shift register cell; and the electricity leakage of the transistor in the clock feed through inhibition module is inhibited, so that work speed and integration degree of the circuit are improved.

Owner:PEKING UNIV SHENZHEN GRADUATE SCHOOL

Driving circuit unit, gate driving circuit and display device

The invention relates to a gate driving circuit and a display device. The gate driving circuit comprises multiple levels of driving circuit units connected in series. Each level of units comprises an inputting module for providing threshold voltage of a driving module, a driving module for responding to the threshold voltage and for sending a first clock signal to a signal outputting interface, a discharging module for responding to an output signal or a clock signal of an adjacent level and for coupling a control terminal of the driving module to a first voltage source, a clock feedthrough inhibiting module for stablizing the potential of the control terminal of the driving module under the control of the clock signal and the output signal of the adjacent level, and a low level maintaining module for stablizing the output signal at the potential of the first voltage source under the control of the clock signal. The driving circuit unit, gate driving circuit and display device provided by the invention employ single driving tube to realize the fast pull-up and pull-down of the output signal with sequential coordination, reducing the delay time of the rise and fall of the output signal at a low temperature, and employs the clock feedthrough inhibiting module to stablize the gate potential of the driving tube, reducing the corresponding dynamic power consumption.

Owner:PEKING UNIV SHENZHEN GRADUATE SCHOOL +1

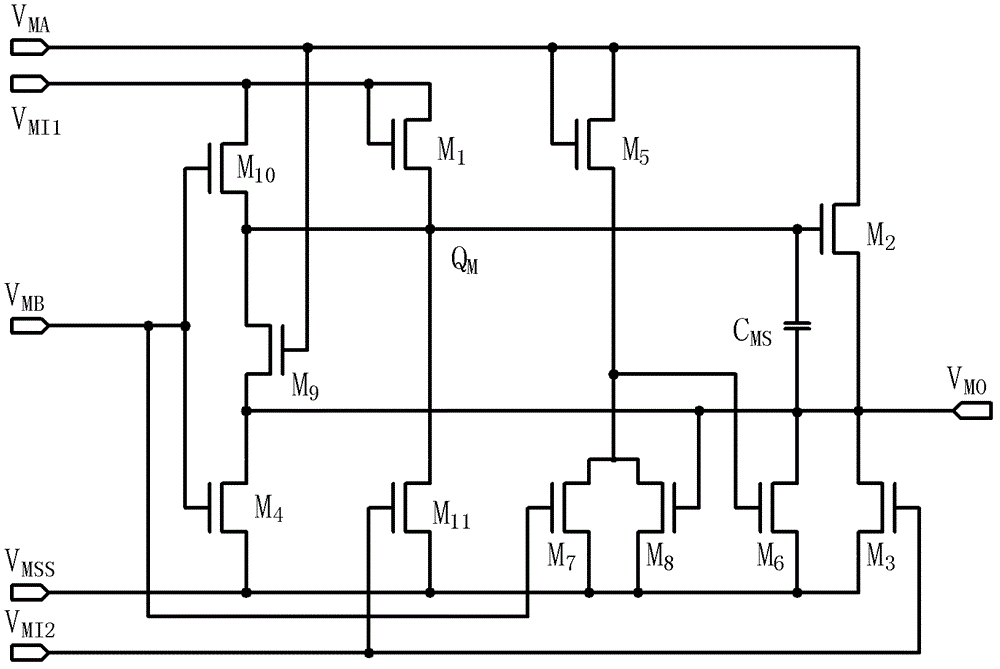

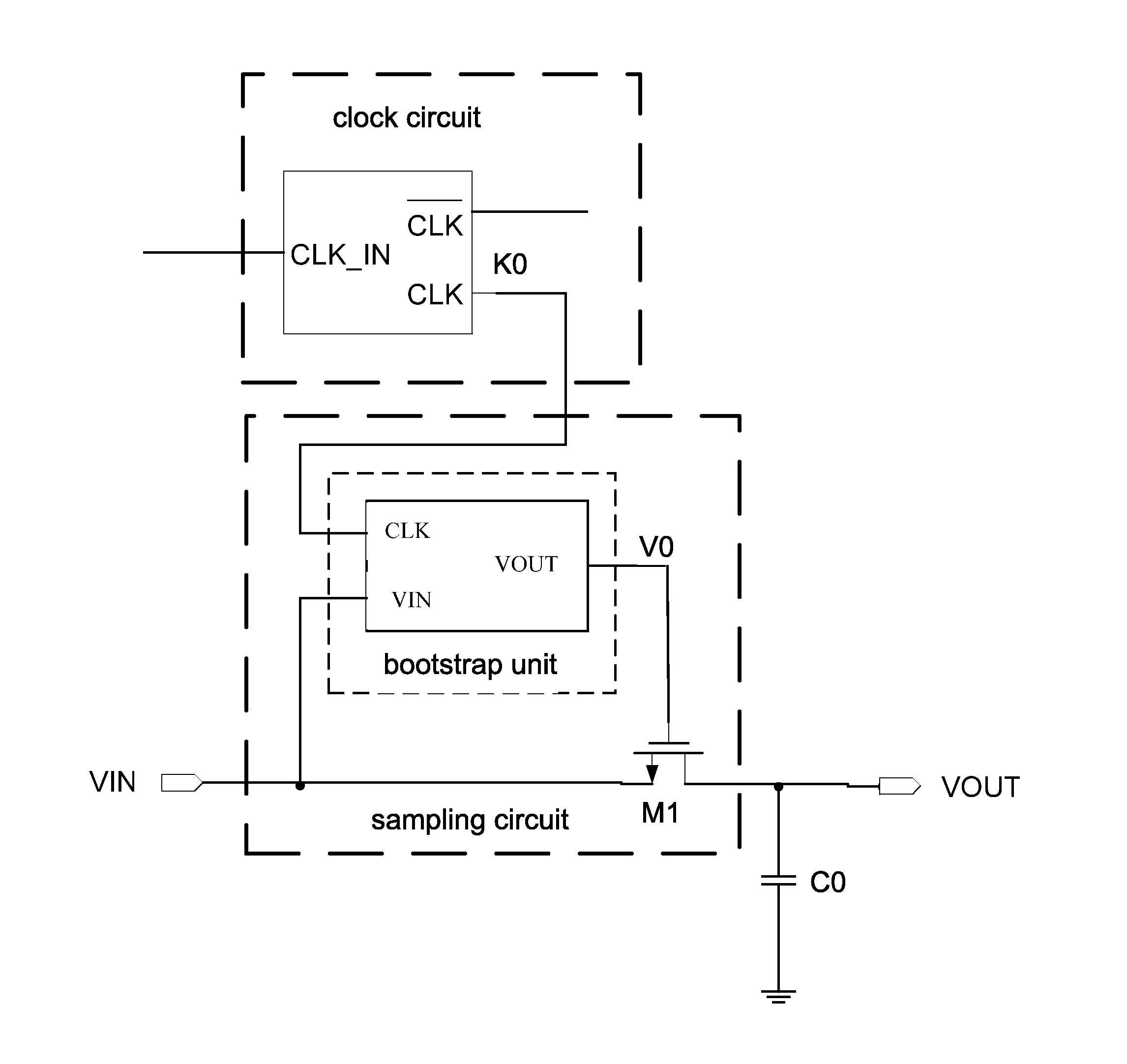

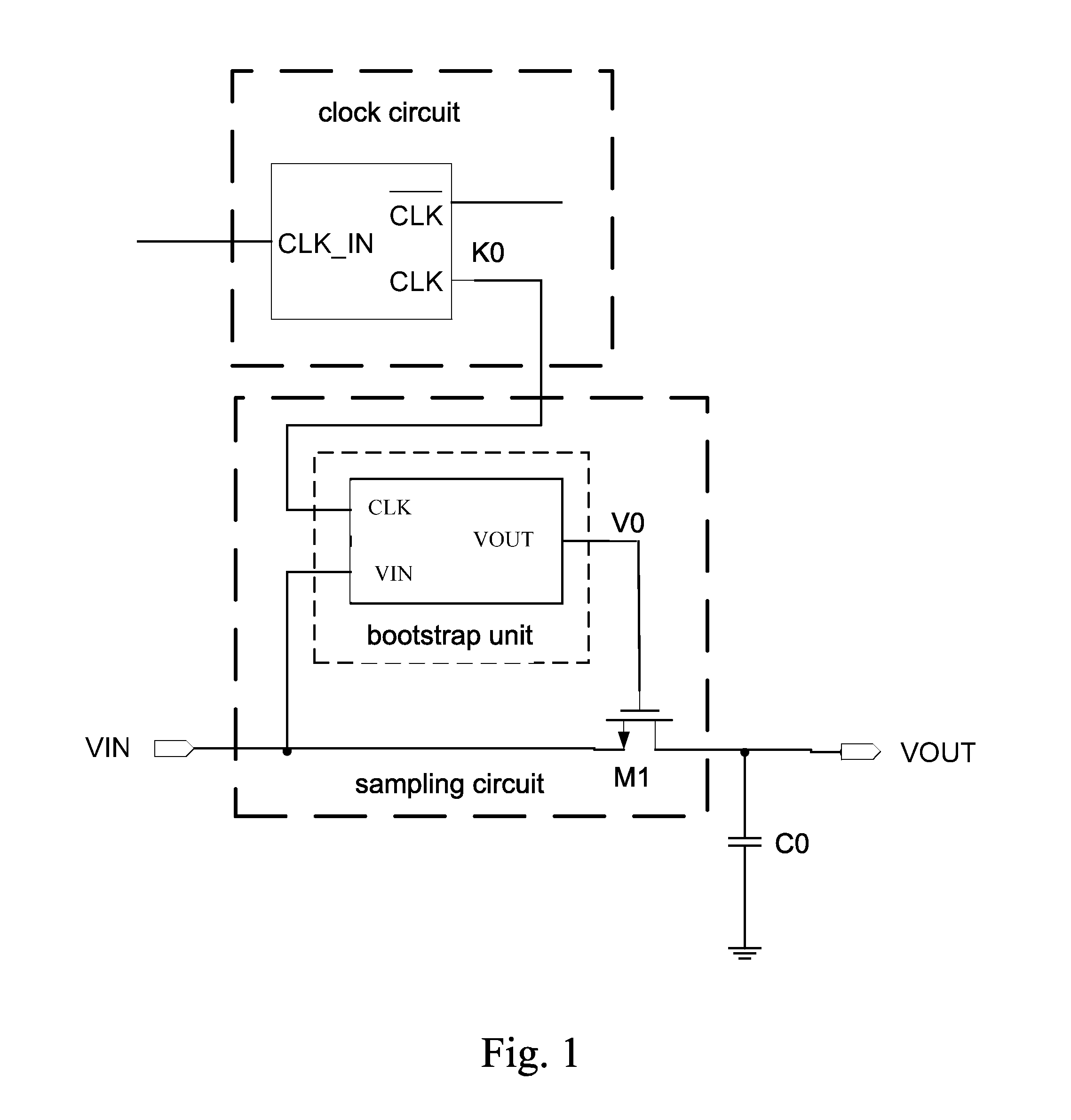

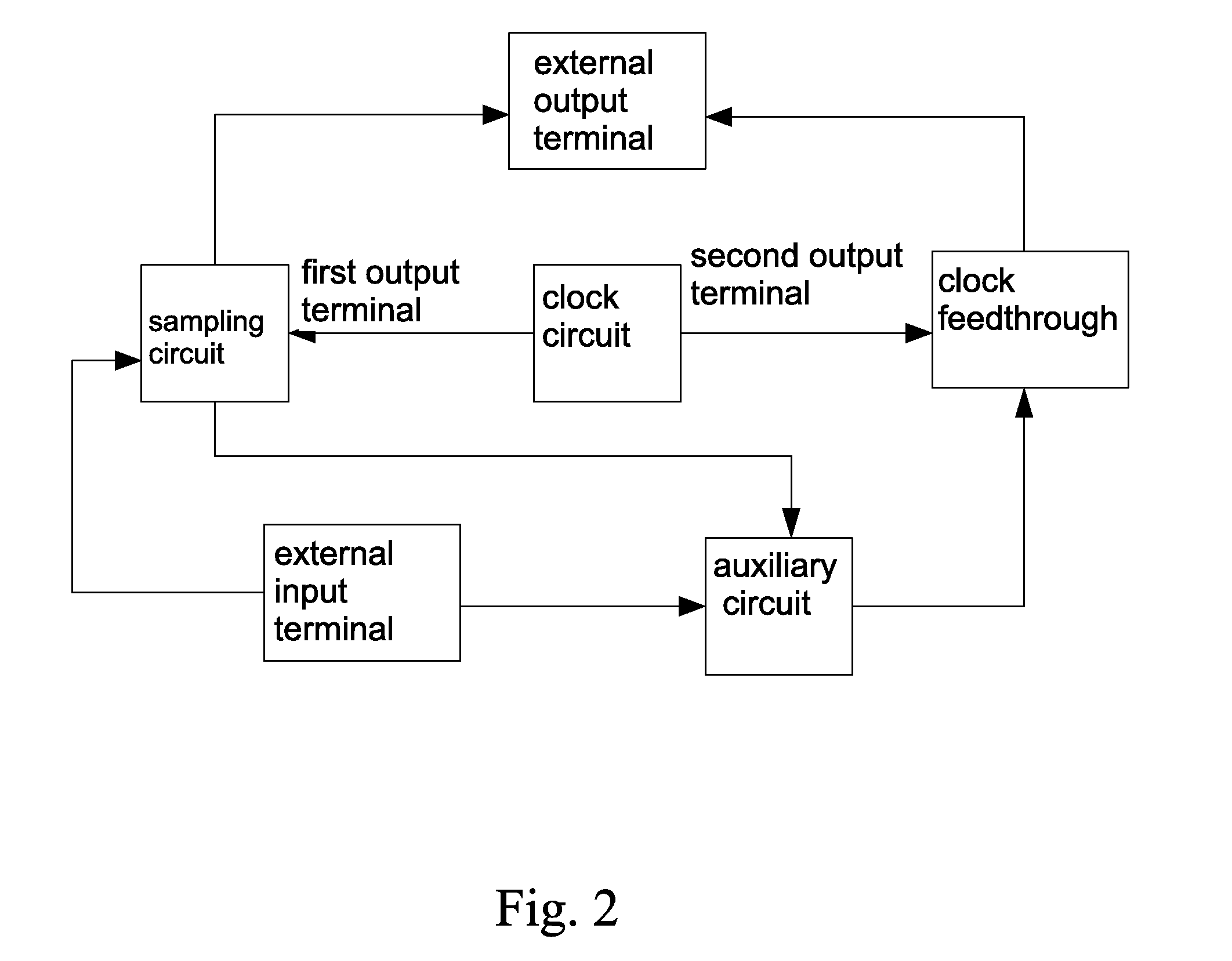

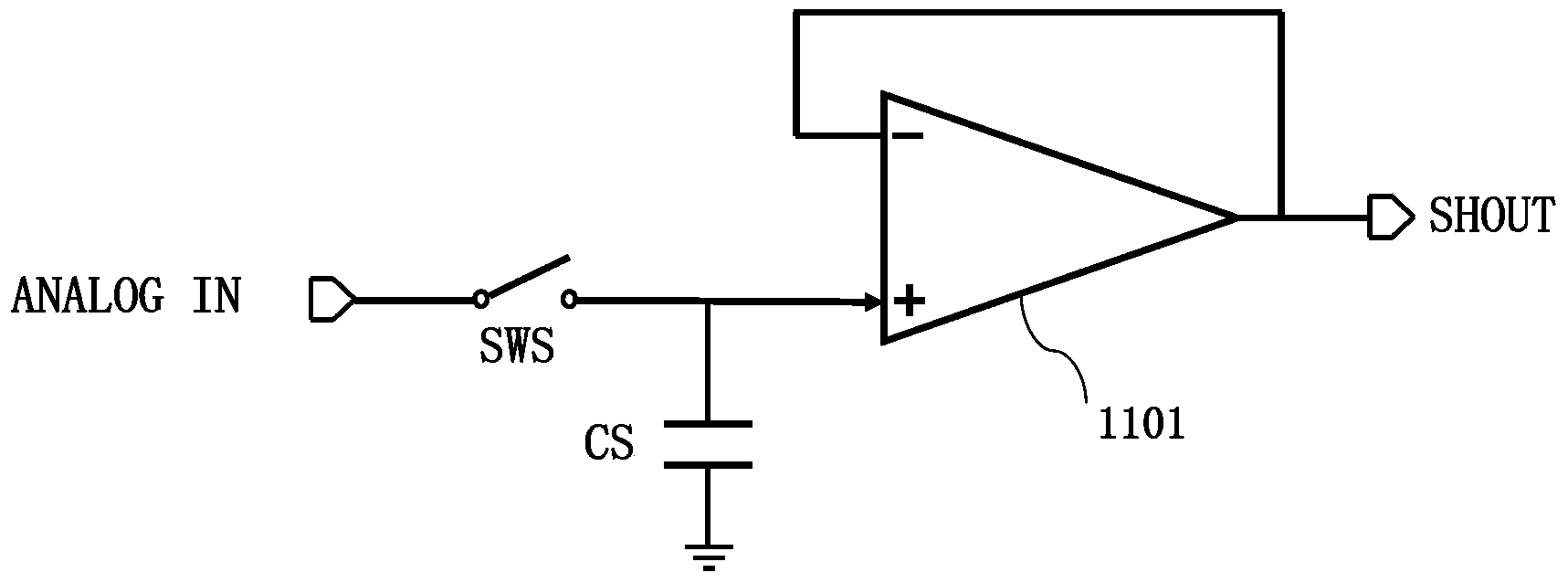

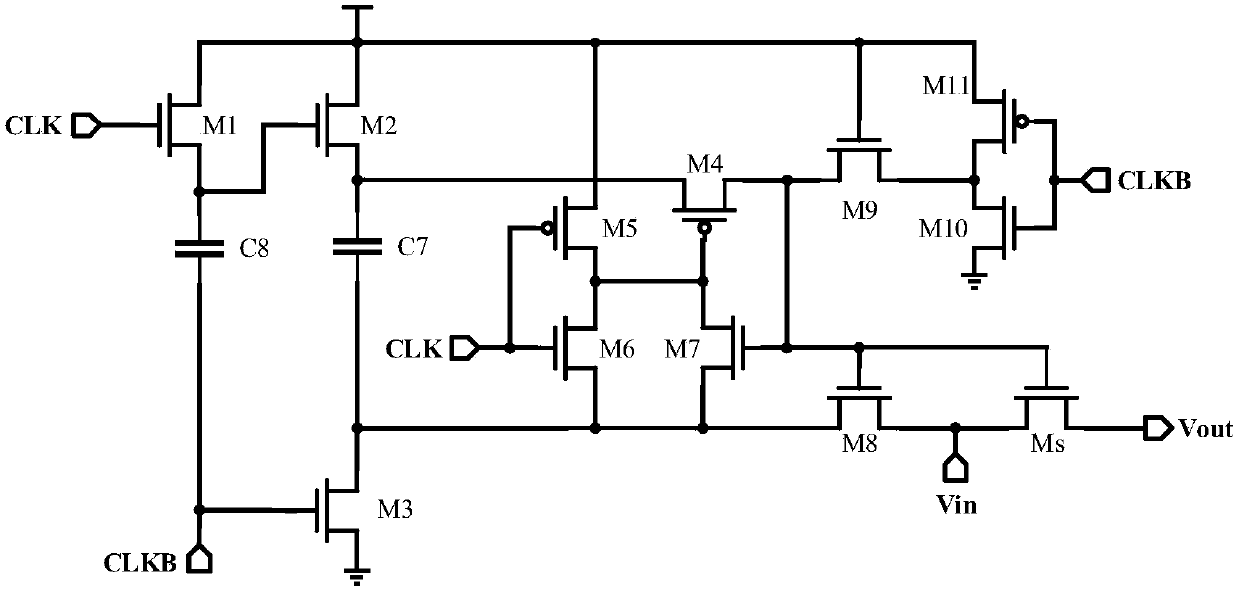

Sampling circuit for ADC

InactiveUS20140176354A1Reduce the impactImprove linearityElectric signal transmission systemsElectric analogue storesEngineeringLinearity

A sampling circuit for ADC includes an external input terminal, a sampling circuit and an auxiliary circuit which are connected with the external input terminal, a clock circuit and an external output terminal which are connected with the sampling circuit, and a clock feedthrough circuit connected with the auxiliary circuit, wherein the clock feedthrough circuit is respectively connected with the clock circuit and the external output terminal. The sampling circuit for ADC of the present invention decreases the impact of clock feedthrough on signal sampling, improves linearity of sampling FET, reduces harmonic distortion of the sampling circuit and improves sampling speed thereof, and improves sampling accuracy of the sampling circuit for ADC.

Owner:IPGOAL MICROELECTRONICS (SICHUAN) CO LTD

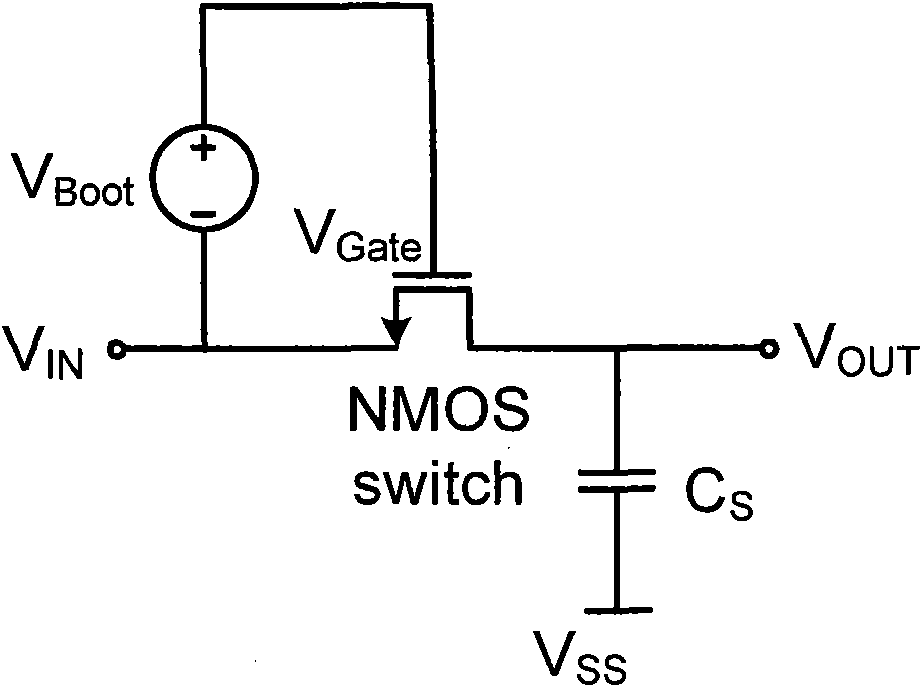

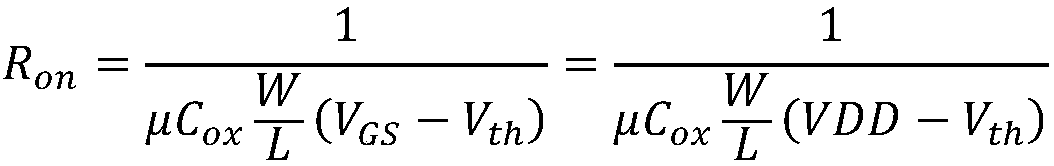

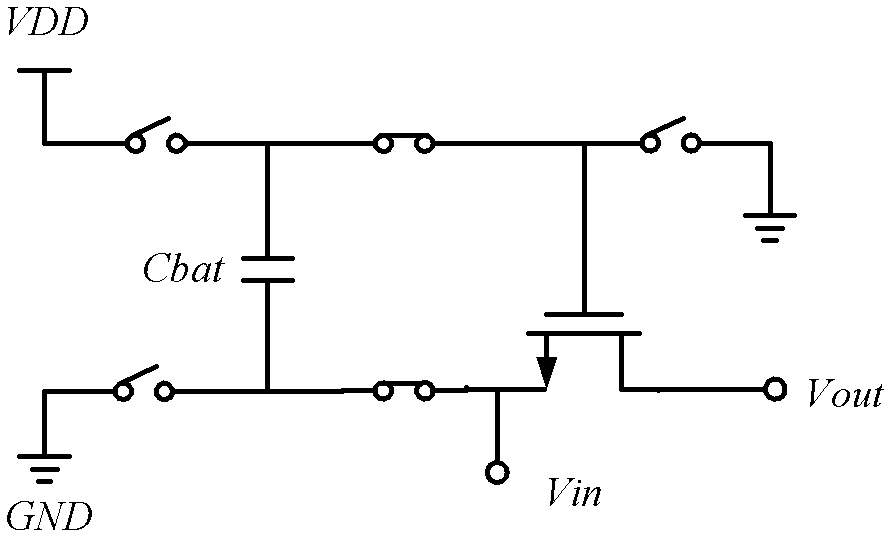

Dual bootstrap and voltage compensation technology-based A/D converter sampling switch

ActiveCN101577545AReduce power consumptionSolve nonlinear problemsElectric analogue storesElectronic switchingLow voltageProcess error

The invention discloses a dual bootstrap and voltage compensation technology-based A / D converter sampling switch, which comprises a primary switch unit used for a to-be-sampled signal channel to sample to-be-sampled signals, a underlayer voltage bootstrap unit for realizing the underlayer voltage bootstrap of a switching tube PMOS Switch in the primary switch unit, a grid voltage bootstrap unit for realizing the grid voltage bootstrap of the switching tube PMOS Switch in the primary switch unit, a storage unit for parallelly sampling input signals VIN and realizing the temporary storage of a VIN voltage, and a voltage compensation unit for compensating the sampling output voltage of an output end VOUT. The invention provides a sampling switch which is capable of working at low voltage and low power consumption and is insensitive to process errors. Meanwhile, the adopted voltage self-compensation method effectively solves a nonlinear problem caused by clock feedthrough occurring after the grid voltage bootstrap of the switching tube.

Owner:INST OF ELECTRONICS CHINESE ACAD OF SCI

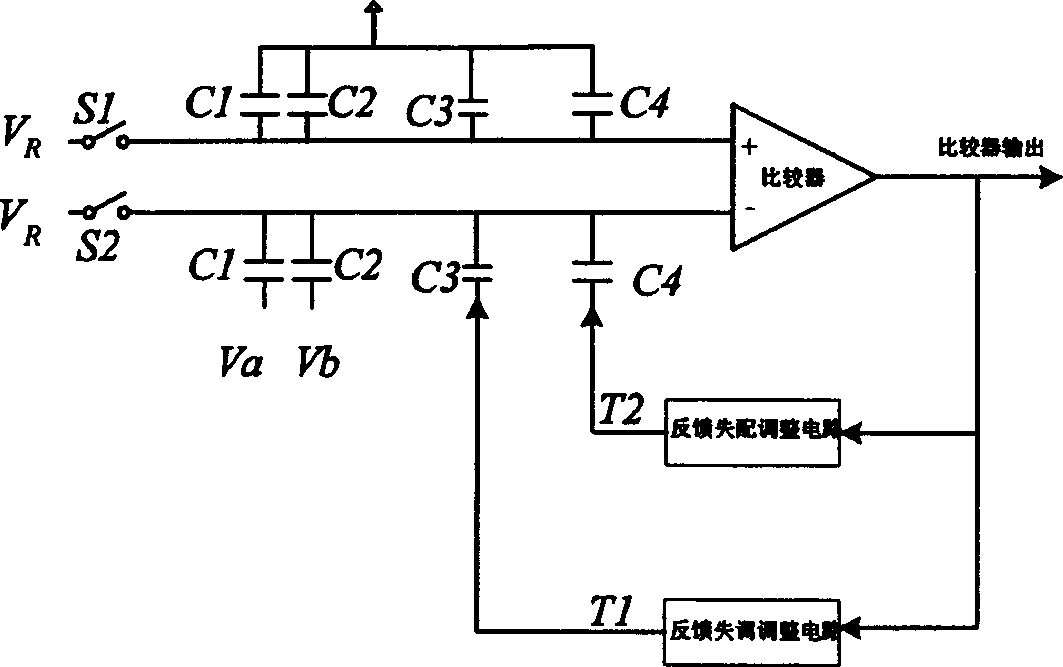

Capacity mismatch calibrating device

InactiveCN1599254AHigh speedEliminate the Effects of MismatchElectric signal transmission systemsAnalogue/digital conversion calibration/testingCapacitanceCharge injection

The invention discloses a capacitor mismatch adjusting device used in the chip and is composed of the capacitor to be adjusted, comparator maladjusted adjusting capacitor, adjusting capacitor and comparator. The capacitor mismatch compensating circuit of the invention adopts the charge on the self-adapting adjusting mismatch adjusting capacitor, increases the speed of the circuit, and eliminates the affect to the capacitor mismatch from the channel charge afflux and the clock feedthrough caused by the on-off of the diode. It is also benefit to increase the precision of the capacitor match.

Owner:SOUTHEAST UNIV

Current switching circuit for high-speed current rudder digital-to-analog converter

InactiveCN102158211AReduced voltage swingFast switching speedElectronic switchingDriver circuitControl signal

The invention discloses a current switching circuit for a high-speed current rudder digital-to-analog converter, comprising a switch main body circuit, a constant-current circuit which provides a constant flow source for the switch main body switch, a switch drive circuit which provides difference switching signals to the switch main body circuit and a four-phase control signal generating circuit which provides difference control signals for the switch drive circuit. A pre-breakover pull-down MOS (Metal Oxide Semiconductor) tube is adopted in the switch drive circuit , and a clock feedthrough compensation structure is applied to the switch main body circuit, thus overshooting of the difference switching signals is greatly weakened, falling edges of the difference switching signals at the initial stage of hopping become gentle, symmetry of rising and falling edges of the difference switching signals in case of low swing amplitude is improved and clock feedthrough errors resulting from the difference switching signals are effectively reduced. The current switching circuit is especially applicable to the high-speed and high-precision digital-to-analog converter.

Owner:ZHEJIANG UNIV

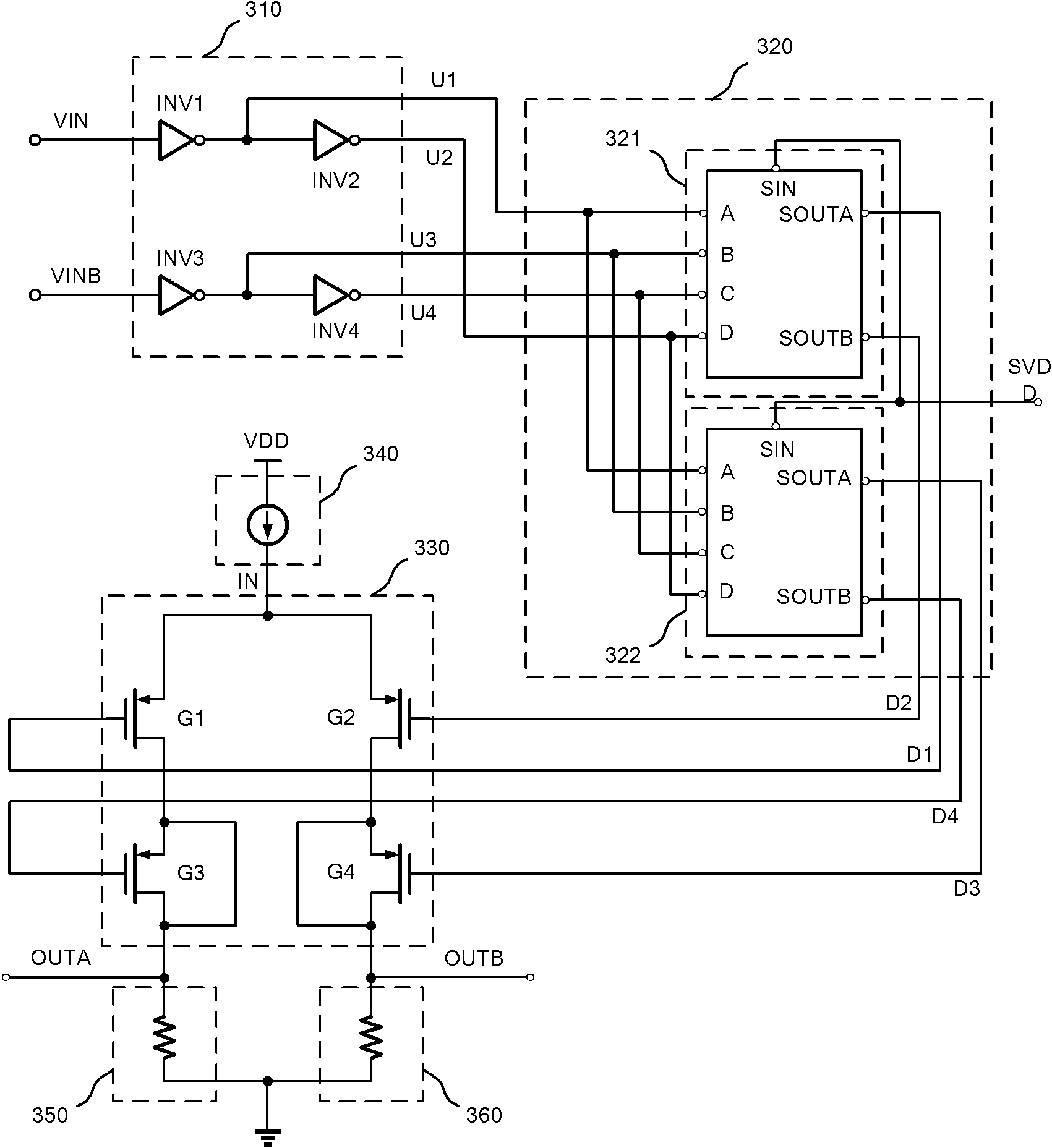

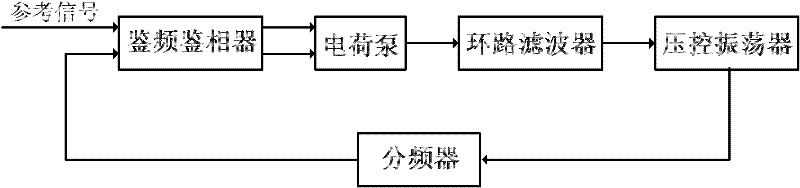

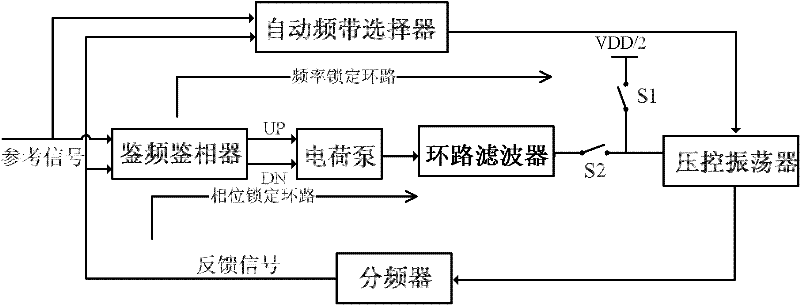

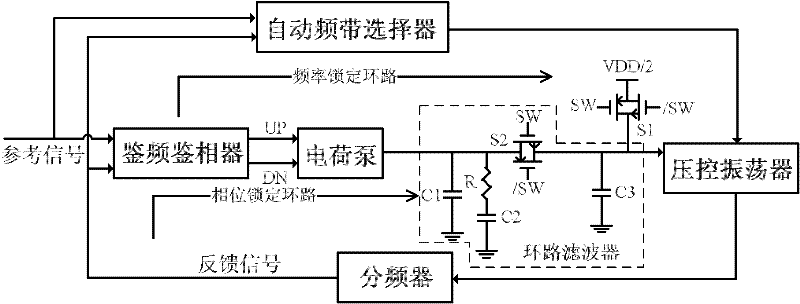

A phase-locked loop circuit for suppressing vco voltage ripple

InactiveCN102291129AReduce control voltage rippleReduce injectionPulse automatic controlPhase detectorLoop filter

The invention discloses a phase-locked loop circuit used for inhibiting a VCO (voltage-controlled oscillator) voltage ripple, which comprises a frequency-phase detector, a charge pump, an automatic frequency band selector, a loop filter, a voltage-controlled oscillator, a frequency divider and a first transmission gate. In the invention, as the transmission gate is used as a mode-converting switch, the VCO control voltage ripple caused by traditional MOS (metal-oxide semiconductor) transistor in different working models converting in the phase-locked loop, the electric charge injection and the clock feed-through are reduced, thus, the purpose of inhibiting the VCO voltage ripple is achieved. Meanwhile, the transmission gate is embedded in the third order loop filter, thus, the converting of different working models of the phase-locked loop is realized, and an onstate resistor of the transmission gate is utilized as the resistor of the third order loop filter, the noise is effectively filtered, and the VCO voltage ripple caused by the noise is greatly reduced.

Owner:ZHEJIANG UNIV

Method for nulling charge injection in switched networks

InactiveUS6850098B2Computing operations for integral formationComputing operations for integration/differentiationCharge injectionExchange network

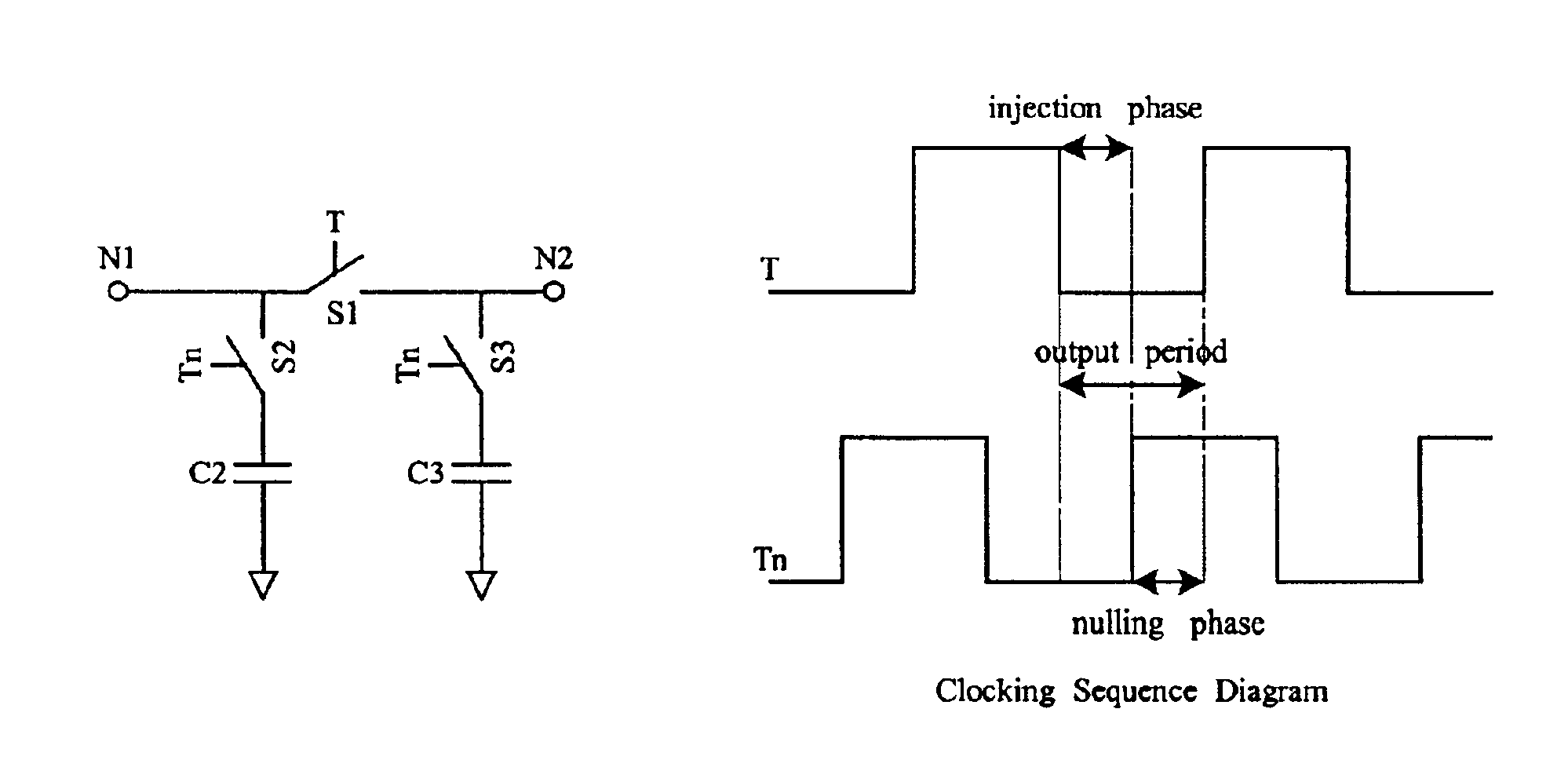

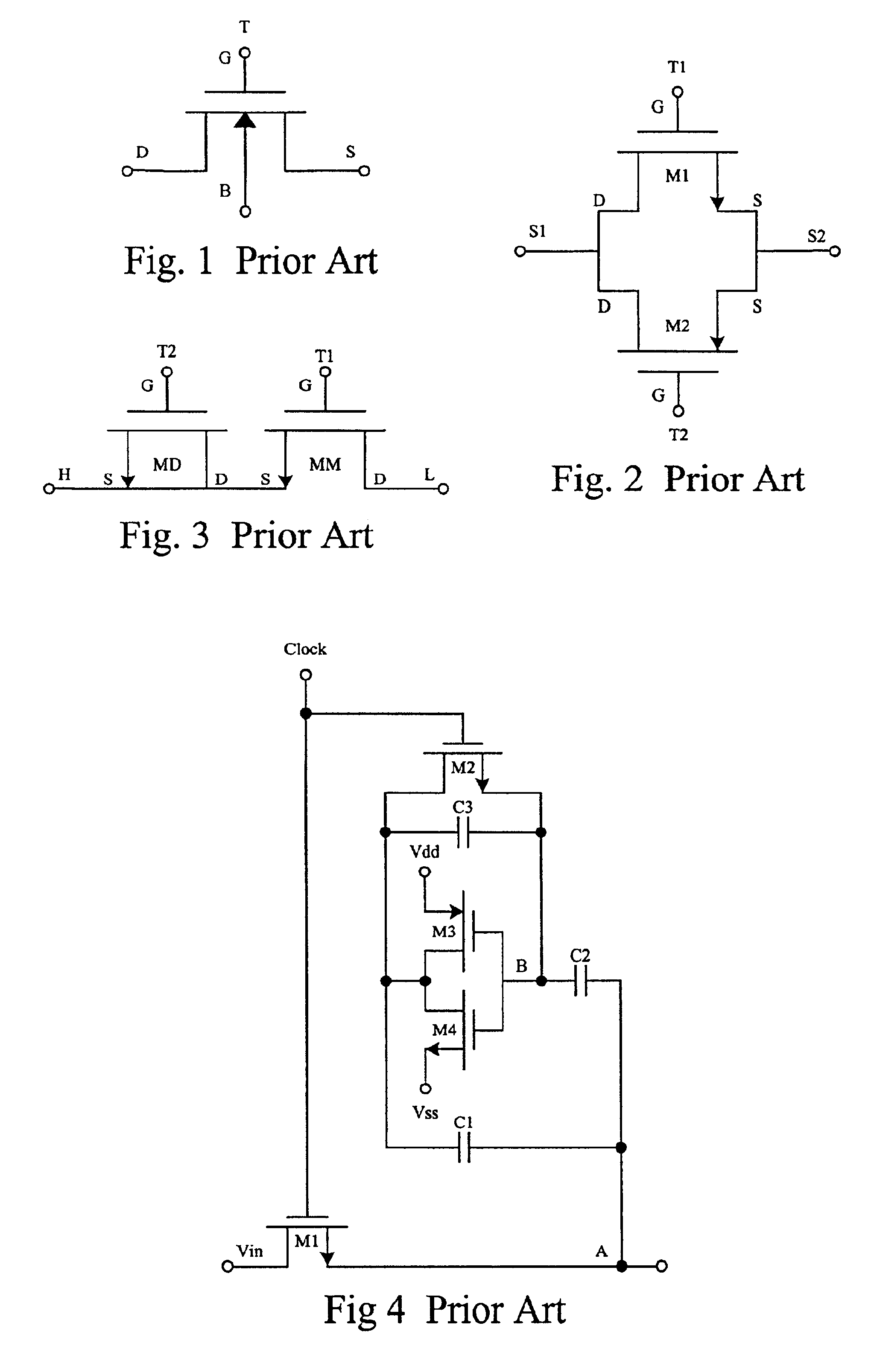

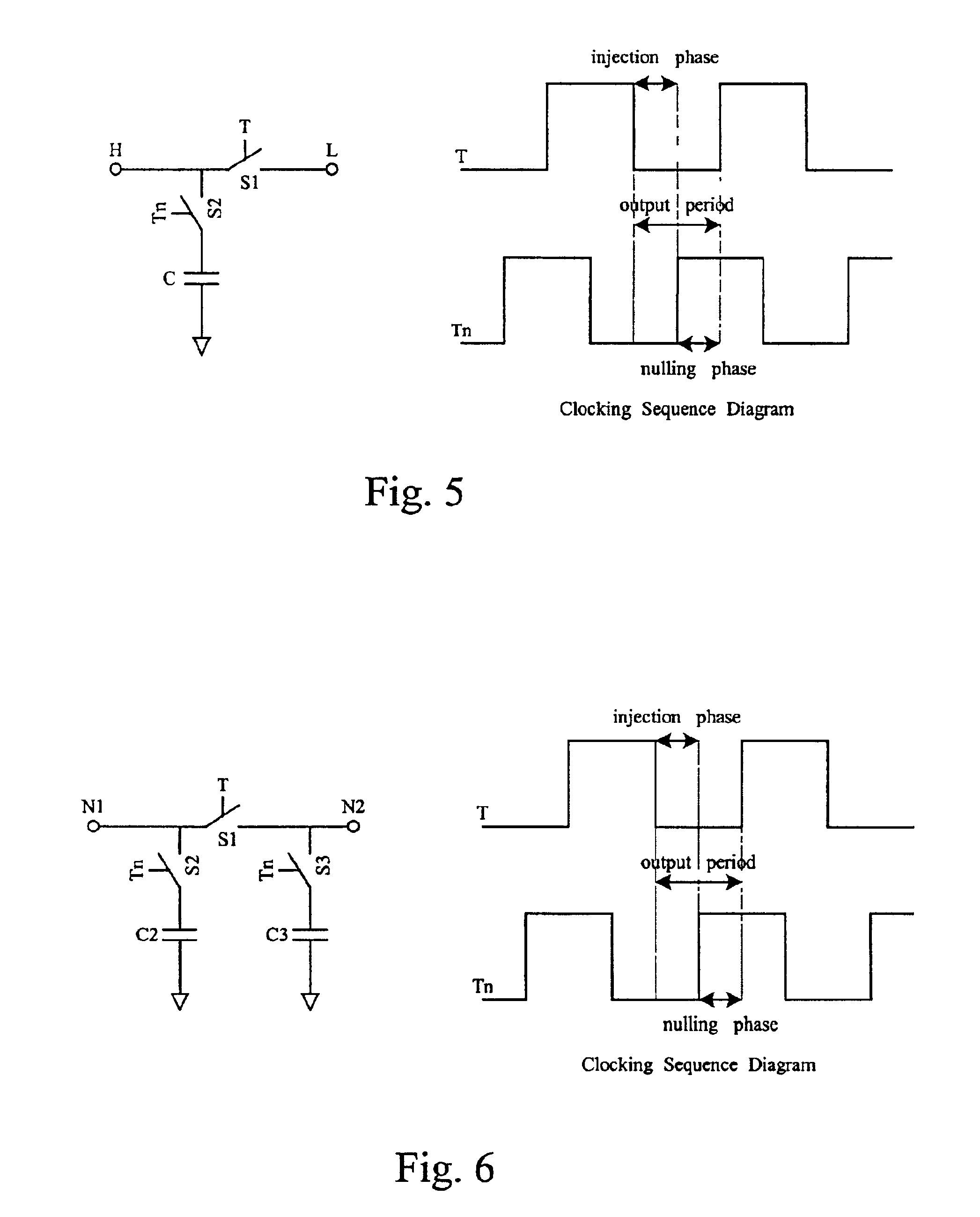

A system and method to overcome or nullify a charge injection and clock feed-through error voltage caused by the turning-off charge of a switched element(s) in switched networks. A circuit for nulling a charge injection and clock feed-through error voltage includes, for example, two switched elements and a capacitor. The circuit can be used to replace any switch element in a switched network. The circuit may also include, for example, three switched elements and two capacitors.

Owner:NANYANG TECH UNIV

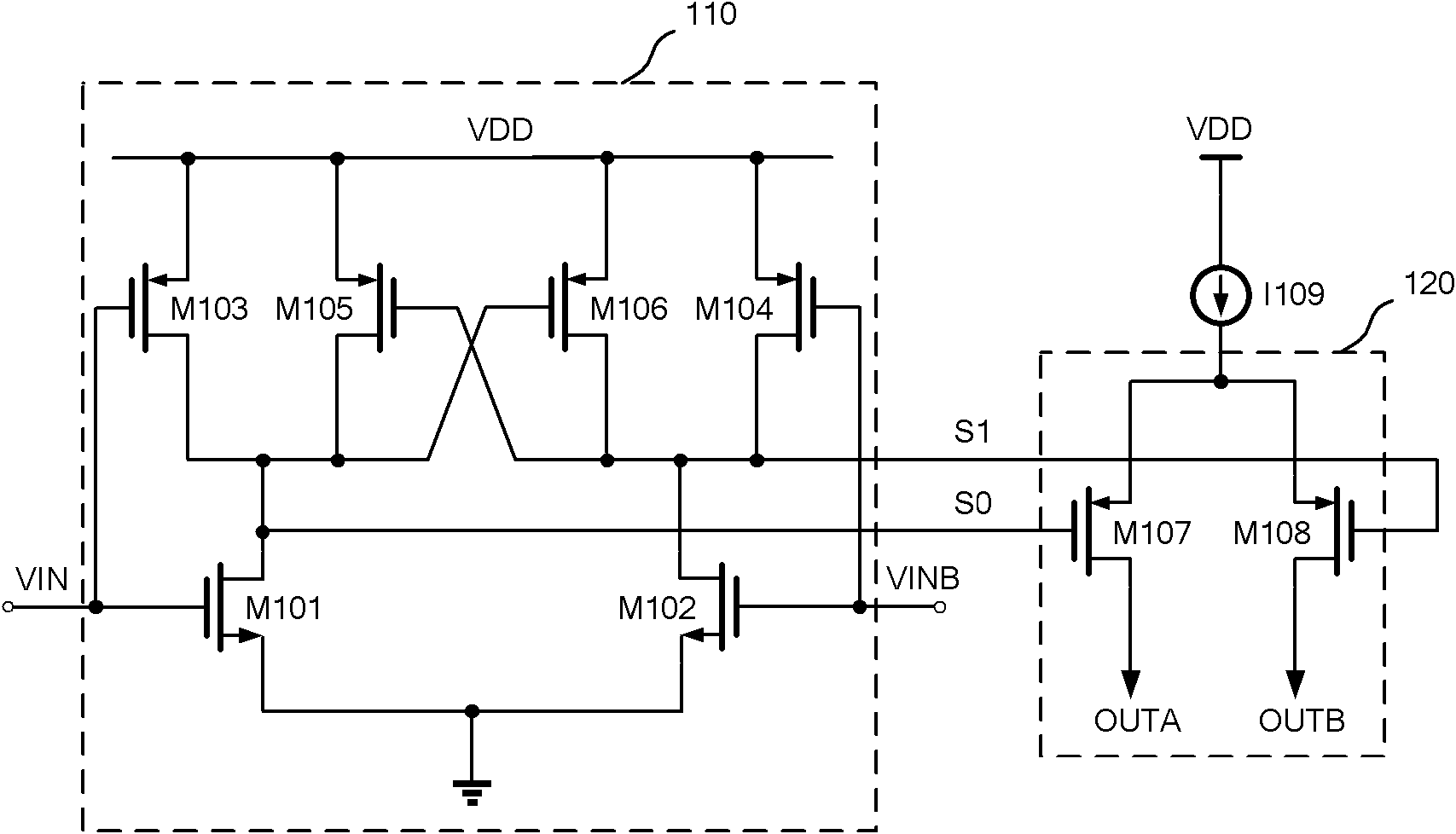

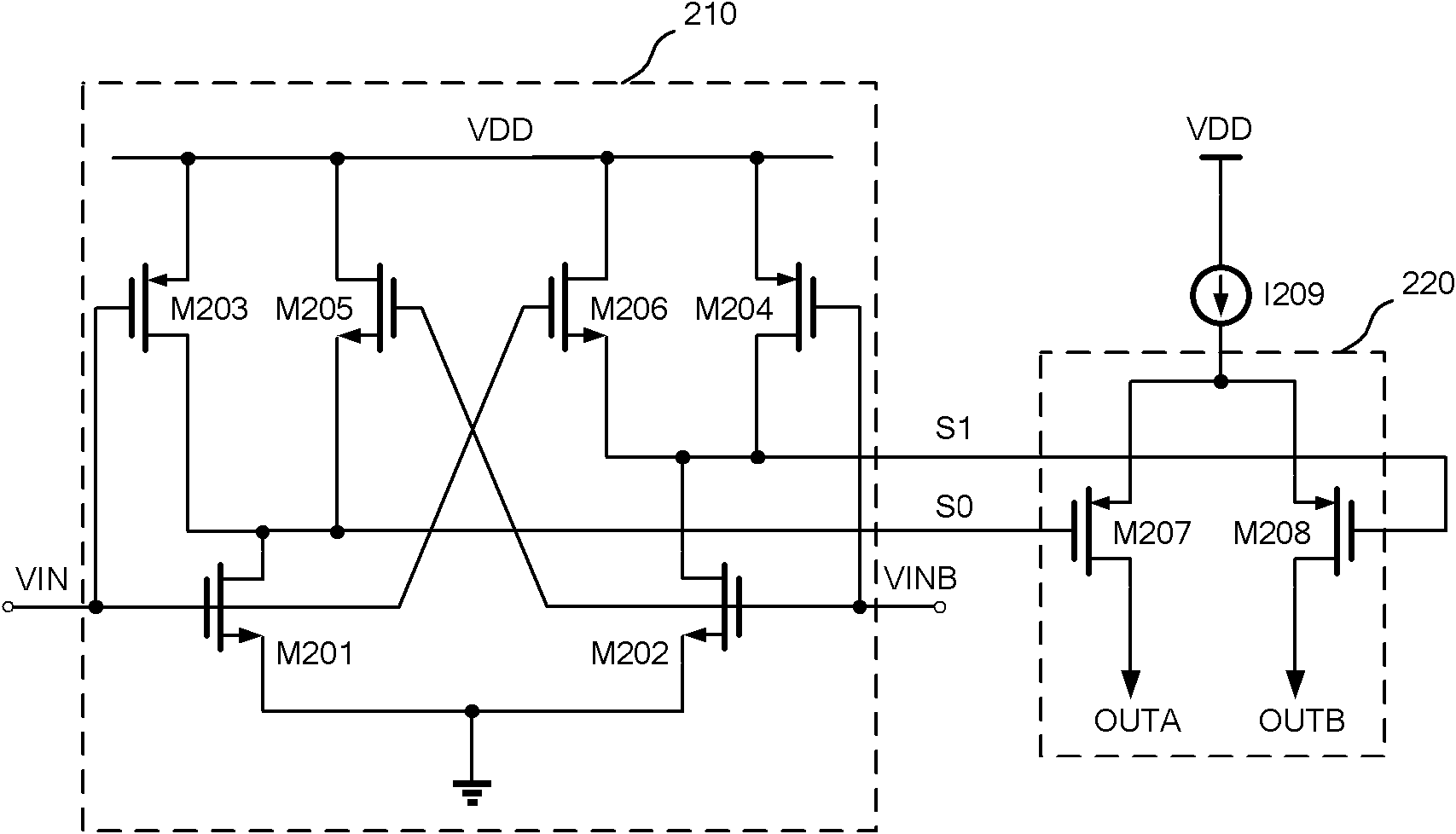

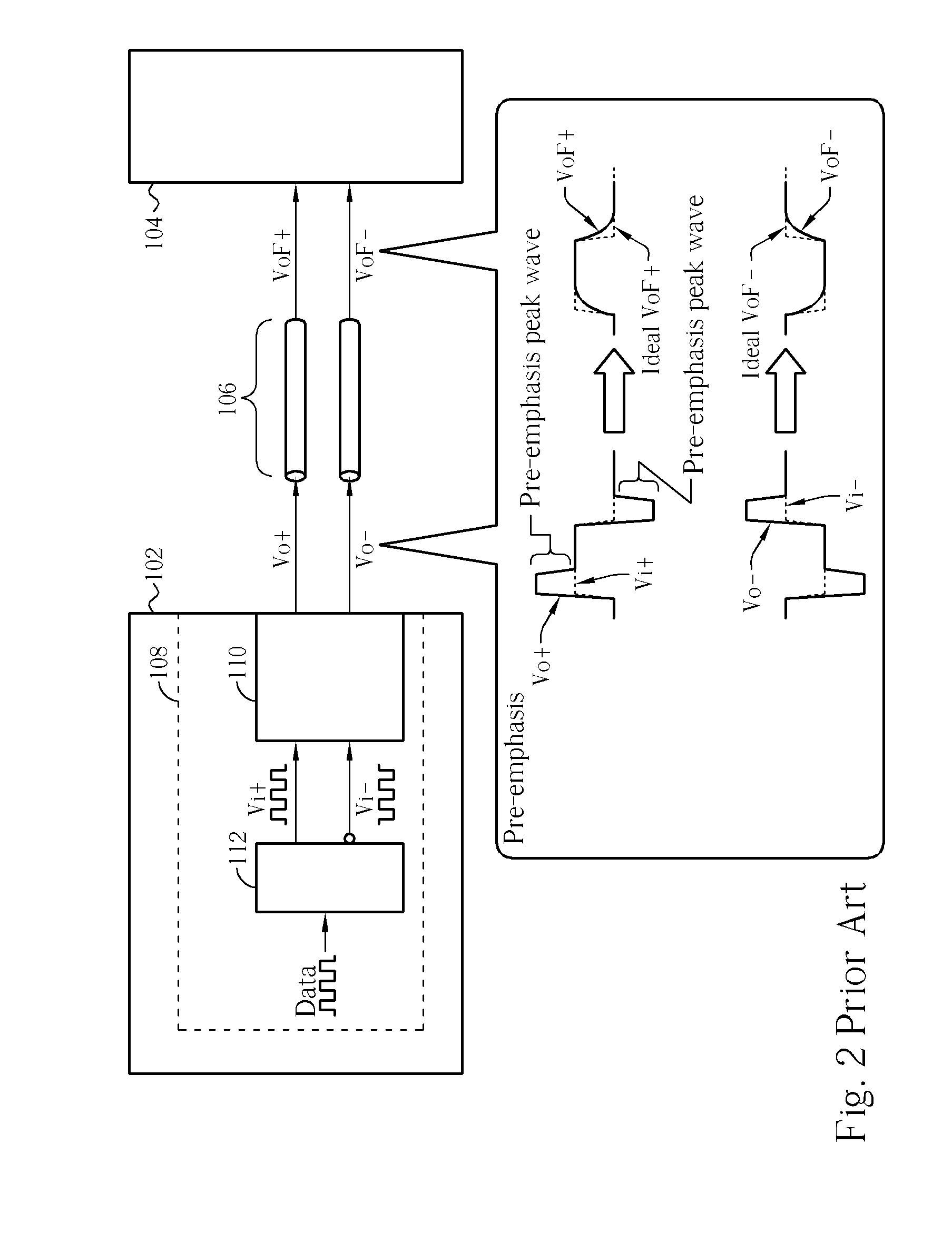

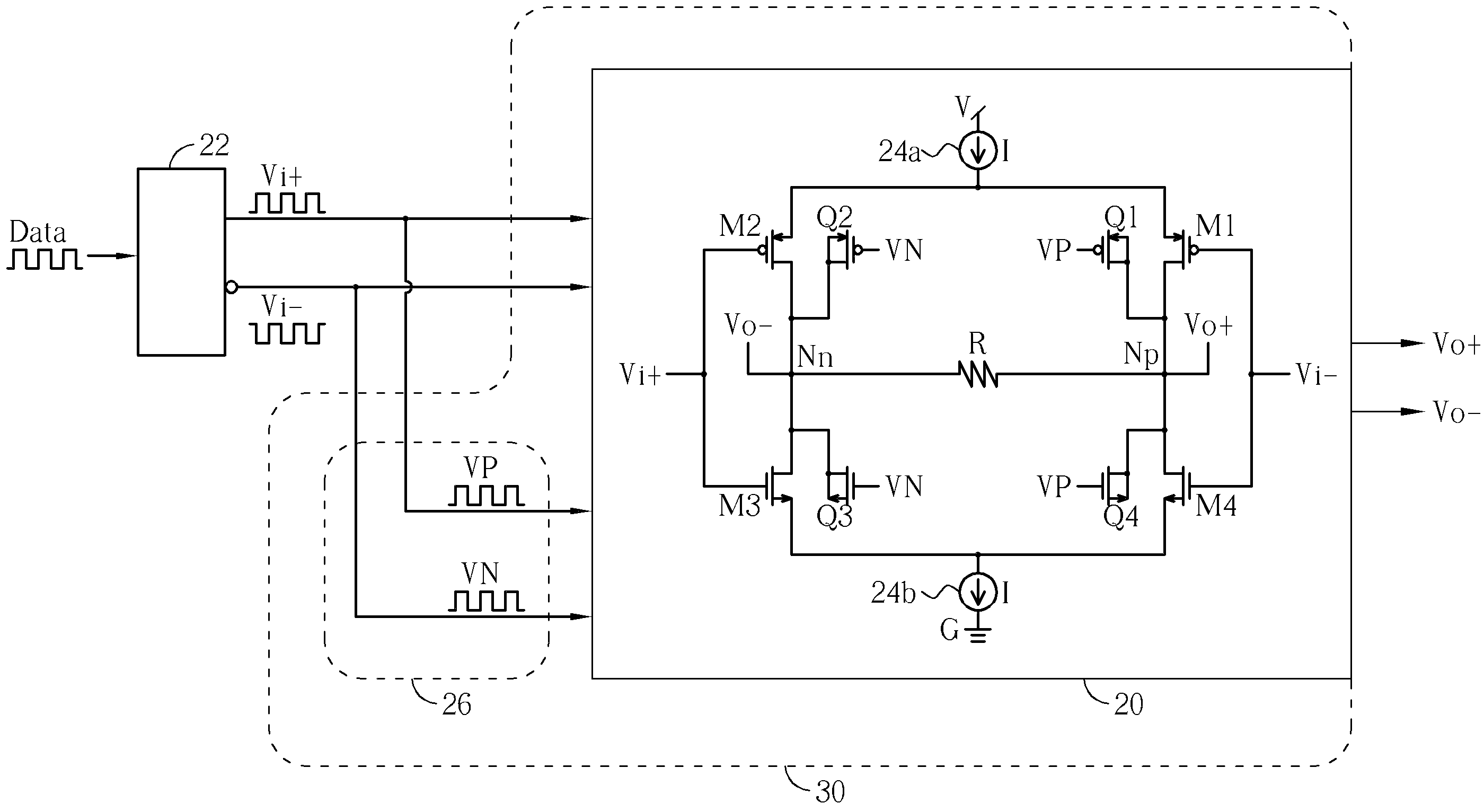

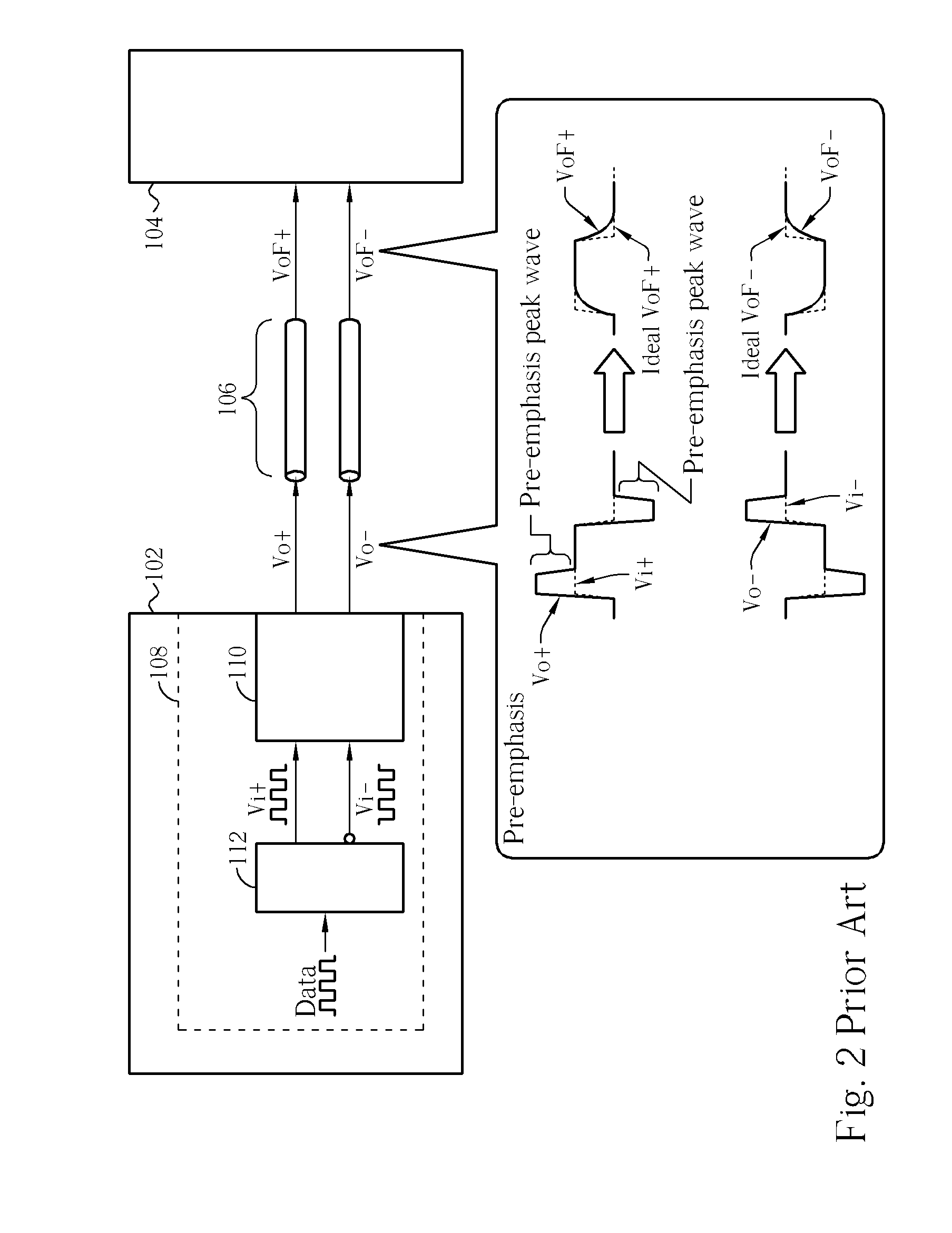

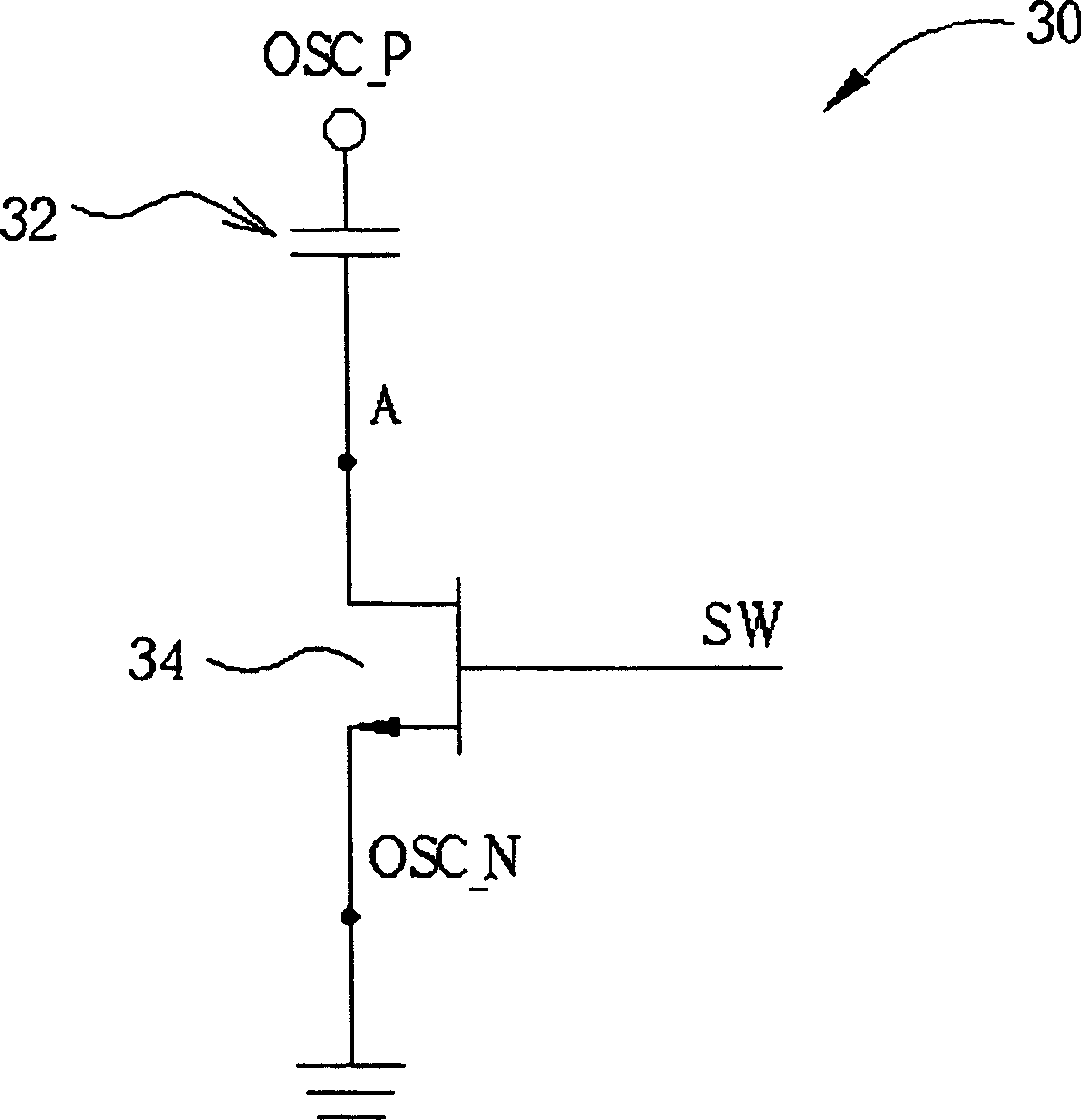

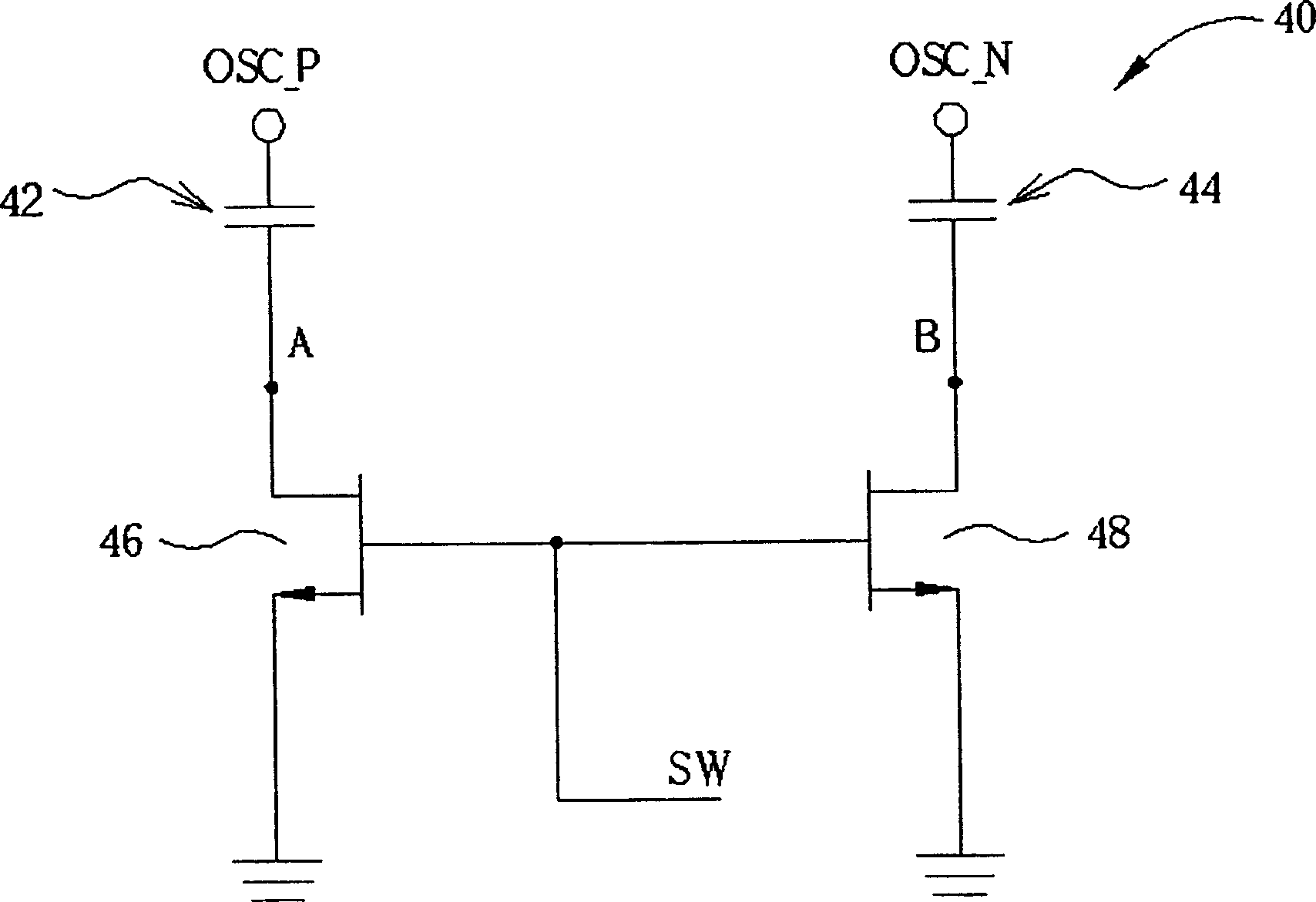

Transmission Circuit and Related Method

ActiveUS20070152749A1Gain controlManipulation where pulse delivered at different timesCharge injectionPeak value

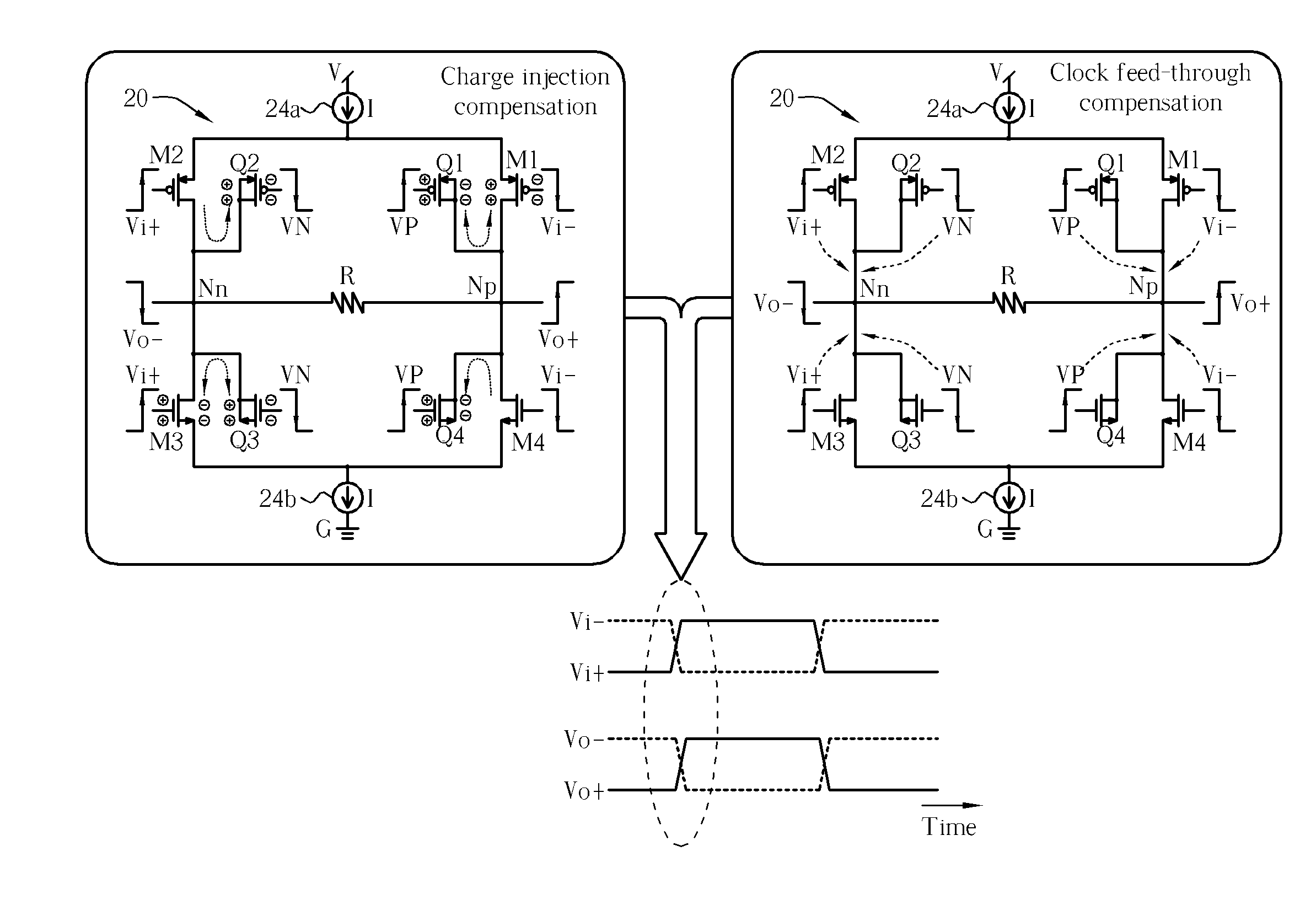

A transmission circuit and related method are disclosed. A transmitter in the transmission circuit has CMOS transistors as driving units for responding an input signal to drive an output signal at an output node, and each driving unit has a corresponding charge unit formed by a capacitor-connected MOS of a same type as that of the corresponding driving unit. Each charge unit is controlled by an auxiliary signal inverse to the input signal. When a level transition occurs in the input signal, the charge unit can compensate charge injection and clock feed-through caused by the driving unit at the output node, and form peaks for pre-emphasis. In this way, a better transmission property can be realized by using a simpler and low-power circuit design.

Owner:VIA TECH INC

Transmission circuit and related method

ActiveUS7825691B2Gain controlManipulation where pulse delivered at different timesCharge injectionPeak value

A transmission circuit and related method are disclosed. A transmitter in the transmission circuit has CMOS transistors as driving units for responding an input signal to drive an output signal at an output node, and each driving unit has a corresponding charge unit formed by a capacitor-connected MOS of a same type as that of the corresponding driving unit. Each charge unit is controlled by an auxiliary signal inverse to the input signal. When a level transition occurs in the input signal, the charge unit can compensate charge injection and clock feed-through caused by the driving unit at the output node, and form peaks for pre-emphasis. In this way, a better transmission property can be realized by using a simpler and low-power circuit design.

Owner:VIA TECH INC

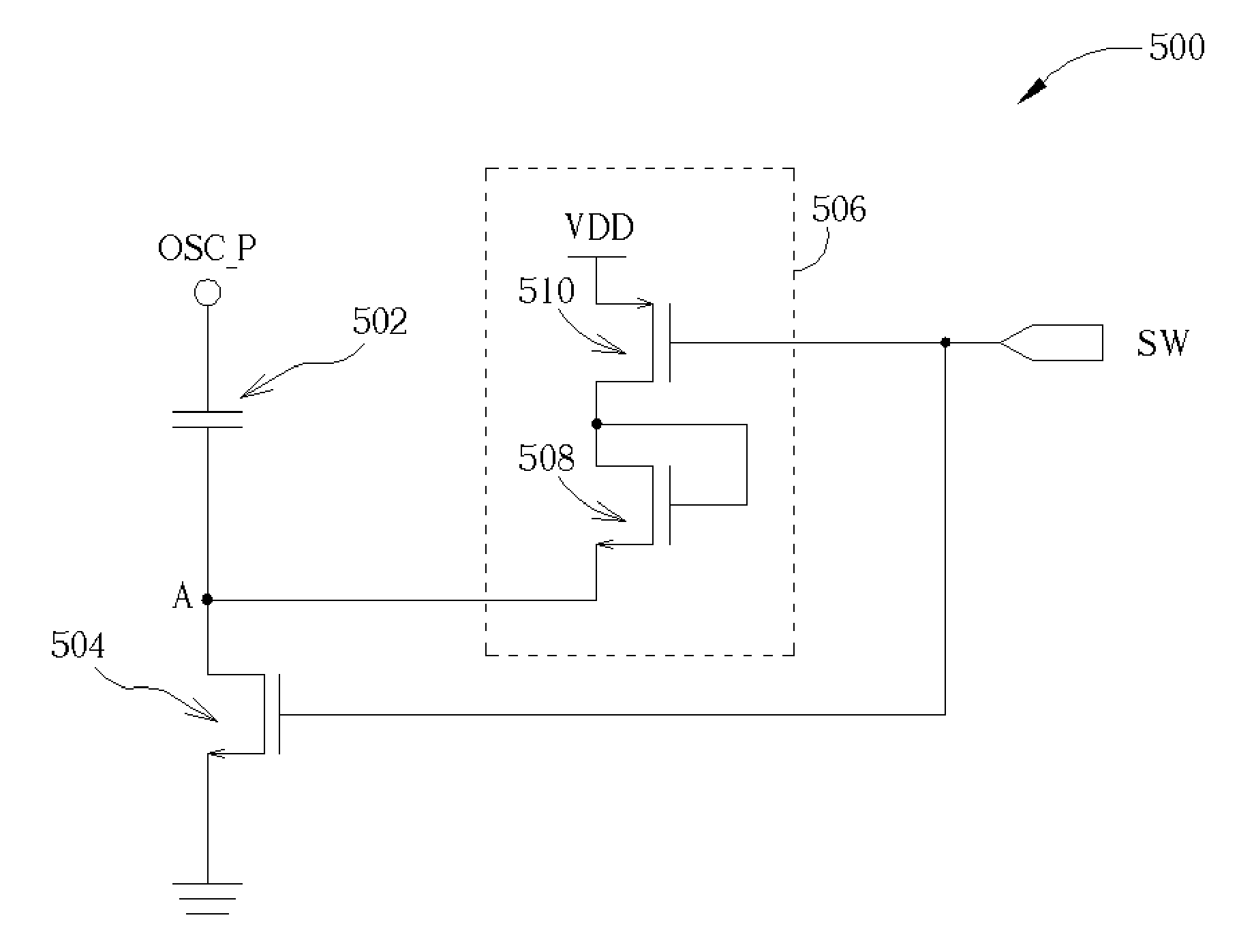

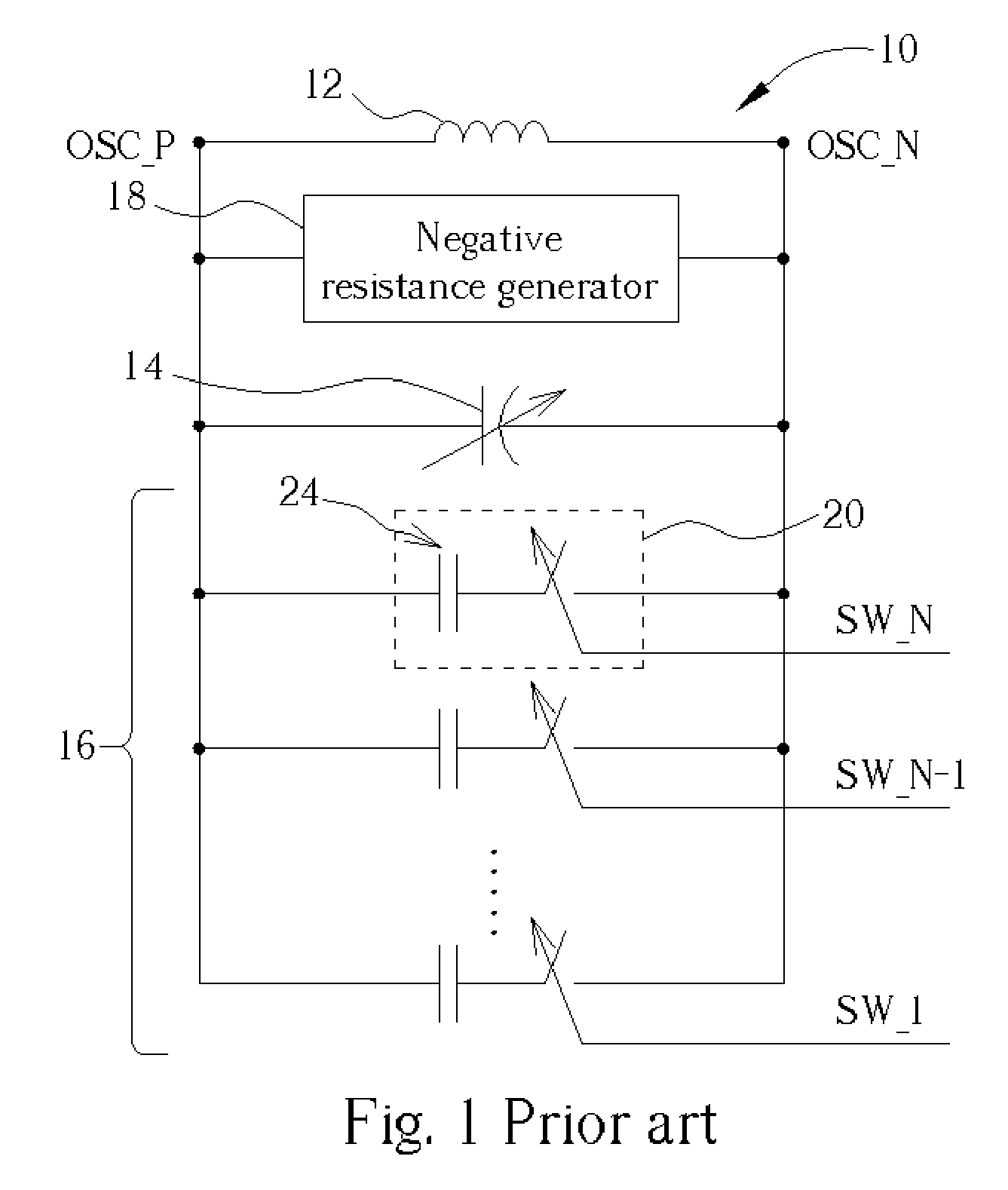

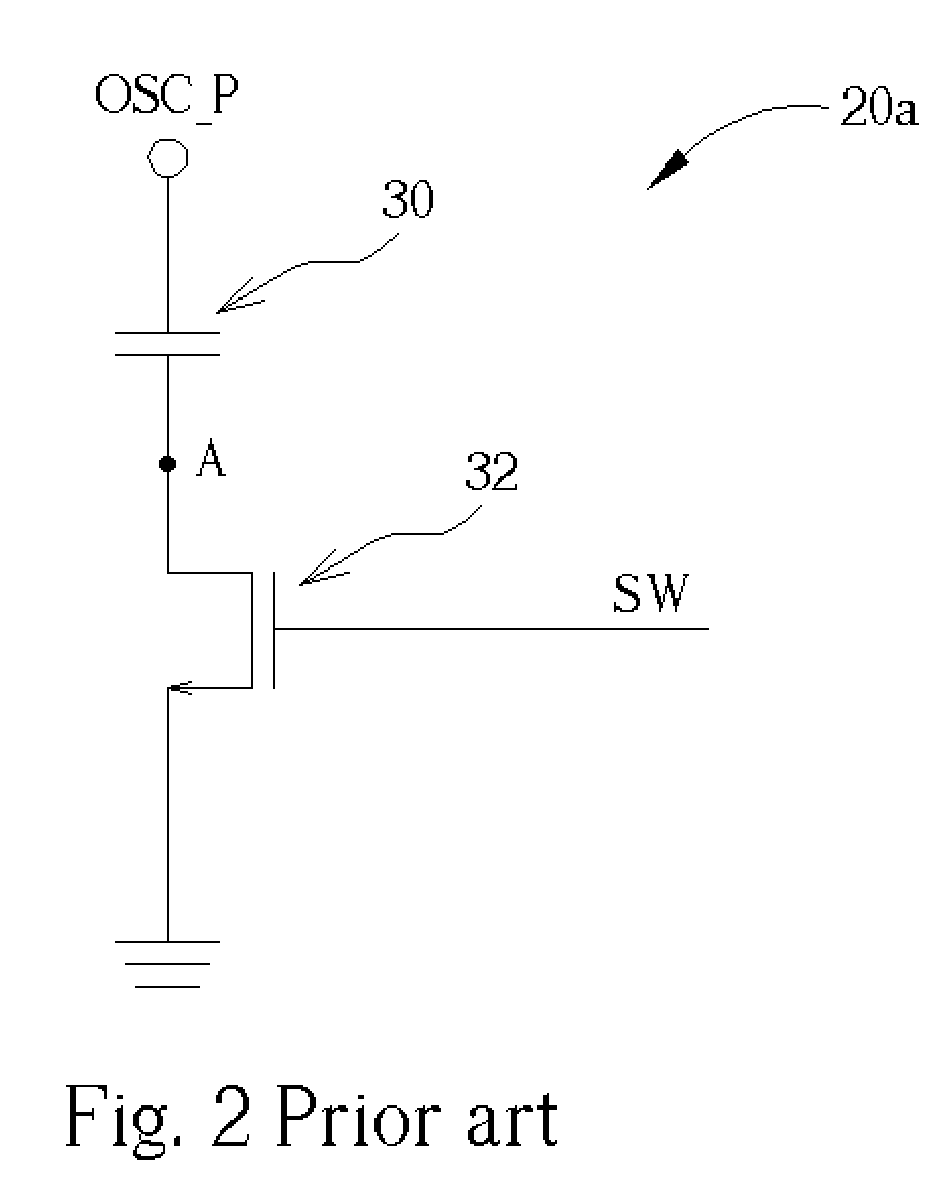

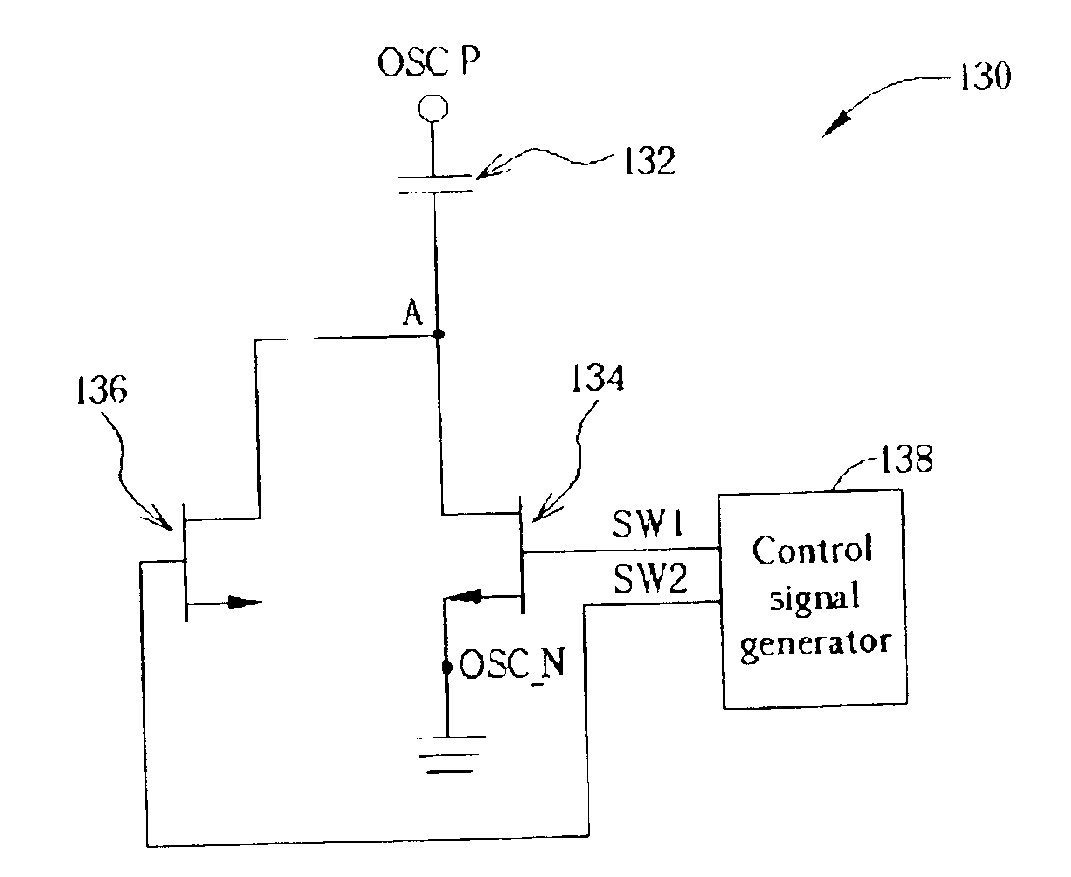

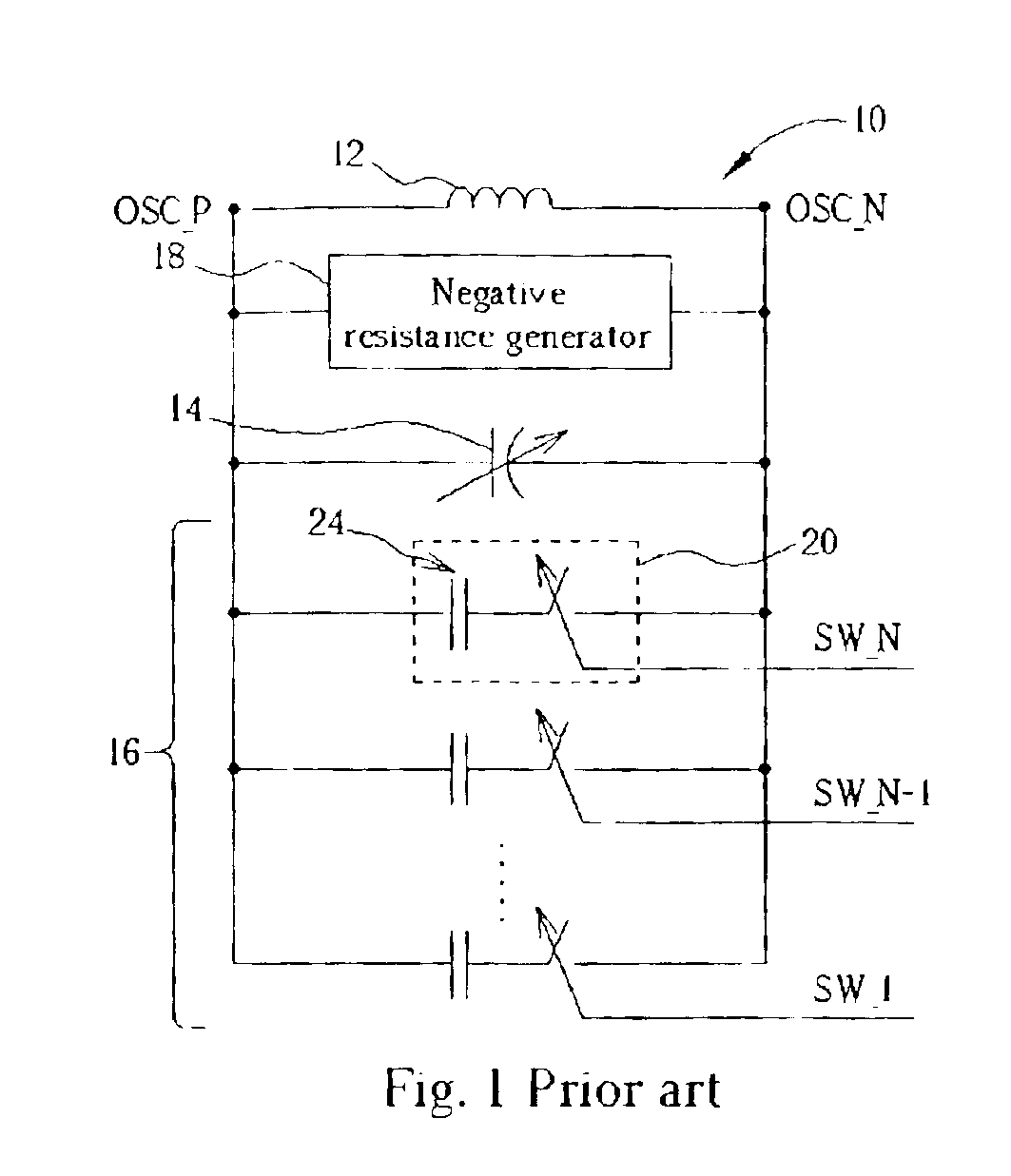

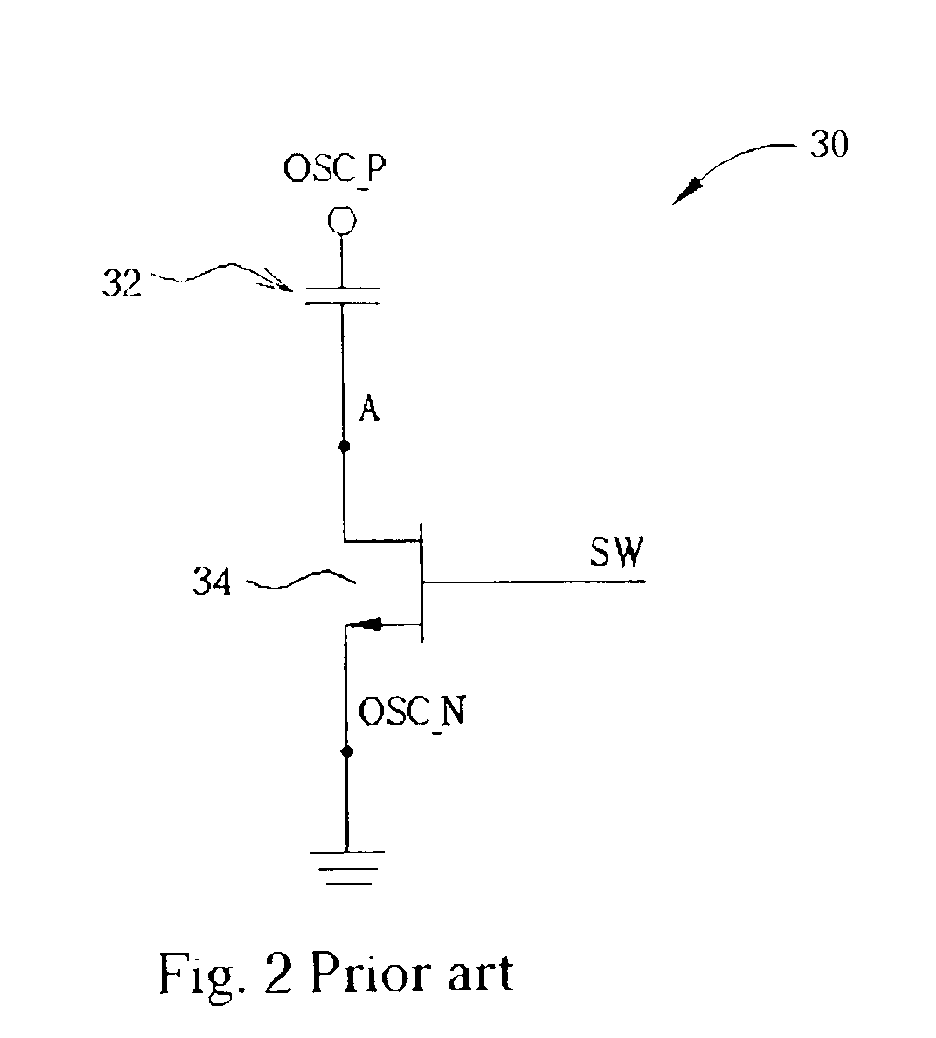

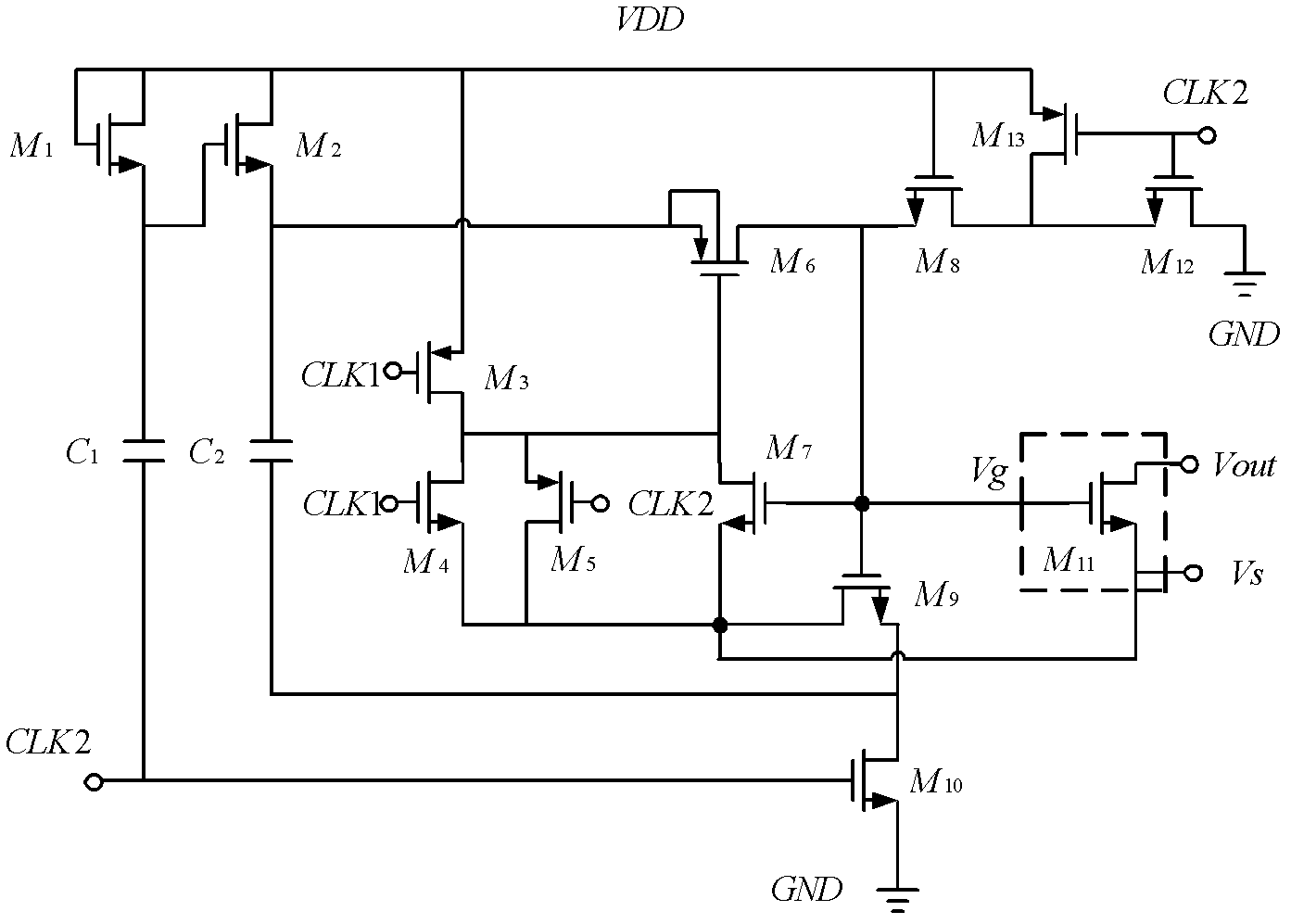

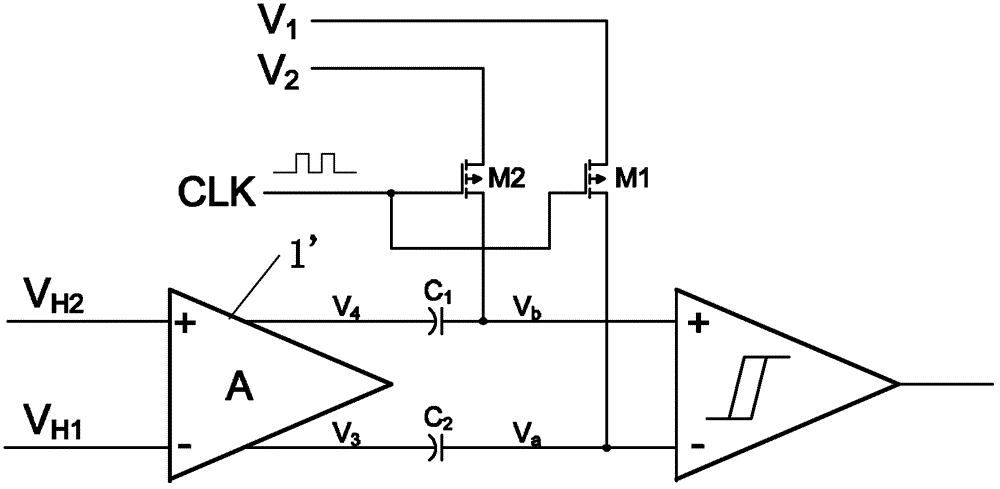

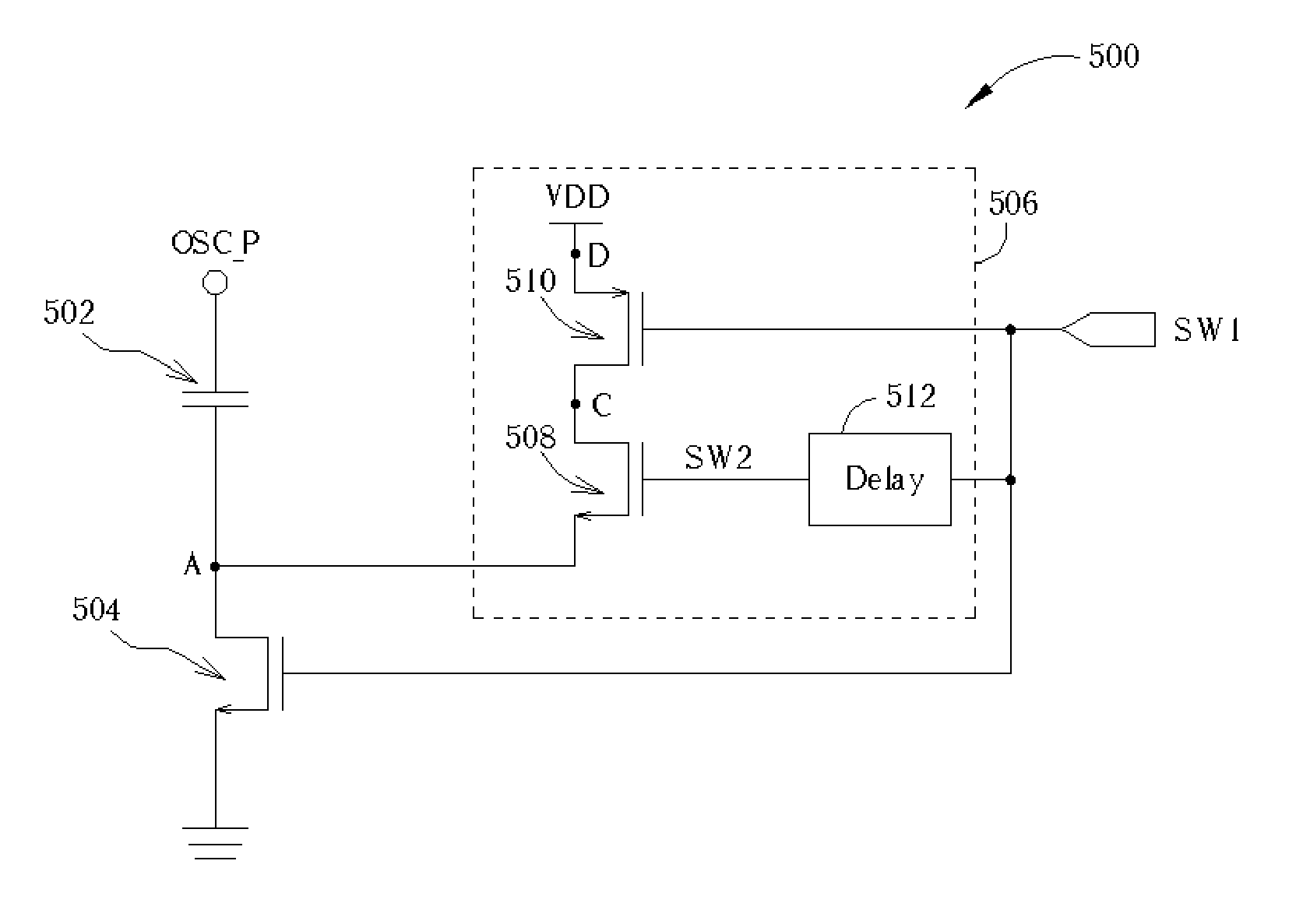

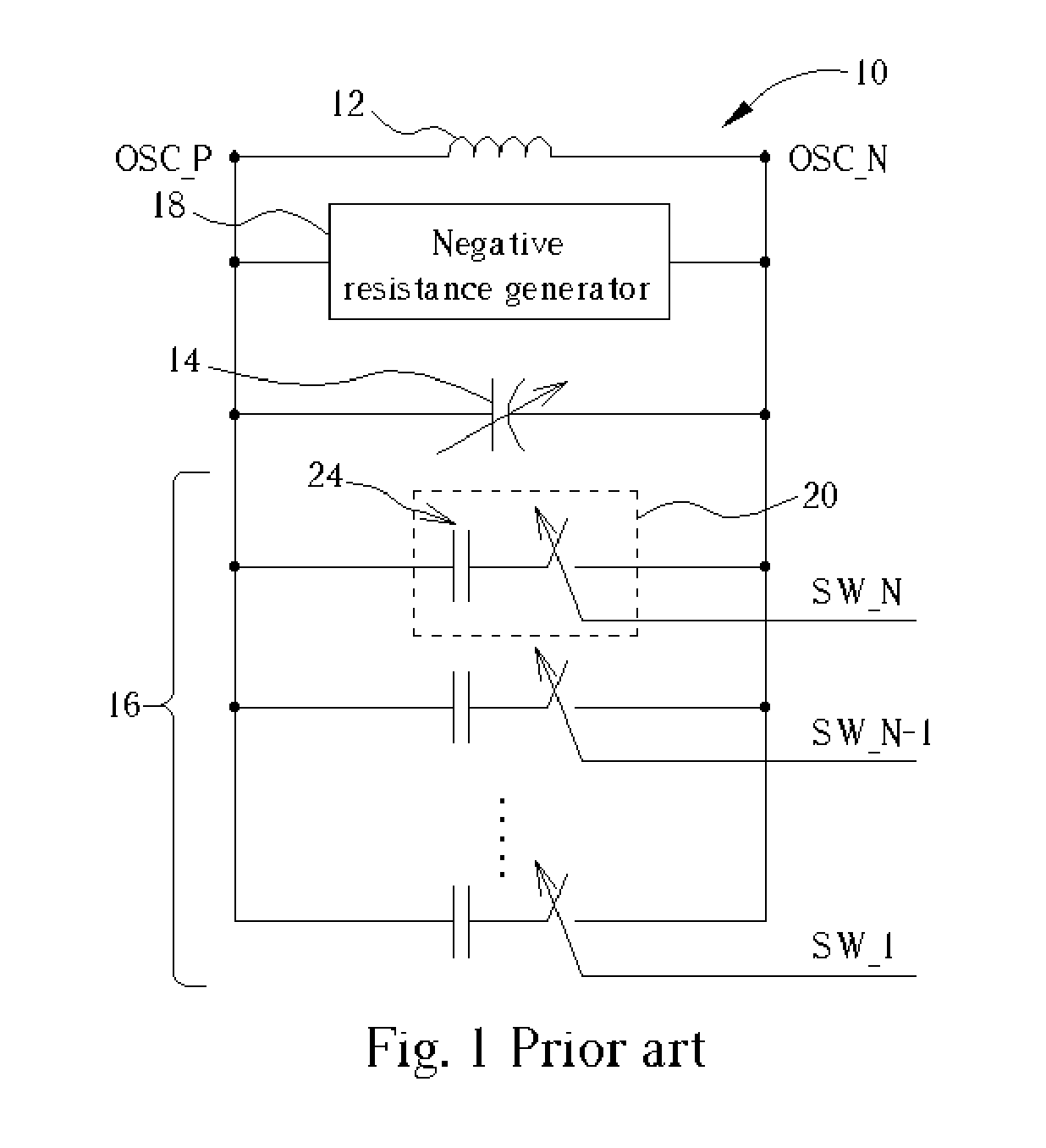

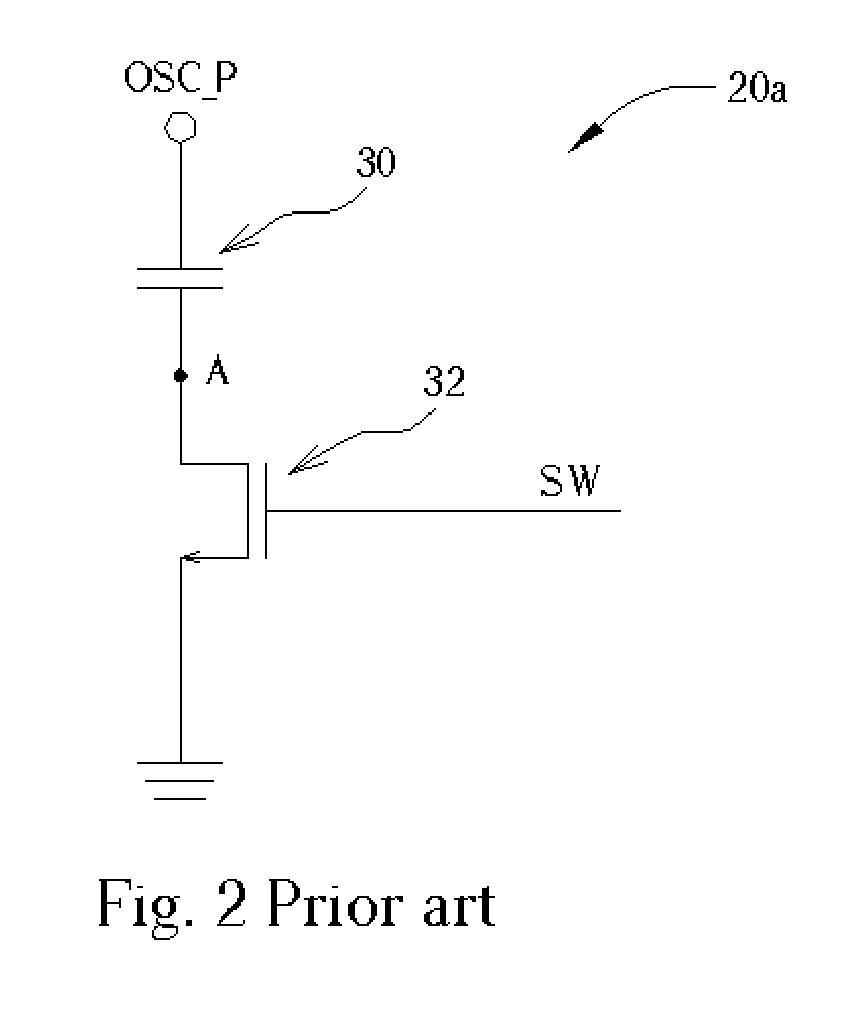

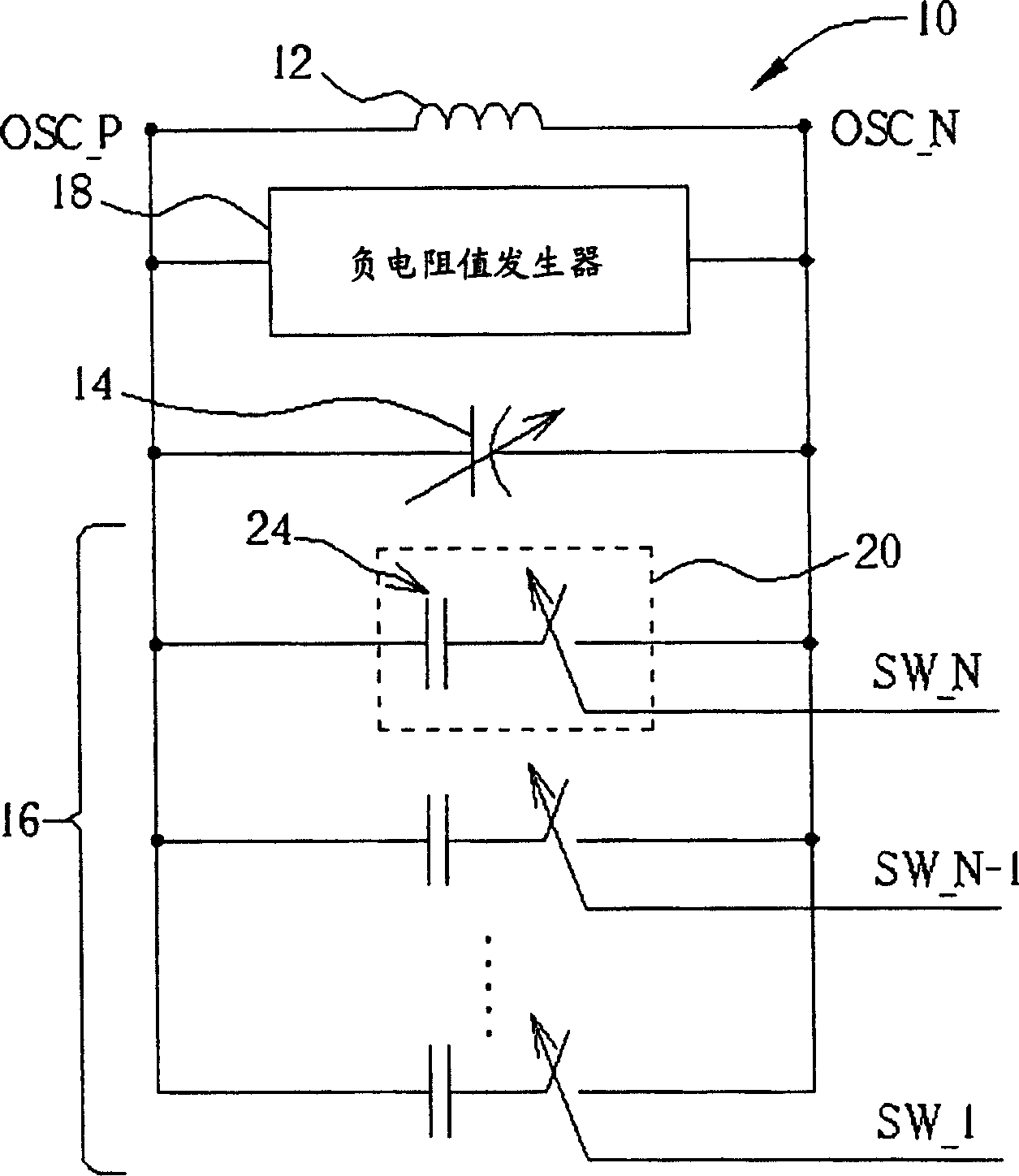

Switched capacitor circuit capable of minimizing clock feedthrough effect and having low phase noise and method thereof

ActiveUS7002393B2Minimize impactComputing operations for integral formationComputing operations for integration/differentiationPhase noiseControl signal

Owner:MEDIATEK INC

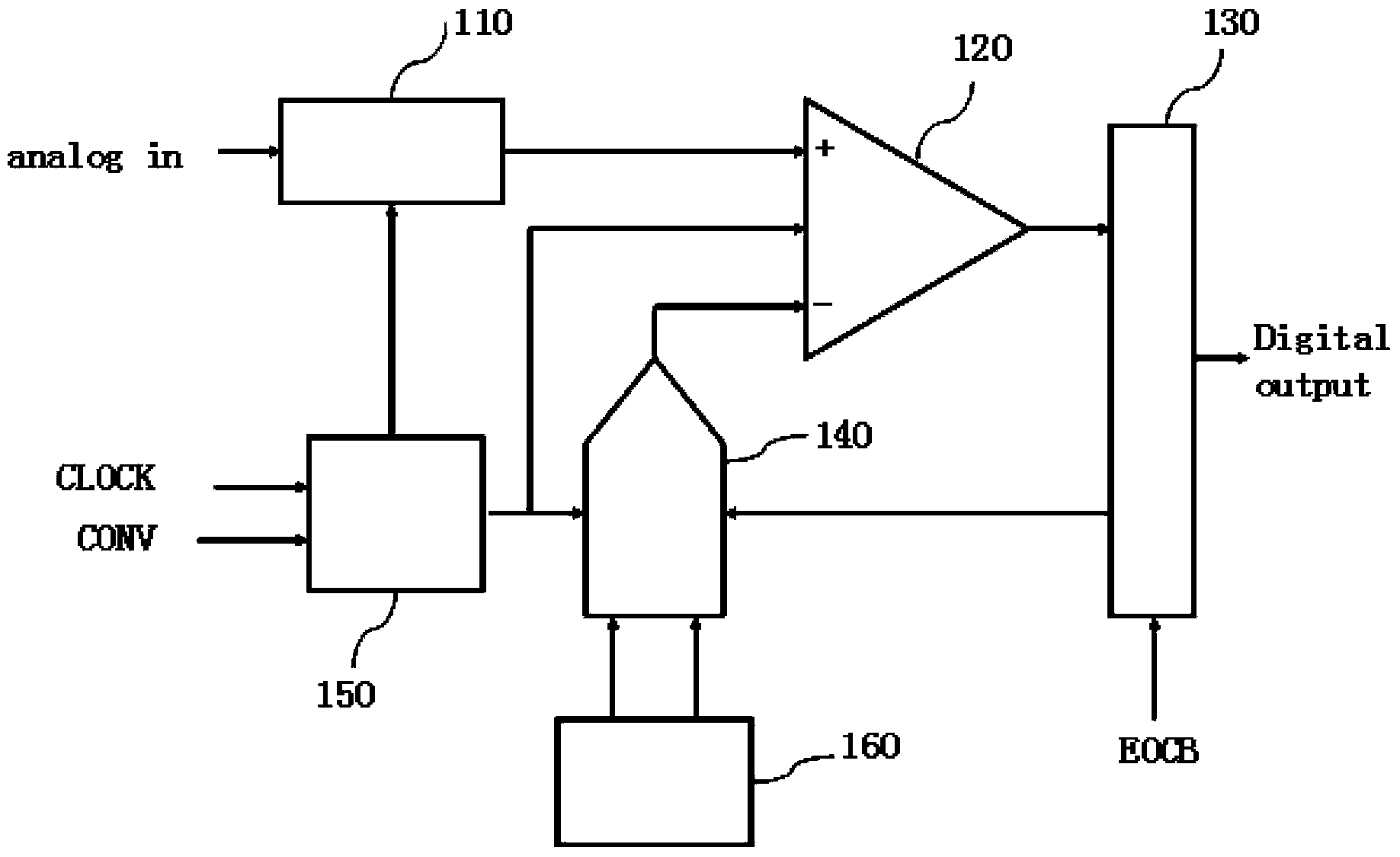

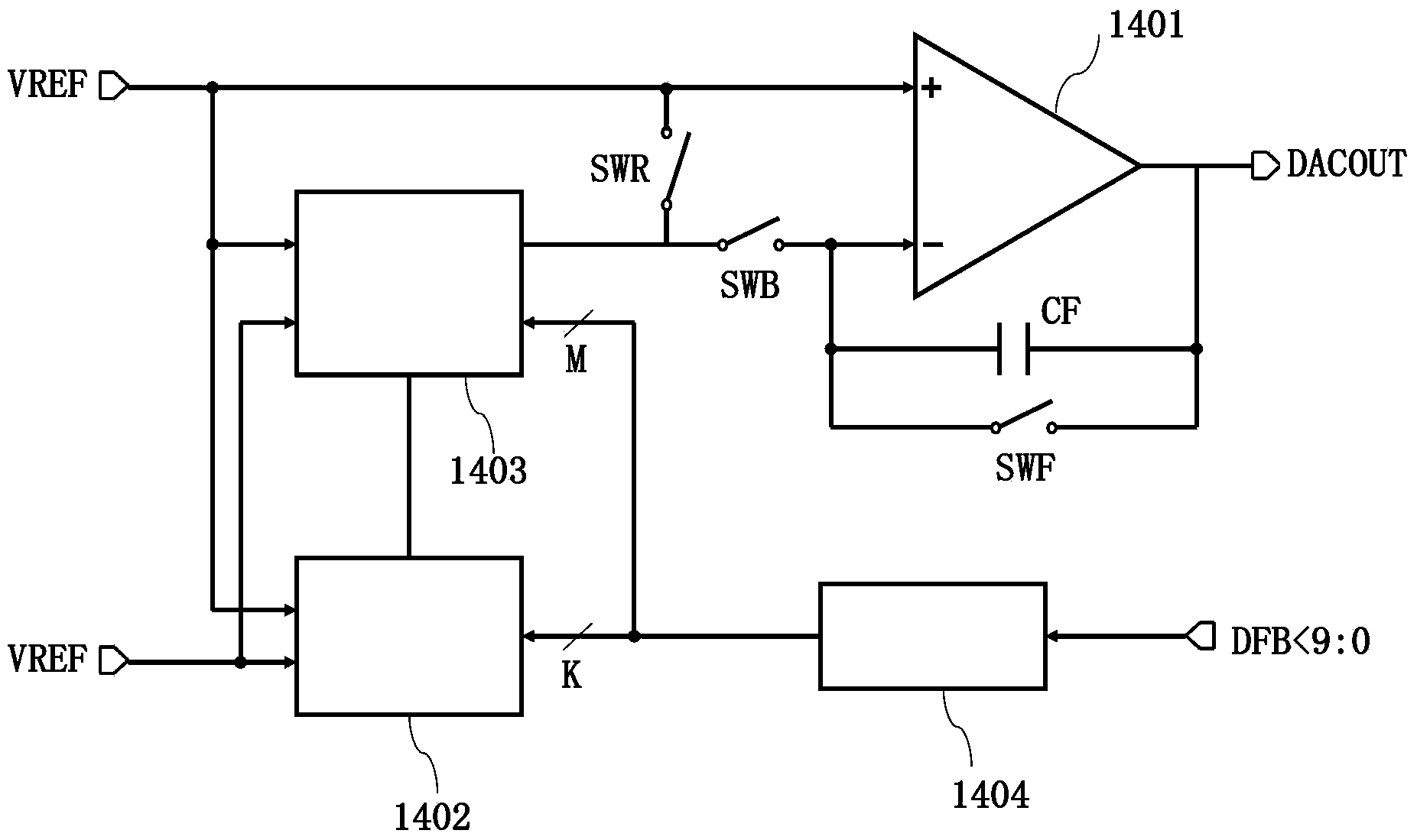

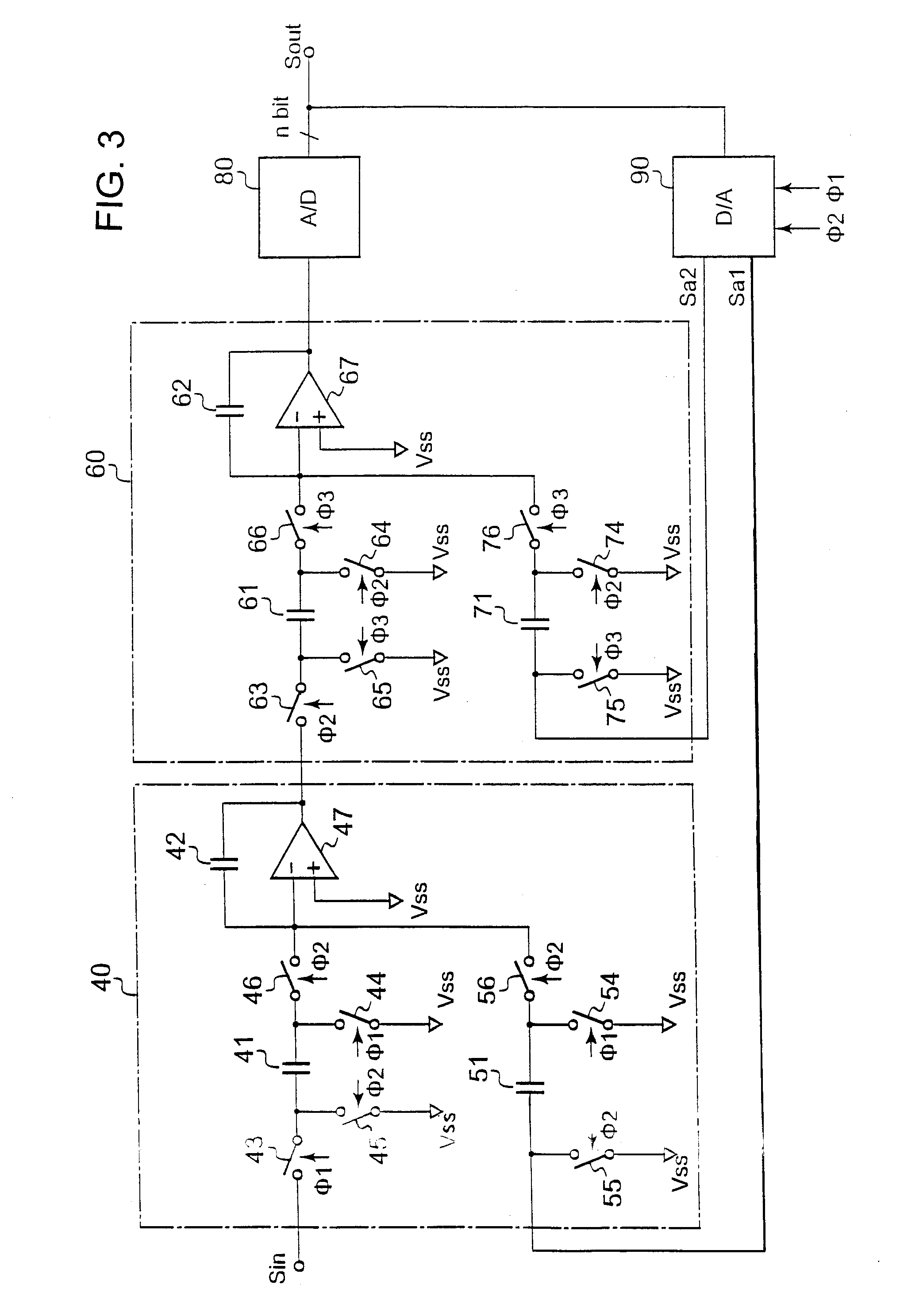

Successive approximation type analog-to-digital conversion device

InactiveCN104283562AReduce load capacitanceSmall working currentAnalogue/digital conversionElectric signal transmission systemsShift registerCapacitance

The invention discloses a successive approximation type analog-to-digital conversion device. The successive approximation type analog-to-digital conversion device comprises a sample-and-hold circuit, a comparator, a shift register, a digital-to-analog converter, a clock generation circuit and a reference voltage generation circuit. The minimum sampling error can be obtained by adopting the independent sample-and-hold circuit, and a most significant bit charge scaling digital-to-analog converter body, a least significant bit voltage scaling digital-to-analog converter body, an amplifier and the like of the digital-to-analog converter form a closed-loop switched capacitor amplifier. Due to the structure, the influence of charge injection and clock feed-through can be eliminated, the load capacitance of the amplifier can be reduced, and accordingly the power consumption can be reduced. In addition, a gapping switch is additionally arranged between the charge scaling digital-to-analog converter body and the amplifier for isolation, and therefore additional charging current caused by charge averaging can be eliminated.

Owner:上海明波通信技术股份有限公司

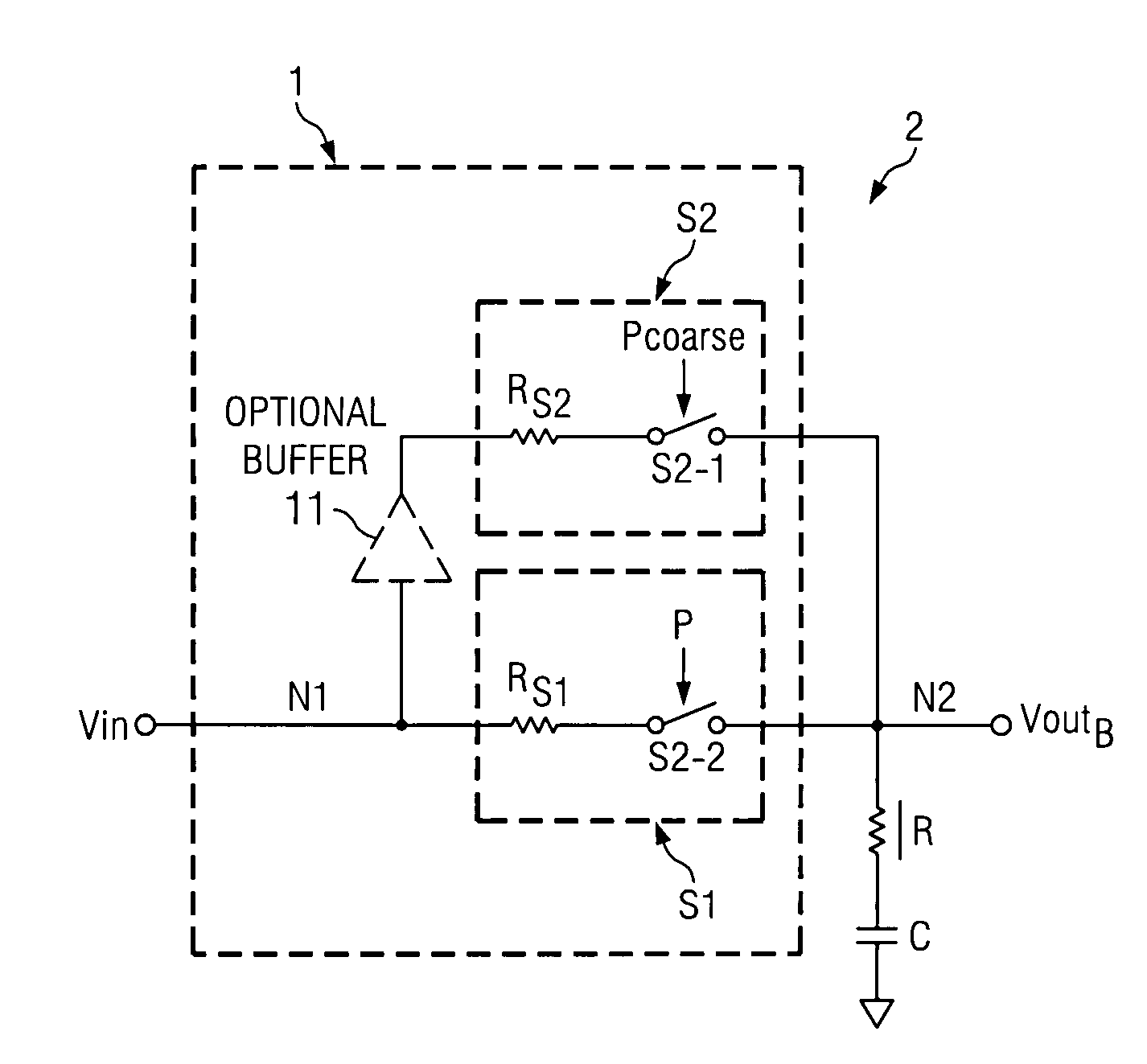

Circuit and method for reducing charge injection and clock feed-through in switched capacitor circuits

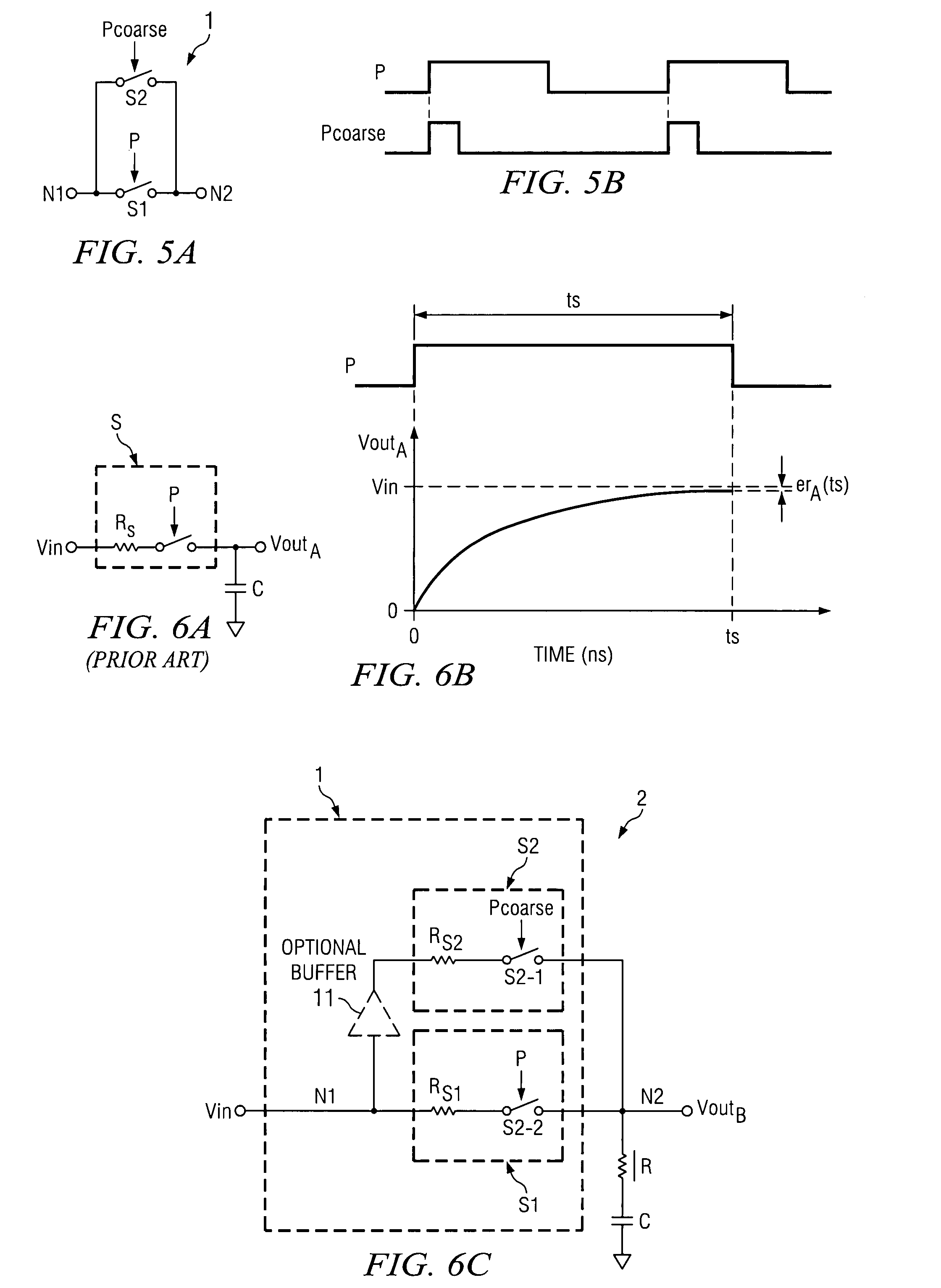

ActiveUS7663424B2Reduce charge injectionReducing charge injection mismatch and mismatchPower reduction in field effect transistorsComputing operations for integral formationCharge injectionEngineering

A low charge injection, low clock feed-through switch (1) has an input signal (Vin) applied both to the sources of first (S1) and second (2) switching transistors. A first clock signal (P) having pulses of a first duration ts is applied to a gate of the first switching transistor, and a second clock signal (Pcoarse) having pulses of a second duration m×ts substantially less than the first duration is applied to a gate of the second switching transistor. A capacitor (C) is charged toward the input voltage through both the first and second switching transistors during the pulse of the second clock signal. The capacitor is charged further toward the input voltage during a remaining portion of the pulse of the first clock signal.

Owner:TEXAS INSTR INC

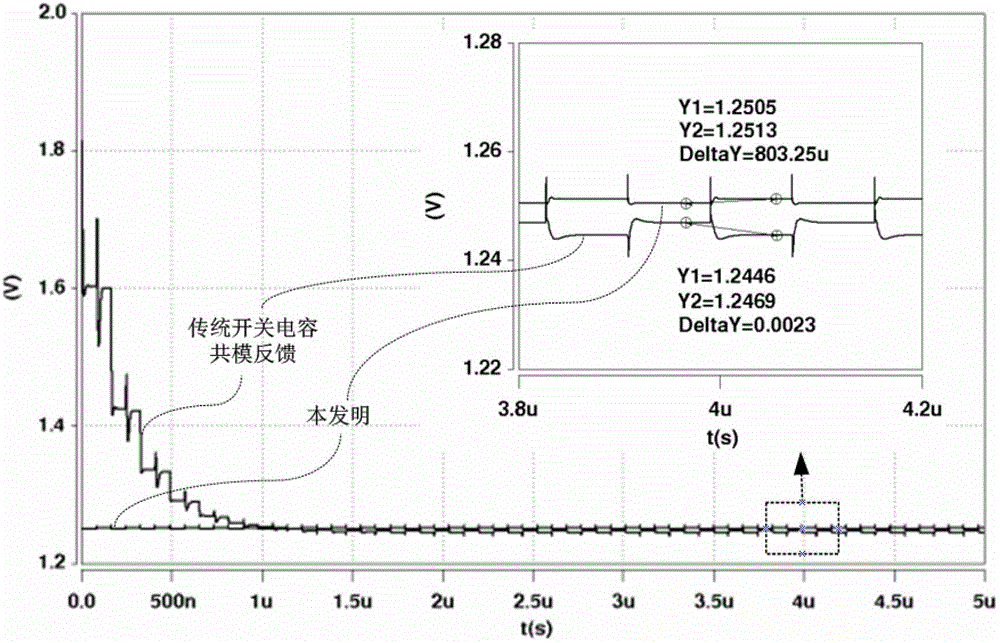

Switched capacitor common-mode feedback structure

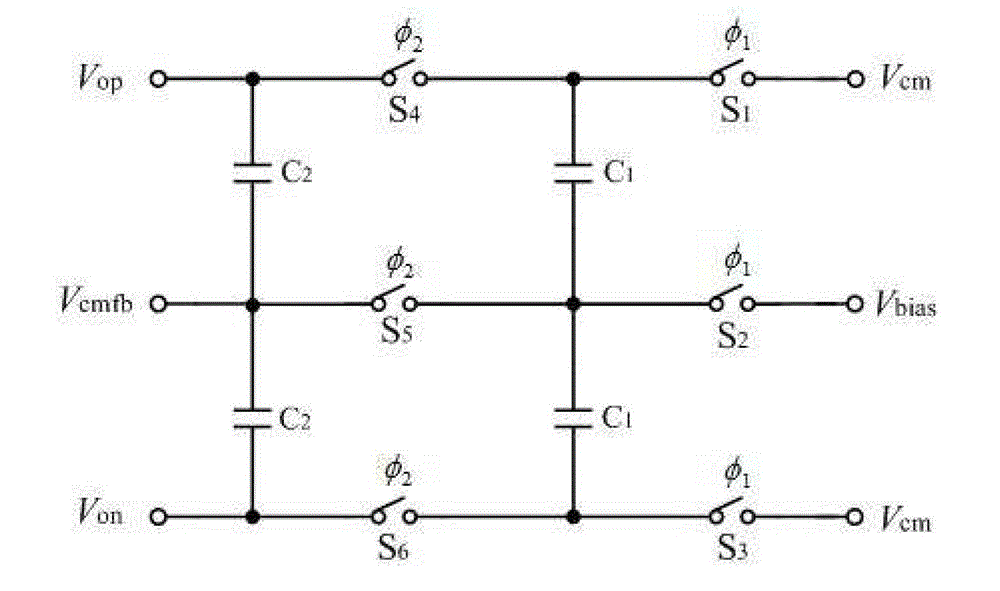

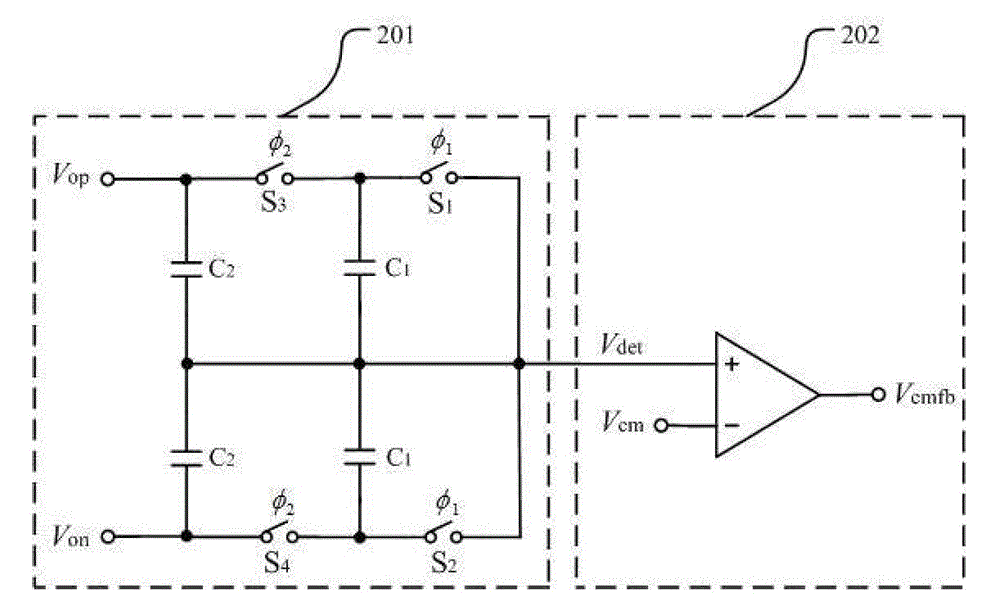

InactiveCN102751956AImprove detection accuracyImprove output swingDifferential amplifiersDc-amplifiers with dc-coupled stagesCapacitanceCharge injection

The invention discloses a switched capacitor common-mode feedback structure and belongs to an analogue integrated circuit technique. The switched capacitor common-mode feedback structure comprises a common-mode detection switched capacitor circuit and an operational amplifier circuit, wherein the common-mode detection switched capacitor circuit is composed of four switches and four capacitors and is capable of amplifying a fully differential operational amplifier output swing, detecting a fully differential operational amplifier output common-mode voltage, and reducing influences of switch charge injection, clock feedthrough and capacitor initialized intrinsic charge on common-mode detection precision. A detected common-mode voltage and an ideal common-mode voltage are compared and amplified through an operational amplifier, then common-mode feedback current source bias voltage is output, the establishing time of the common-mode voltage can be effectively reduced, and the common-mode voltage precision is improved.

Owner:UNIV OF ELECTRONICS SCI & TECH OF CHINA

Switched capacitor circuit capable of eliminating clock feedthrough by complementary control signals for digital tuning VCO

ActiveUS7015742B2Computing operations for integral formationComputing operations for integration/differentiationDigital tuningCapacitance

A differential switched capacitor circuit for use in a voltage controlled oscillator (VCO) capable of eliminating clock feedthrough and preventing an unwanted momentary frequency shift and drift in the VCO output frequency when the switched capacitor circuit is shut off. A center switch element connects a positive side capacitance node with a negative side capacitance node depending on a first control signal. A positive side primary switch element and a negative side primary switch element connect the positive and negative side capacitance nodes depending on the first control signal. A positive side additional switch element and negative side additional switch element with control signals complementary to the first control signal cancel the clock feedthrough of the center switch and the positive and negative side primary switch elements at the positive and negative side capacitance nodes respectively.

Owner:MEDIATEK INC

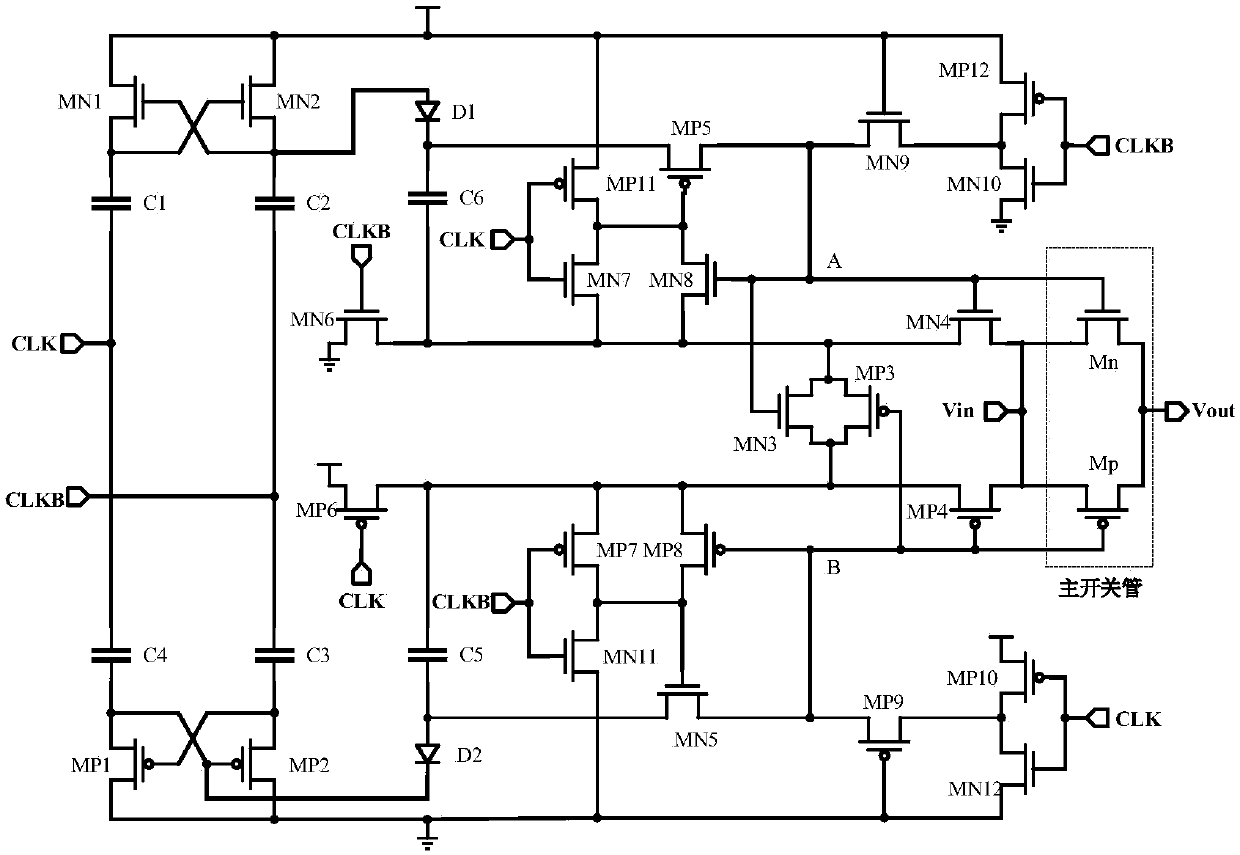

Grid voltage bootstrap switch circuit

The invention provides a grid voltage bootstrap switch circuit, and belongs to the field of analog integrated circuits. A charge pump circuit is used for charging a fifth capacitor and a sixth capacitor to make the stored charge amounts be constant, a grid voltage boosting circuit and a grid voltage reducing circuit are used for changing the grid voltages of an NMOS switch tube and a PMOS switch tube to maintain the grid voltages as constant values, and a switching circuit is used for controlling the charging of the charge pump circuit and the opening and closing of the grid voltage boosting circuit and the grid voltage reducing circuit. The grid voltage bootstrap switch circuit provided by the invention uses the NMOS switch tube and the PMOS switch tube to connect input signals to the output at the same time, thereby reducing the on-resistance of the switch; by using a parallel connection mode of the NMOS switch tube and the PMOS switch tube, the channel charge injection effects of the NMOS switch tube and the PMOS switch tube caused by clock changes cancel each other, and the clock feedthrough effects cancel each other as well, thereby improving the linearity of the switch; and by using a diode to charge the capacitor, the circuit does not have an overvoltage device, thus improving the reliability of the circuit.

Owner:UNIV OF ELECTRONICS SCI & TECH OF CHINA

Analog-to-digital converter and electronic equipment

ActiveCN102571091AInhibition effectHigh precisionAnalogue-digital convertersAnalog circuit designCharge injection

The invention provides an analog-to-digital converter and electronic equipment and belongs to the field of analog circuit design. According to a gate-voltage bootstrapped switch circuit in the analog-to-digital converter, two transistors are connected with each other through a transmission gate (TG) and connected with an input signal Vin. By connecting the two transistors through the TG, influence of charge injection and clock feed-through on the input signal Vin can be effectively eliminated, and sampling accuracy is improved.

Owner:昆山启达微电子有限公司

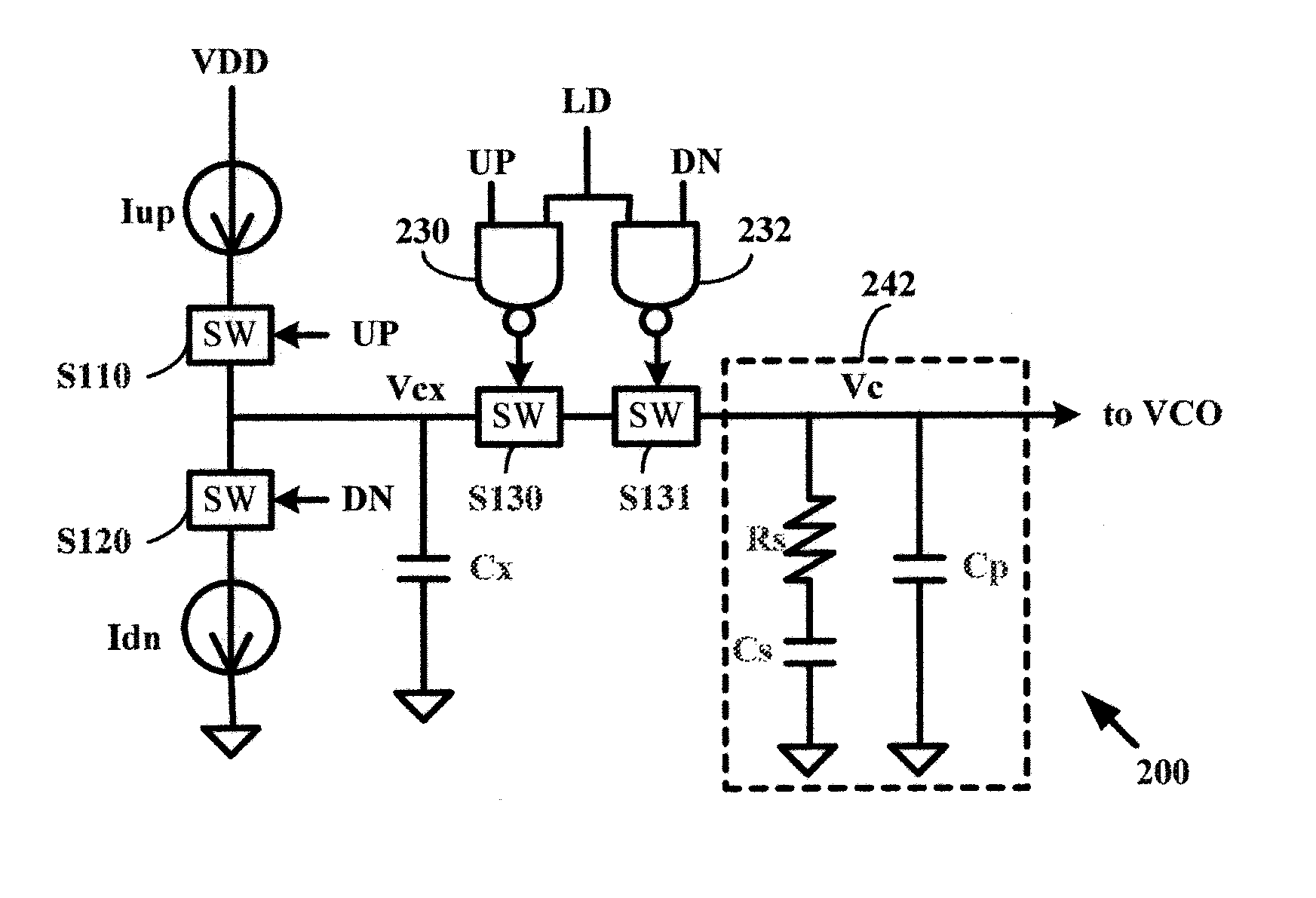

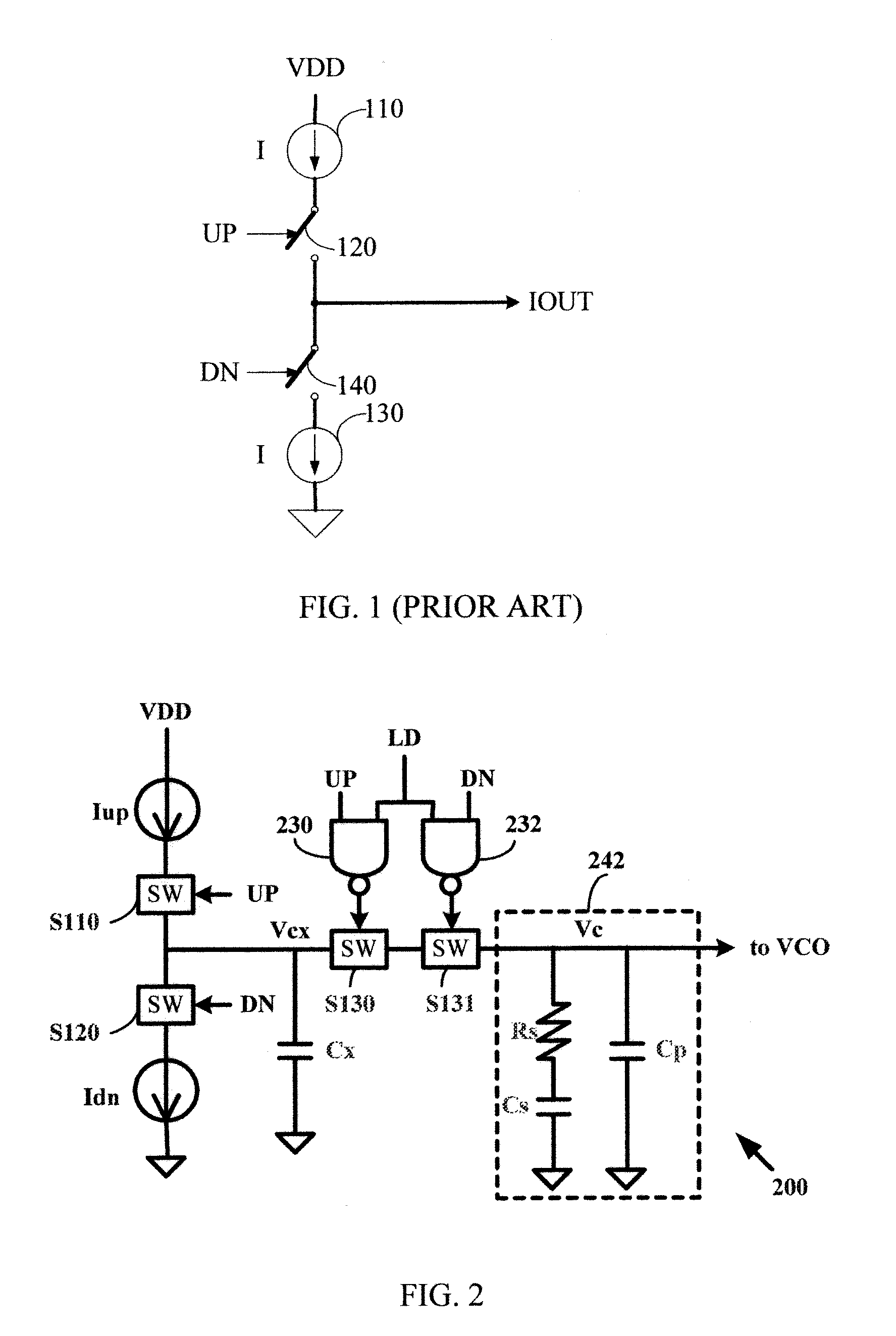

Charge pump circuit and method thereof

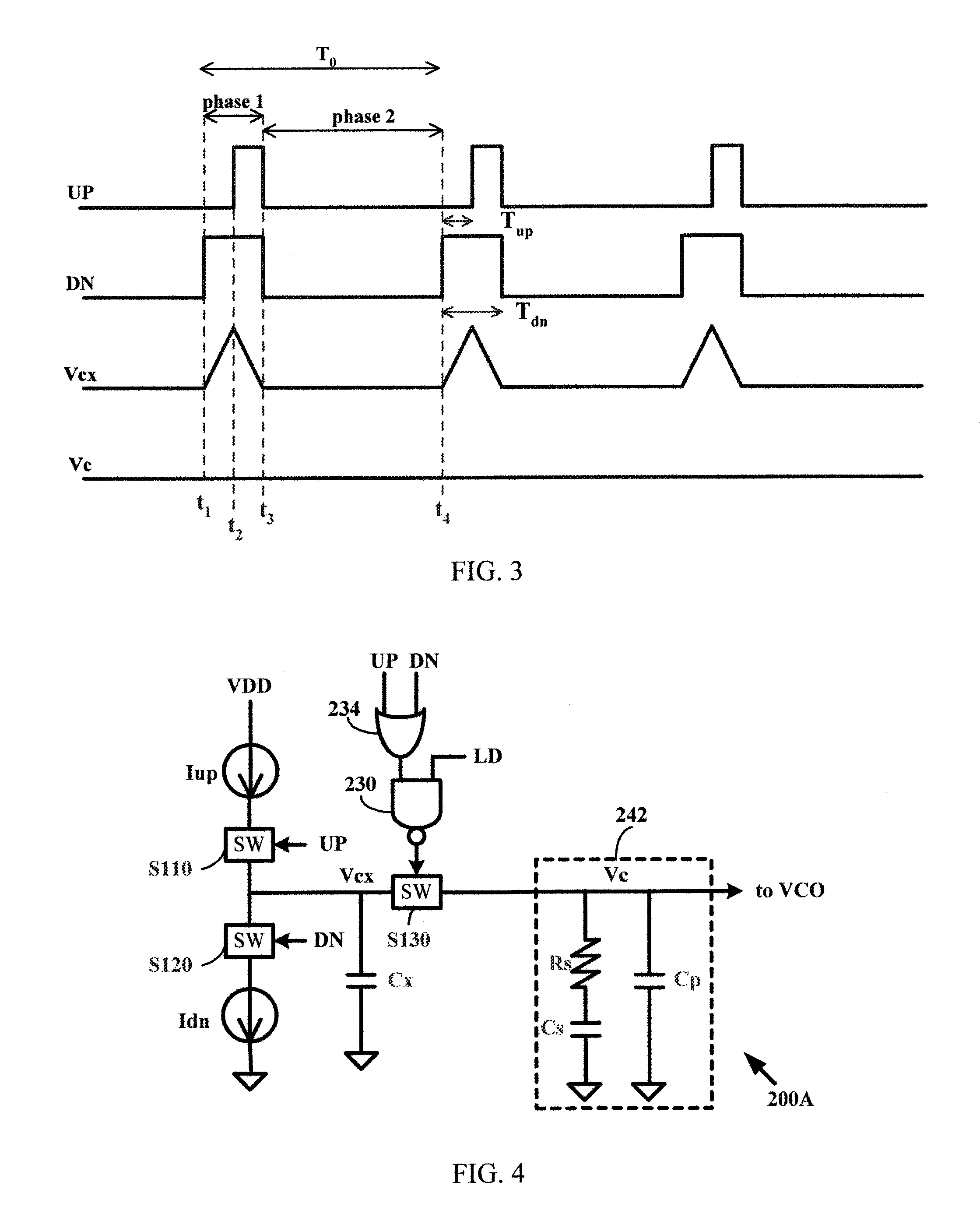

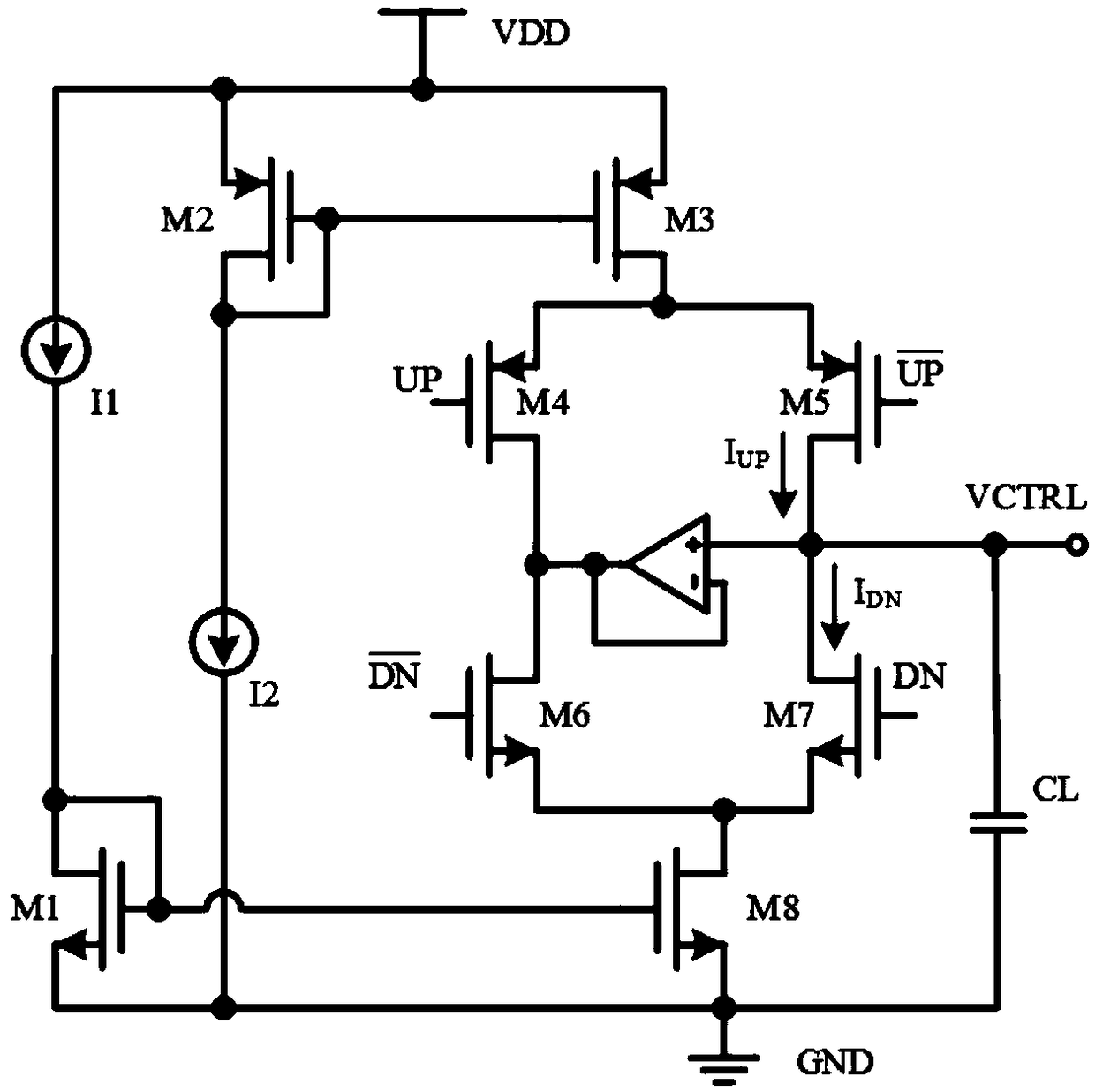

A charge pump circuit capable of canceling current mismatch and suppressing clock feedthrough. The charge pump circuit comprises a current source enabled by a first logical signal, a current sink enabled by a second logical signal, an integrating capacitor coupled to both the current source and the current sink, and a switching device coupled between the integrating circuit and an output node. The switching device has two states. The switching device is set to a first state whenever a third logical signal is asserted and one of the first logical signal, the second logical signal, and a modulating signal is enabled. The switching device is set to a second state whenever the third logical signal is de-asserted, or none of the first logical signal, the second logical signal, and the modulating signal are asserted.

Owner:REALTEK SEMICON CORP

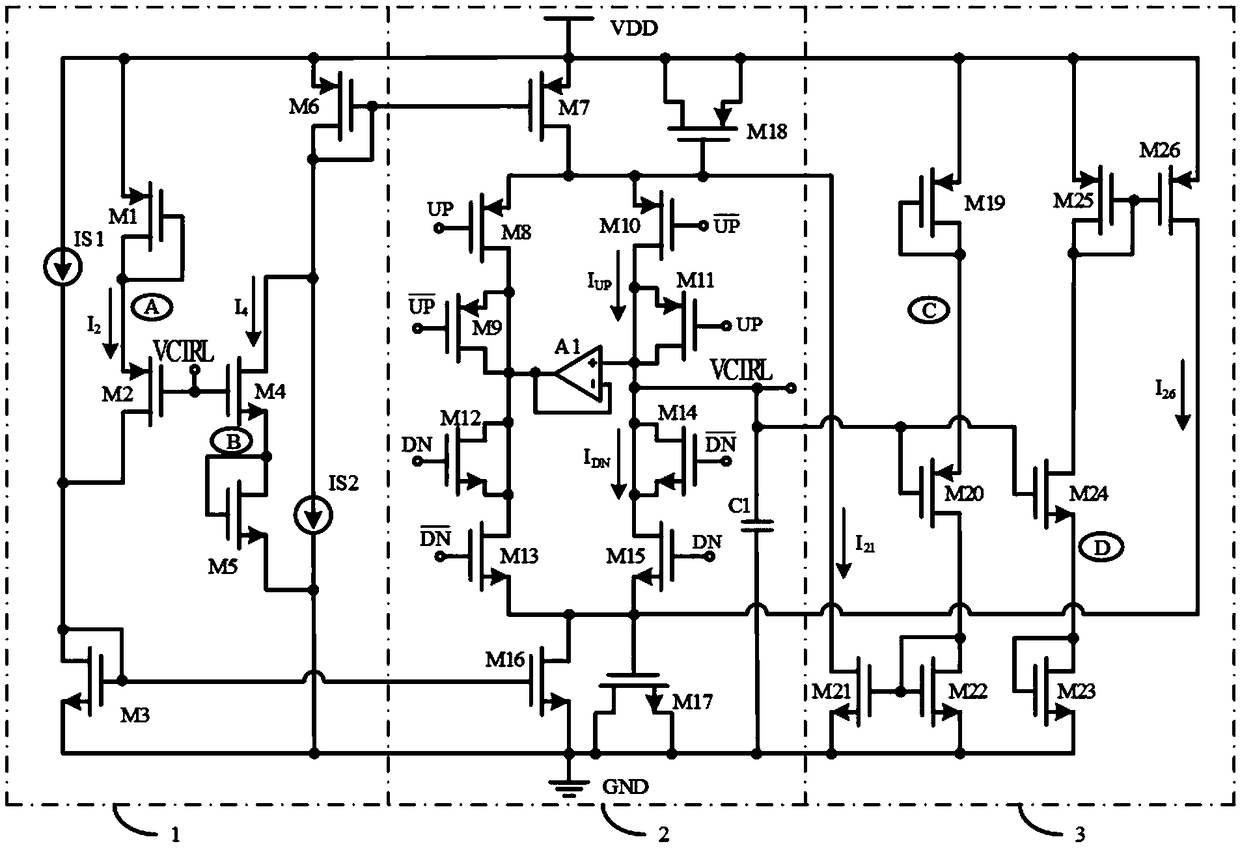

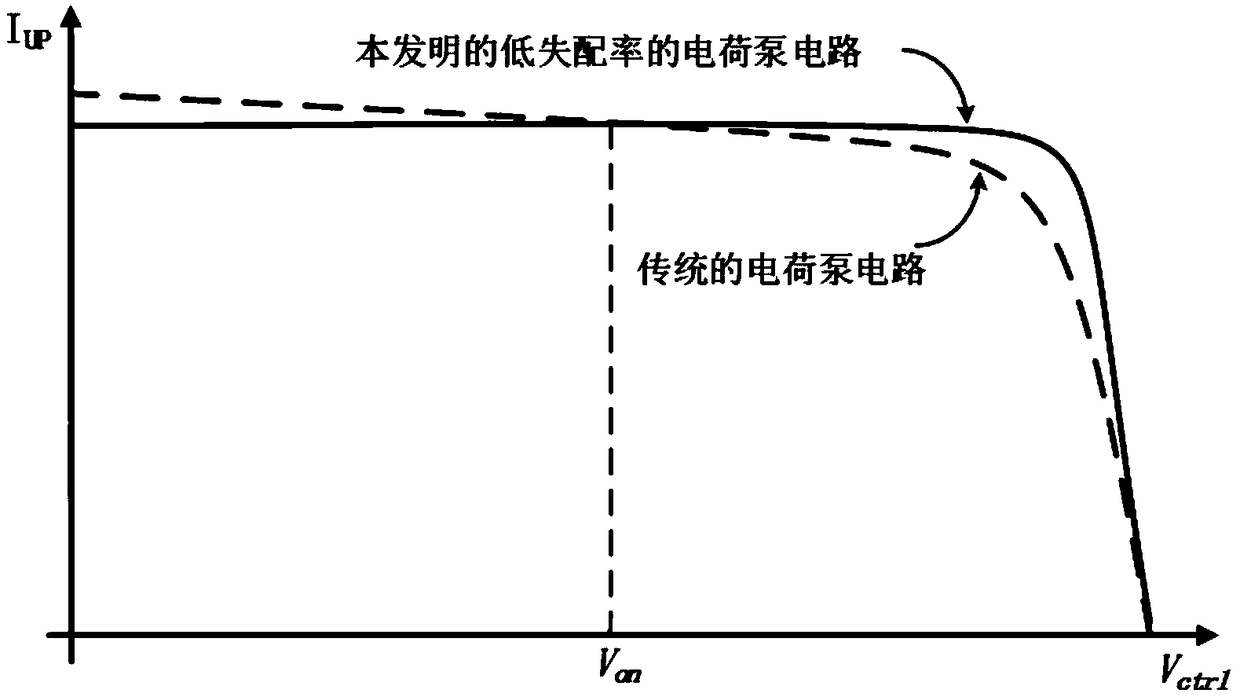

Charge pump circuit with low miss ratio for delay phase-locked loop

ActiveCN109194327AReduce current glitchesMismatch Rate ReductionPulse automatic controlCapacitancePhase-locked loop

The present invention provides a charge pump circuit with low miss ratio for a delay phase-locked loop. The charge pump circuit mainly comprises a biasing circuit with current compensation, a currentwheeled charge pump circuit and a negative feedback current compensation circuit. The current wheeled charge pump circuit employs a virtual switch tube to effectively inhibit charge injection and clock feedthrough effects, MOS capacitors formed by PMOS tubes M18 and MOS capacitors formed by NMOS tubes M6 are respectively added to source and drain ends of a PMOS tube M7 and source and drain ends ofan NMOS tube M16 to reduce the current glitch when the switch tube of the charge pump circuit opens or closes at the same time; and a compensating current I2, a compensating current I4, a compensating current I21 and a compensating current I26 are led into the current wheeled charge pump circuit to reduce the miss ratio of the charge / discharge current of the charge pump circuit so as to achieve acharge pump circuit with low miss ratio for a delay phase-locked loop.

Owner:CHONGQING UNIV OF POSTS & TELECOMM

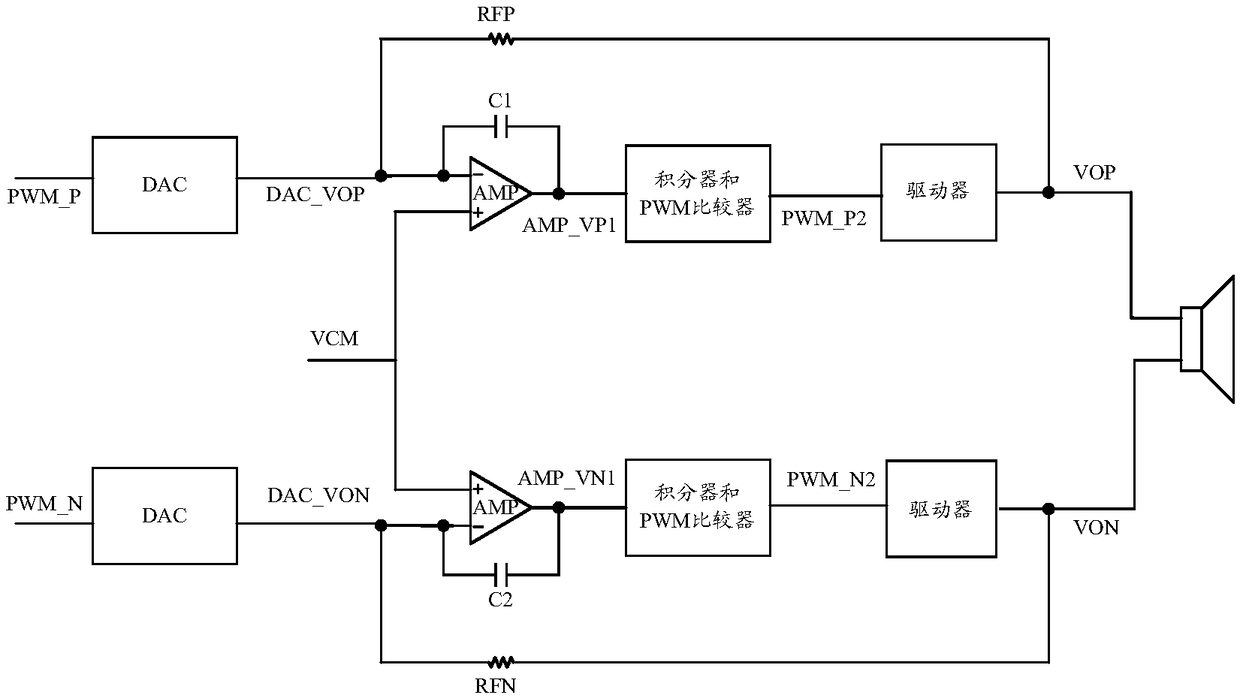

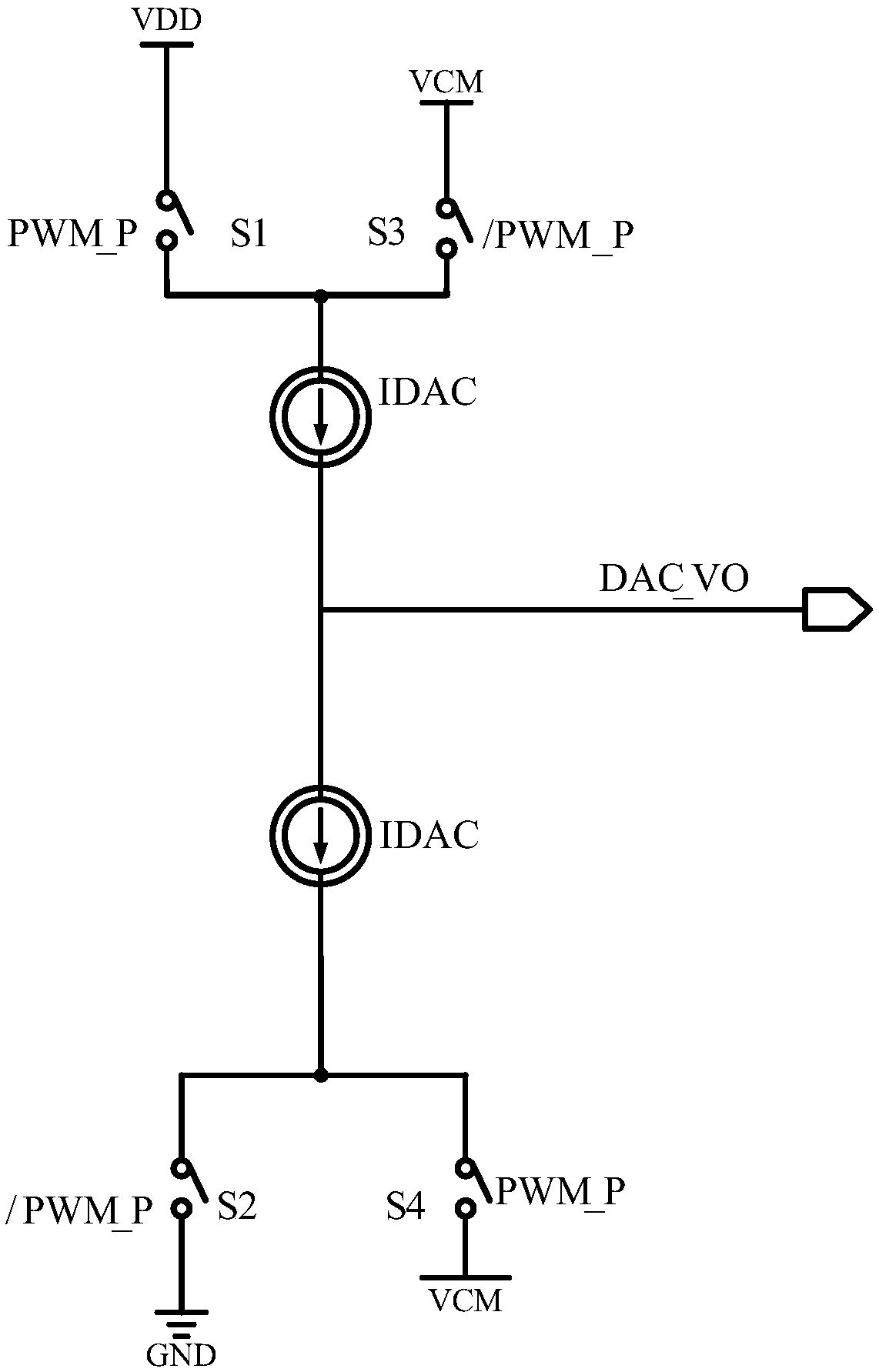

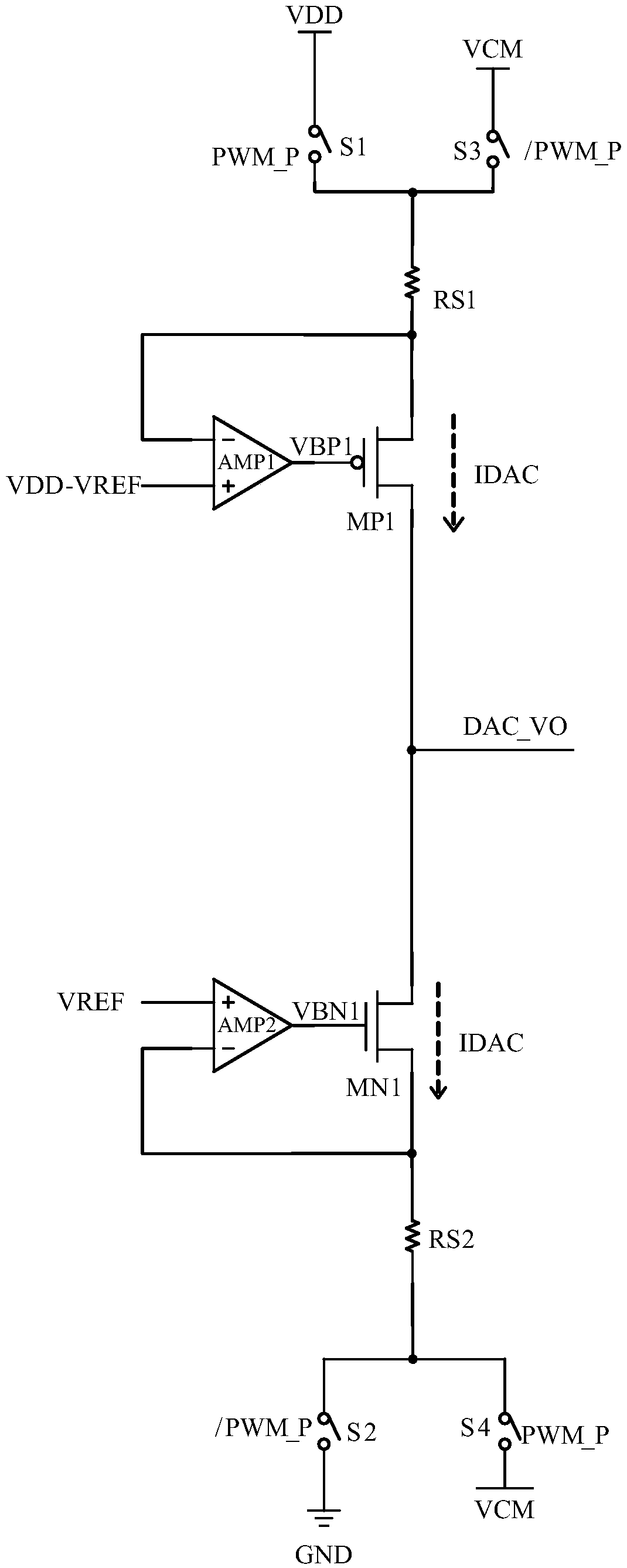

A digital-to-analog converter and a digital power amplifier subsystem

ActiveCN109004936ASize limitReduce adverse effectsAnalogue/digital conversionAmplifier modifications to reduce non-linear distortionCharge injectionLinear region

The invention provides a digital-to-analog converter and a digital power amplifier subsystem, The clock feed-through effect and the channel charge injection phenomenon generated by a first switch, a second switch, a third switch and a fourth switch of the digital-to-analog converter during the switching process are not loaded in the output signal of the digital-to-analog converter by acrossing thefirst current source and the second current source. The invention avoids the adverse effects of clock feed-through effect and channel charge injection phenomenon caused by the first switch, the second switch, the third switch and the fourth switch on the output signal of the digital-to-analog converter in the switching process, so that the sizes of the first switch, second switch, the third switch and the fourth switch are not limited, a larger size switch tube may be used as the first switch, the second switch, the third switch, and the fourth switch to solve the problem that the first current source and the second current source operate in the linear region due to excessive voltage drops consumed by the first switch, the second switch, the third switch, and the fourth switch.

Owner:SHANGHAI AWINIC TECH CO LTD

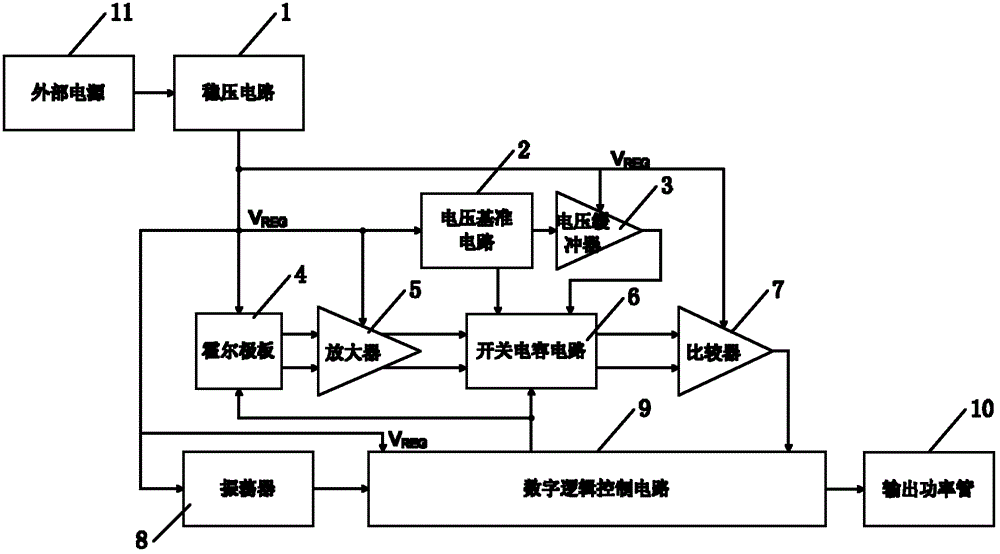

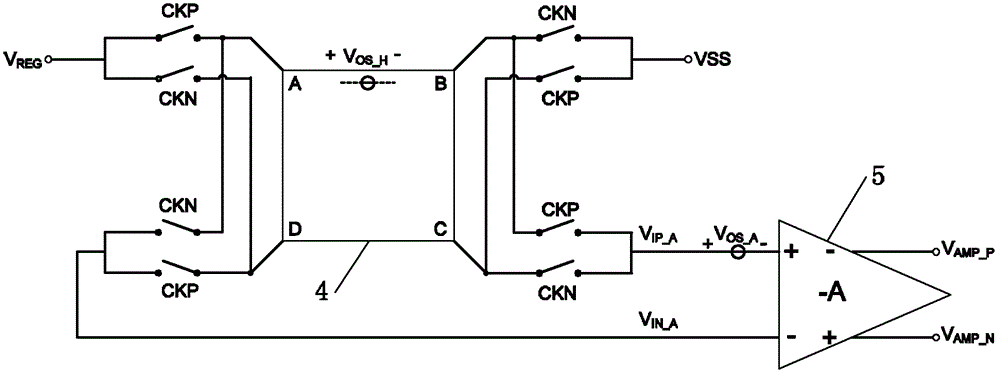

One-chip latch type Hall sensor

InactiveCN103063232AAvoid influenceReduce sensitivity temperature drift effectSpecial purpose recording/indication apparatusCapacitanceCharge injection

The invention relates to a one-chip latch type Hall sensor which comprises a Hall counter electrode, an amplifier, a switched capacitance circuit and a comparator, wherein the Hall counter electrode, the amplifier, the switched capacitance circuit and the comparator are sequentially connected. The one-chip latch type Hall sensor further comprises a voltage reference circuit which is connected with the switched capacitance circuit, wherein the Hall counter electrode is controlled by a first clock signal and a second clock signal, the first clock signal and the second clock signal are input from outside, the switched capacitance circuit comprises a first capacitor, a second capacitor, a third capacitor and a fourth capacitor, the first capacitor, the second capacitor, the third capacitor and the fourth capacitor are respectively provided with an upper counter electrode and a lower counter electrode, and the first clock and the second clock signal are two-phase clock signals which are non-overlapped. Due to the fact that the second capacitor and the third capacitor sample a Hall signal which is amplified by the amplifier, the first capacitor and the fourth capacitor sample reference voltages which are output by the voltage reference circuit, and meanwhile a third clock signal is introduced under the condition of sampling of the first capacitor, the second capacitor, the third capacitor and the fourth capacitor, influence of a charge injection effect and a clock feed through effect on signal establishing accuracy in the moment of switching a sampling switch is avoided.

Owner:上海腾怡半导体有限公司

Switched capacitor circuit capable of minimizing clock feedthrough effect and having low phase noise and method thereof

ActiveUS20050068086A1Minimizing clock feedthrough effectReduce phase noiseComputing operations for integral formationComputing operations for integration/differentiationPhase noiseControl signal

A switched capacitor circuit includes a positive side capacitor coupled to a first positive side node; a first positive side switch element for selectively coupling the first positive side node to a second node according to a first control signal; and precharge circuit coupled to the first positive side node for precharging the first positive side node to a precharge voltage for a predetermined time when the first positive side switch element is switched off according to the first control signal, and then for charging the first positive side node to a charge voltage until the first positive side switch element is switched on according to the first control signal. By rapidly precharging the first positive side node, the clock feedthrough effect is eliminated and the locking period of the VCO is shortened. Afterwards by charging the first positive side node, the phase noise of the VCO is minimized.

Owner:MEDIATEK INC

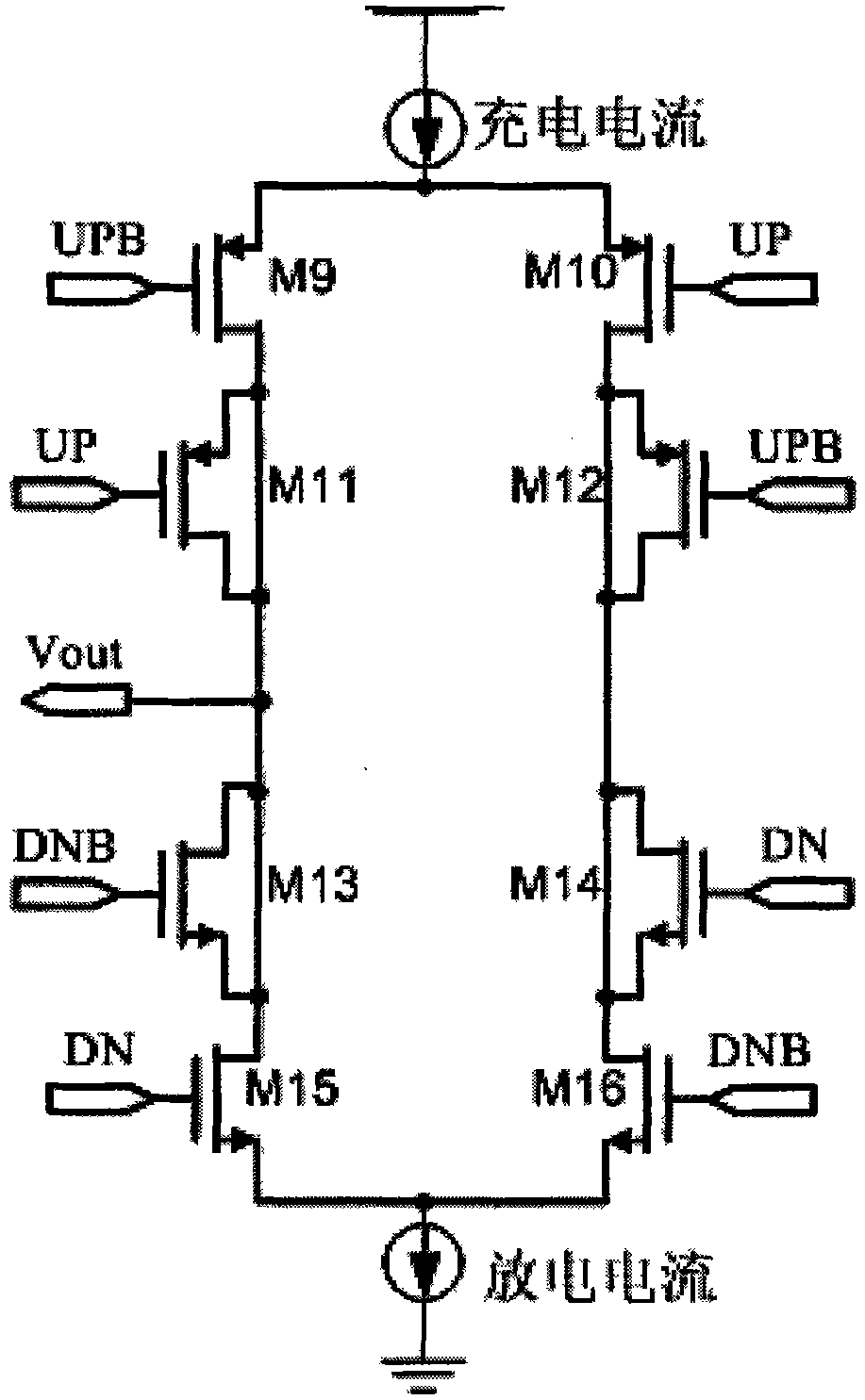

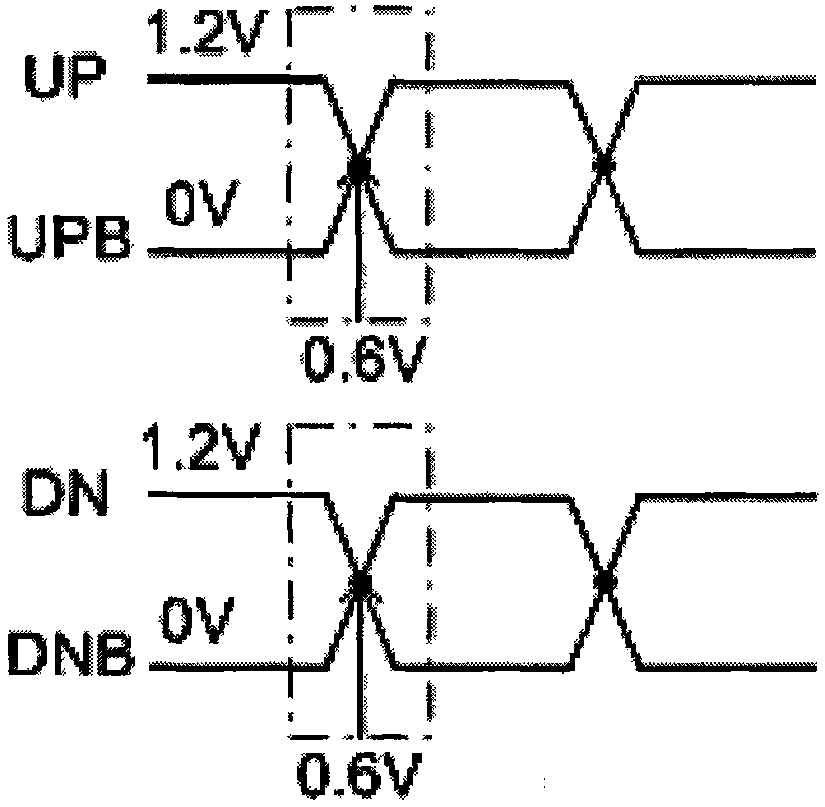

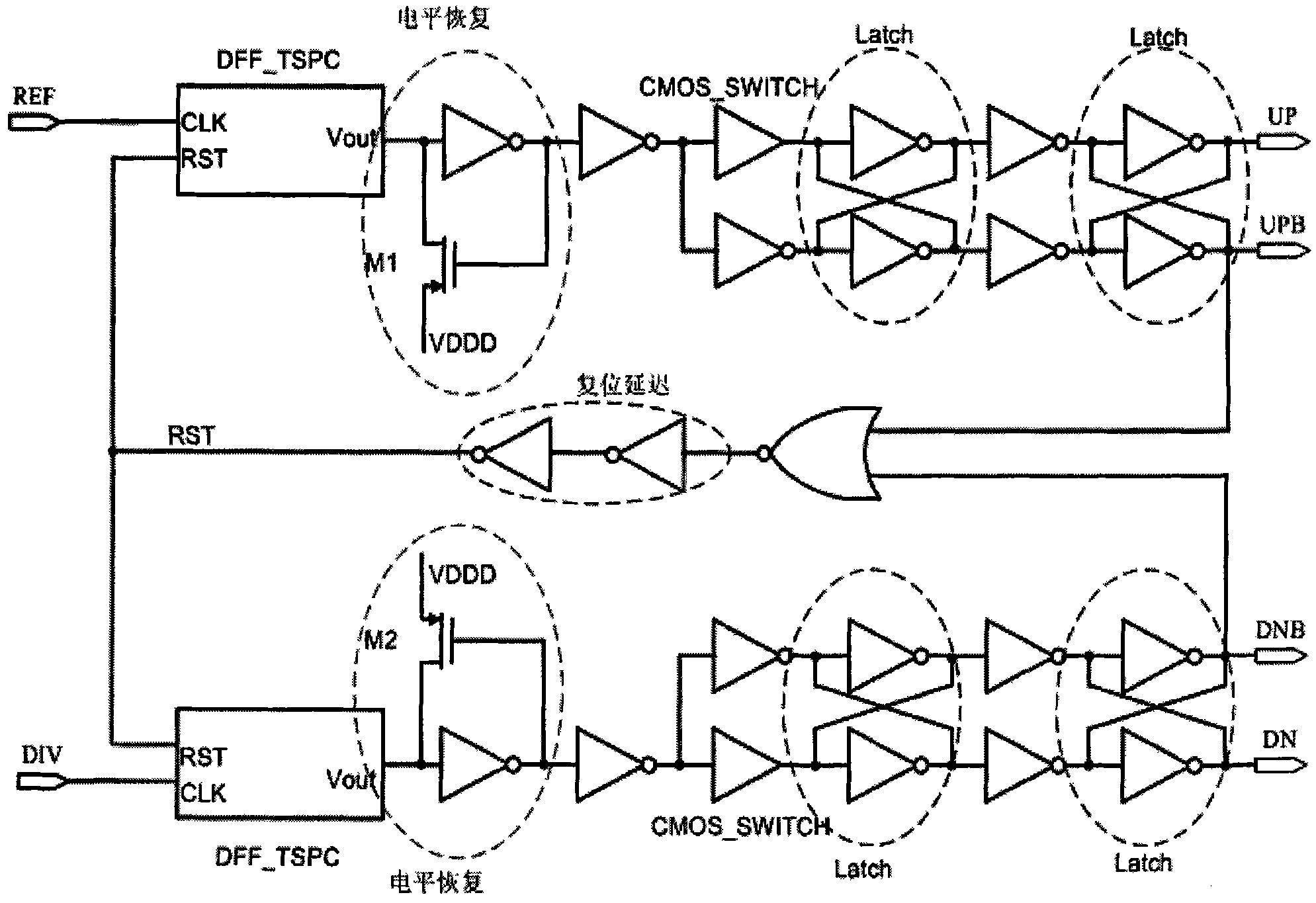

Phase frequency detector and charge pump circuits applying to integral frequency division phase-locked loop

InactiveCN101807915AReduce the impact of frequency synthesis performanceSolve the injection problemPulse automatic controlHemt circuitsEngineering

The invention belongs to the technical field of integrated circuit, in particular to PFD (phase frequency device) and CP (charge pump) circuits applying to an integral frequency division phase-locked loop. The PFD circuit adopts four Latches, so that output signals UP and UPB, and DN and DNB have very good symmetry to reduce the clock feedthrough effect and charge injection effect of the CP circuit; two PMOS tubes with small size are adopted to realize level recovery function, solve the problems that the UP, UPB, DN and DNB signals are in an uncertainty state when the circuit is electrified, and prevent the work error of the CP circuit; the CP circuit adopts two rail-to-rail constant transconductance operational amplifiers so as to solve the problems of current mismatch and charge sharing, adopts four dummy tubes so as to solve the problem of charge injection, and adopts two resistances with small size so as to effectively reduce the charge and discharge current spikes.

Owner:FUDAN UNIV

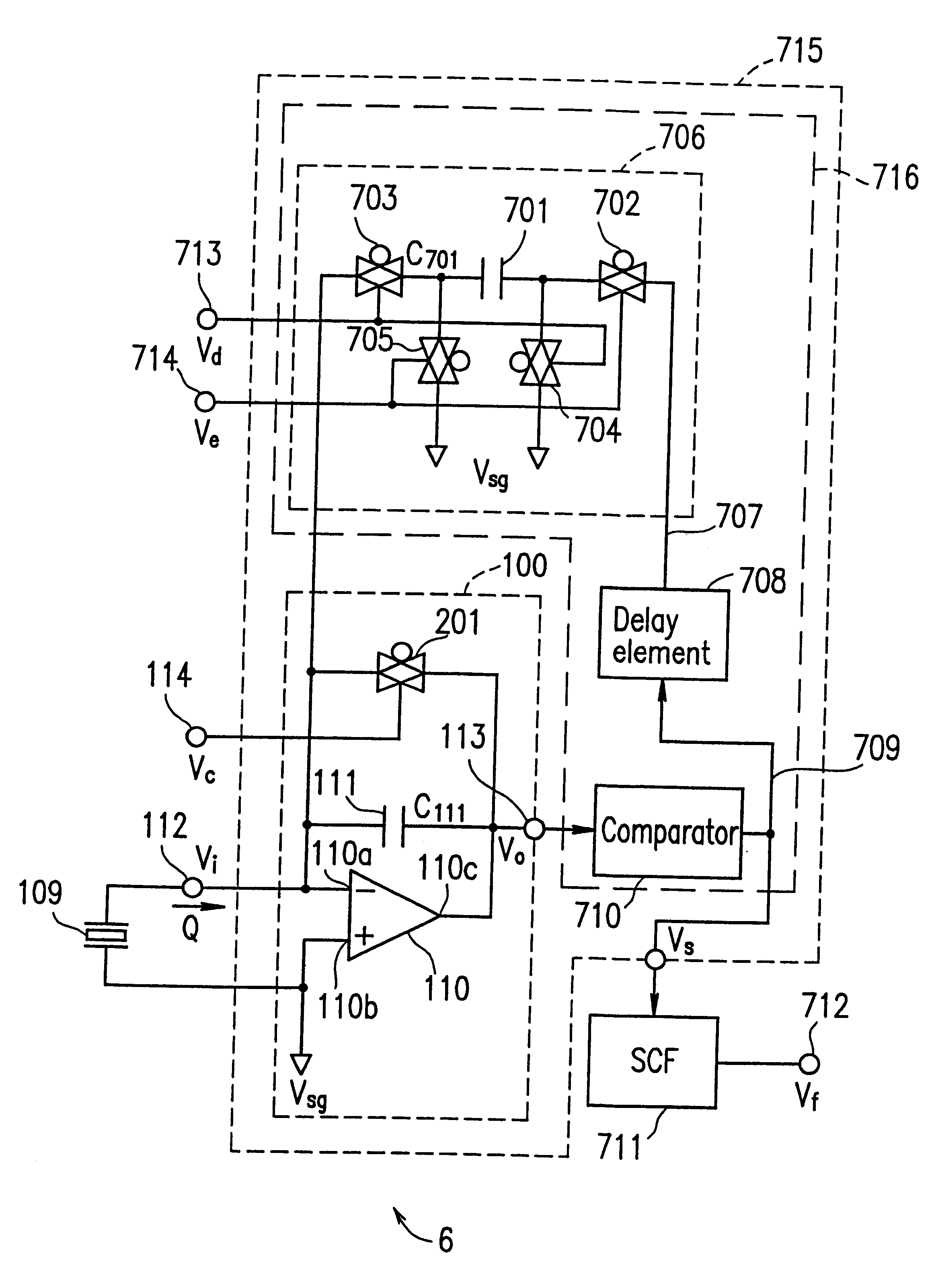

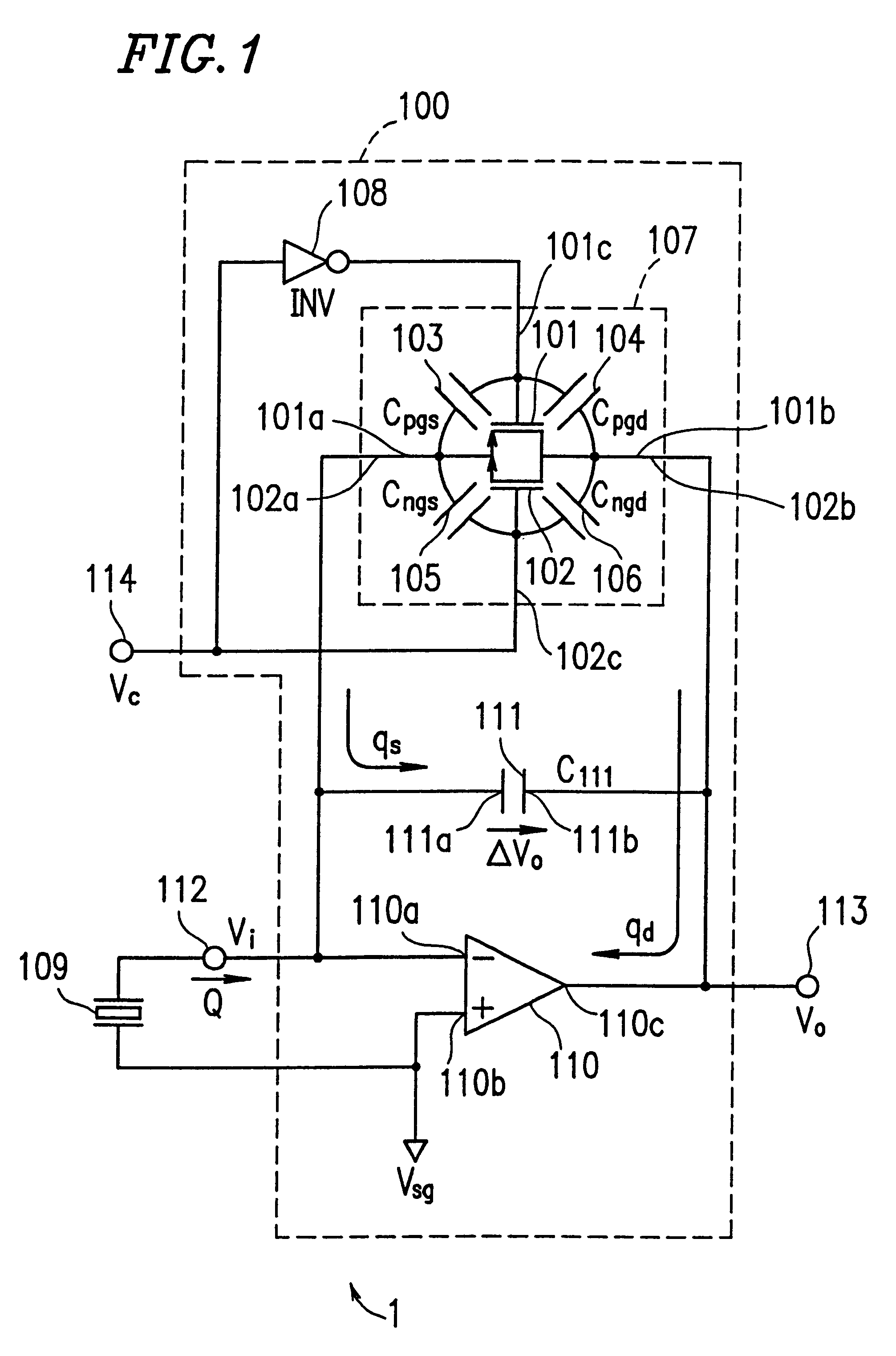

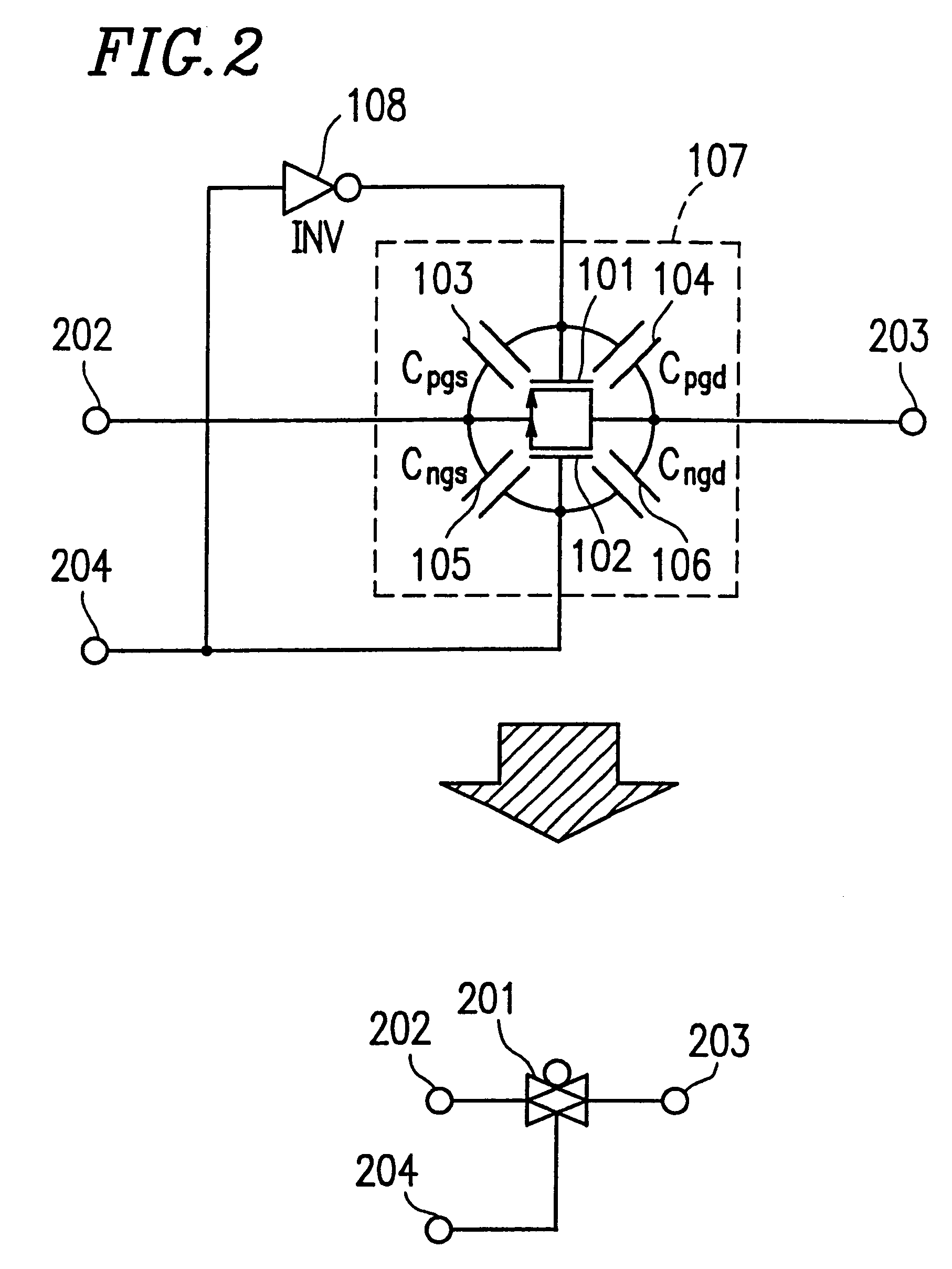

Signal processing circuit for charge generation type detection device

InactiveUS6429719B1Error in output voltageReduce high frequency noiseComputing operations for integral formationFluid pressure measurement using piezo-electric devicesCapacitanceSignal processing circuits

A signal processing circuit for a charge generation type detection device of the present invention includes a charge-voltage conversion circuit for converting a charge generated in the charge generation type detection device to a voltage. The charge-voltage conversion circuit includes: a first capacitor for storing the charge generated in the charge generation type detection device; an operational amplifier connected to the first capacitor to form a feed-back loop; and a first switch connected in parallel with the first capacitor for discharging the charge stored in the first capacitor. The first switch includes a first transistor for generating a first clock feed-through and a second transistor for generating a second clock feed-through, the first switch being configured so that at least a portion of the first clock feed-through is canceled by the second clock feed-through.

Owner:PANASONIC CORP

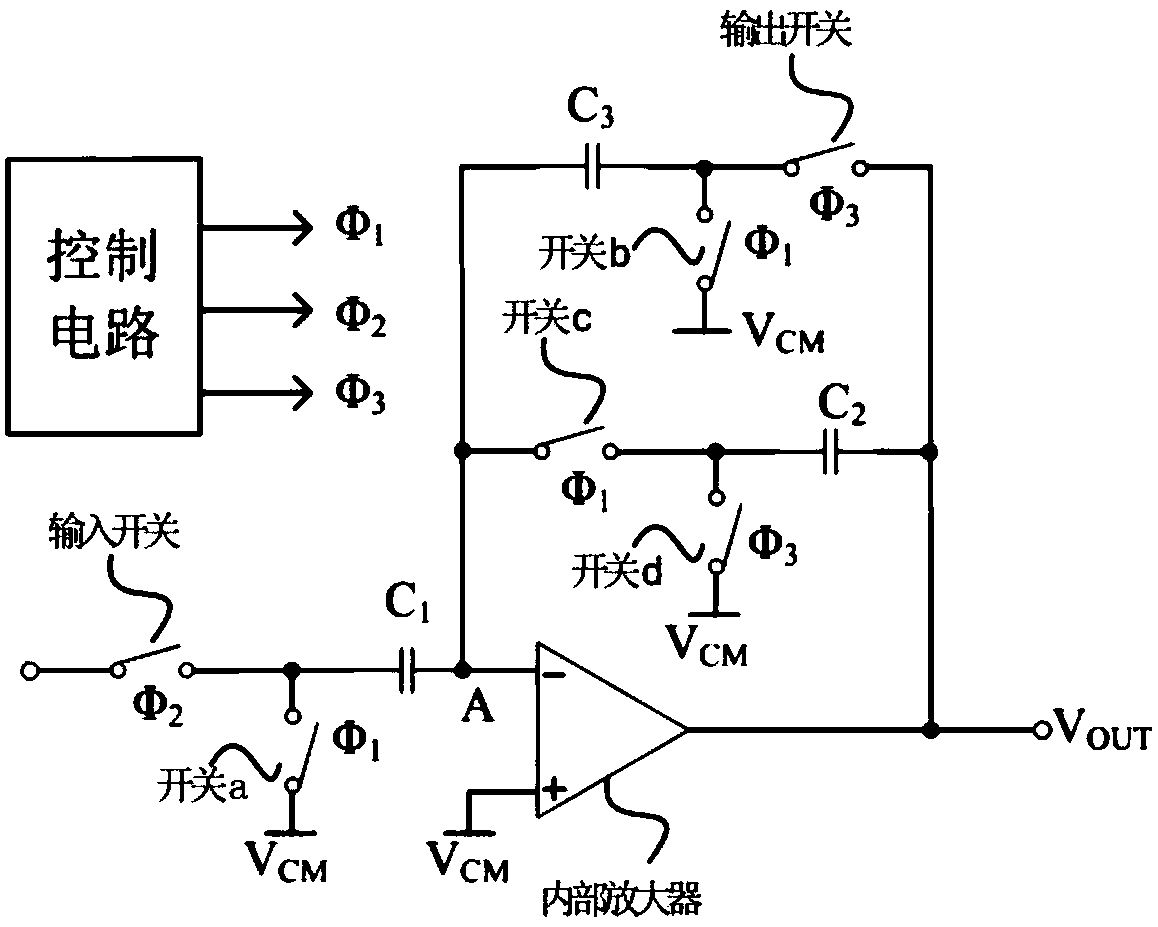

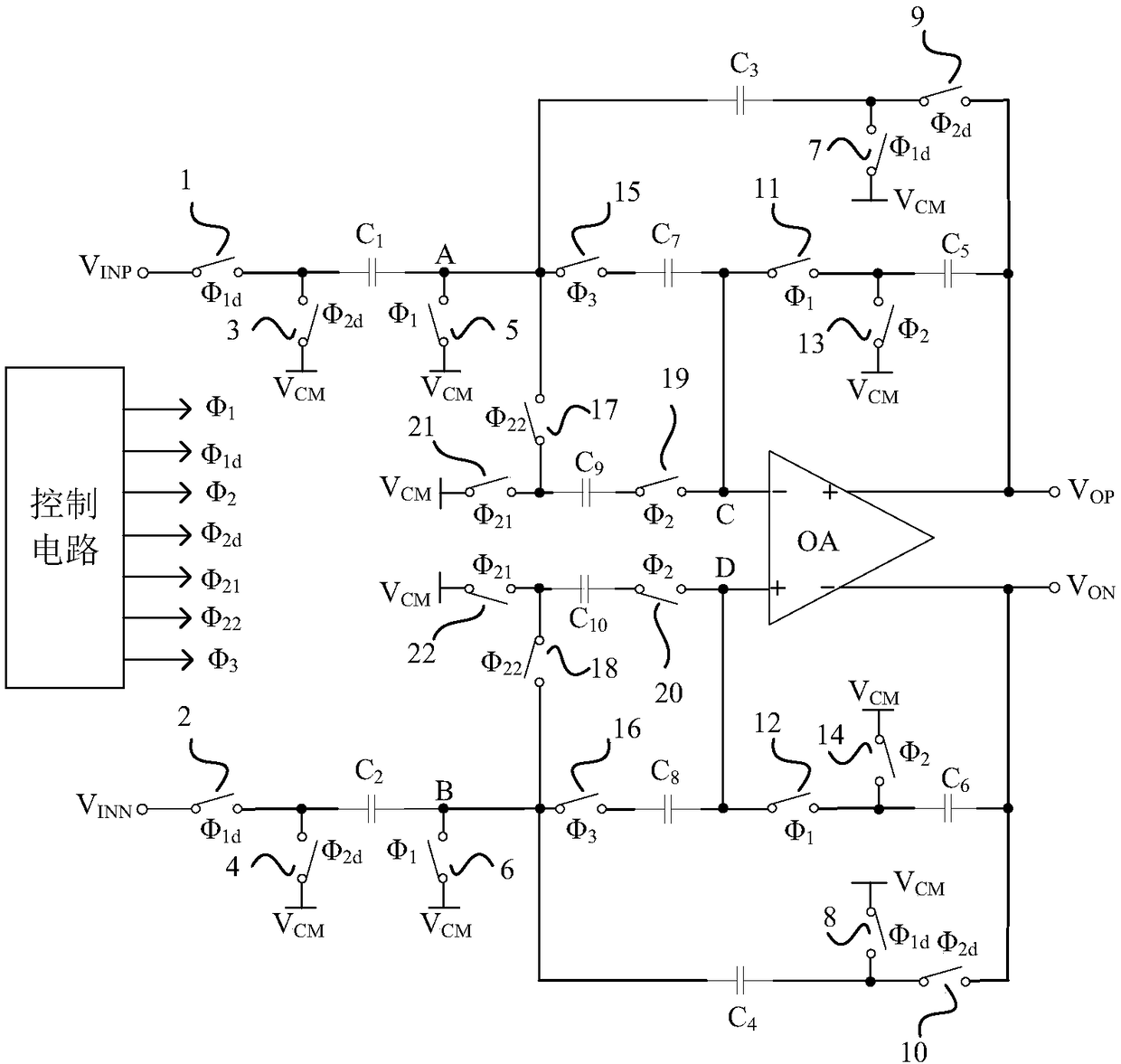

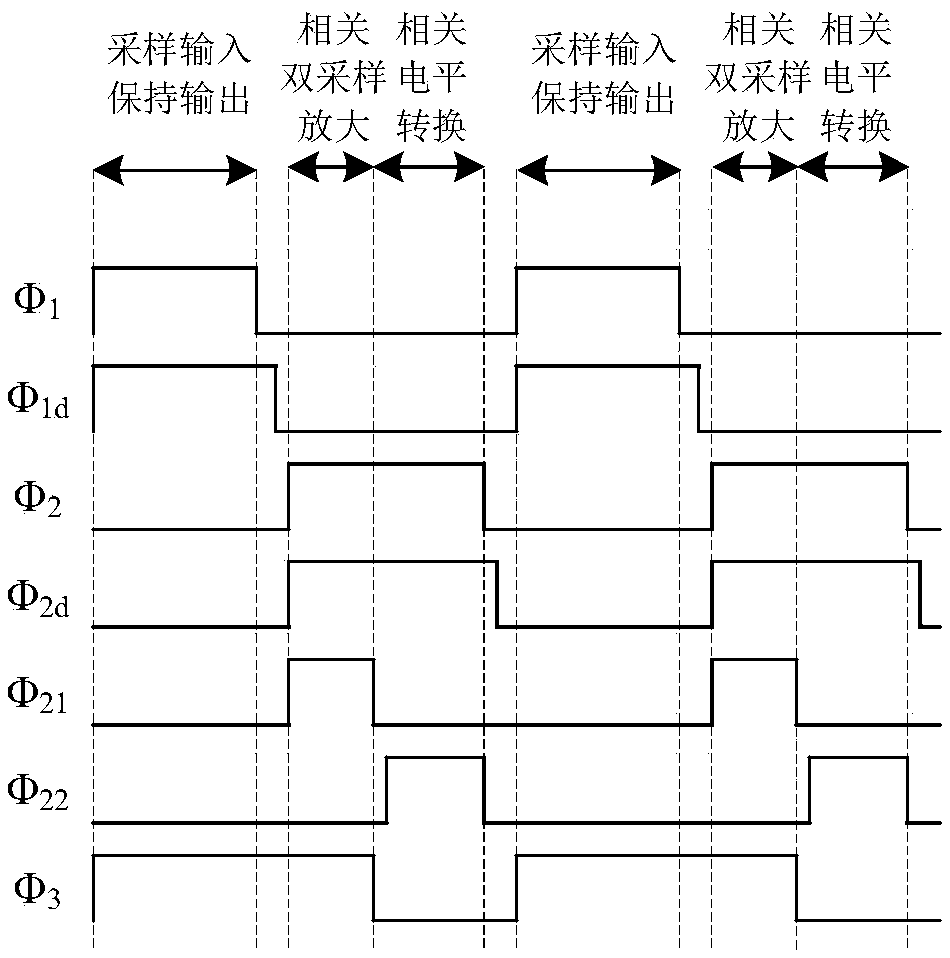

Switched capacitor amplifier capable of offset compensation and finite gain compensation

PendingCN108322192AHigh gain accuracyResidue reductionAmplifier modifications to reduce temperature/voltage variationDifferential amplifiersCapacitanceCharge injection

The invention discloses a switched capacitor amplifier capable of offset compensation and finite gain compensation. The switched capacitor amplifier comprises a correlated double sampling finite gaincompensation branch, an offset voltage storage branch, a correlated level switch branch, a fully-differential operation OA, and a control circuit. The switched capacitor amplifier provided by the invention has the advantages that through the correlated double sampling technology and the input correlated level switch technology, charges remained on an input capacitor and charge transfer errors caused by finite gains of operation are reduced, so that an output DC offset voltage is reduced and higher gain precision of the amplifier is achieved; and the switched capacitor amplifier adopts a fully-differential structure to eliminate charge injection and clock feedthrough, and achieves a small DC offset voltage, high gain precision, etc.

Owner:SHENZHEN INSTITUTE OF INFORMATION TECHNOLOGY

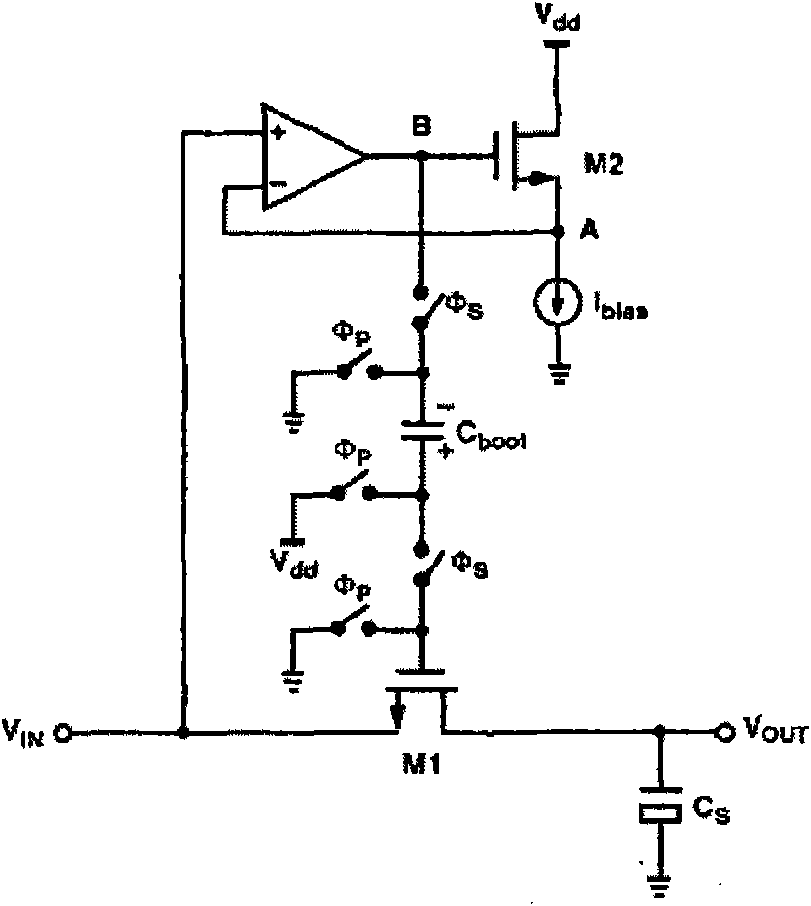

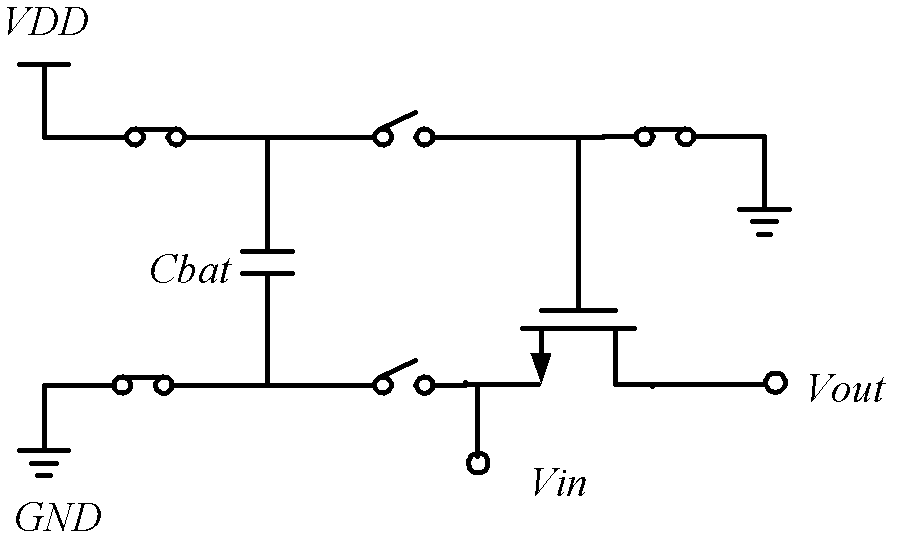

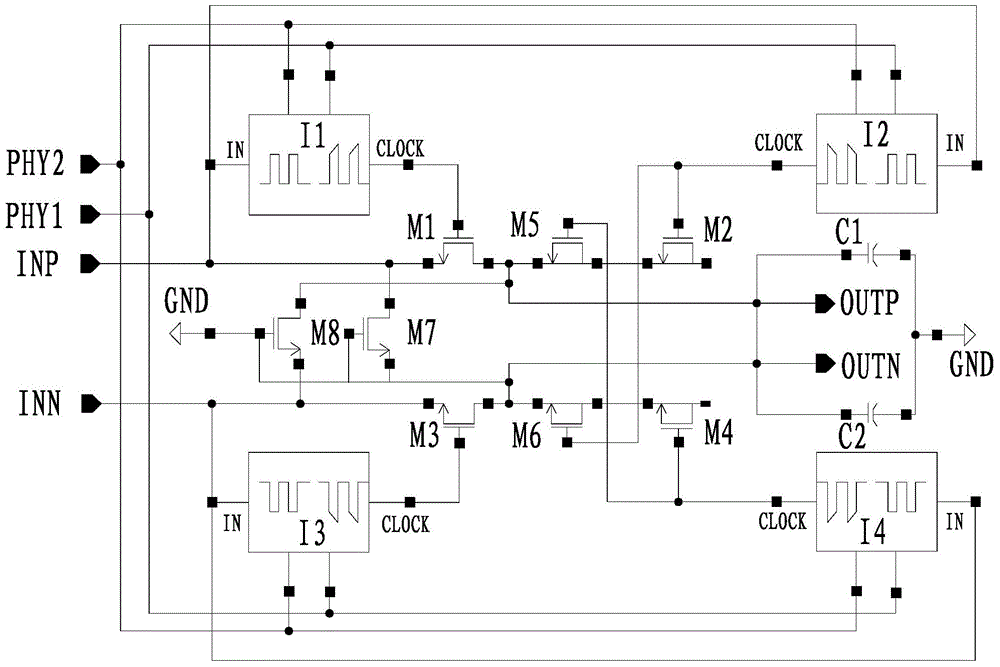

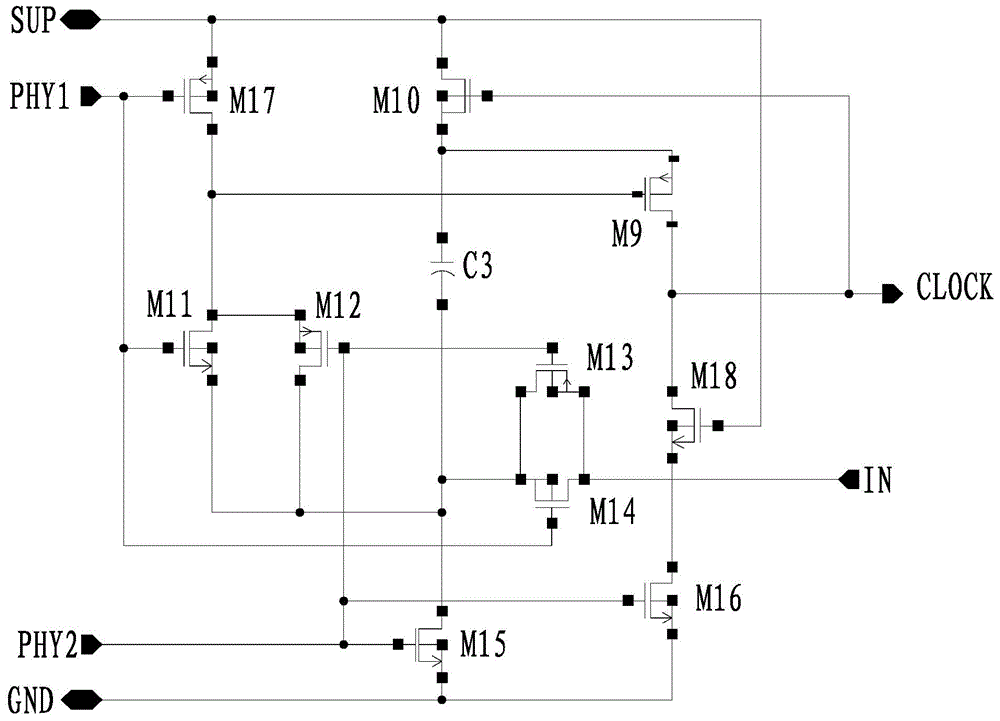

Clock-feedthrough compensation method of bootstrap clock sampling switch and circuit

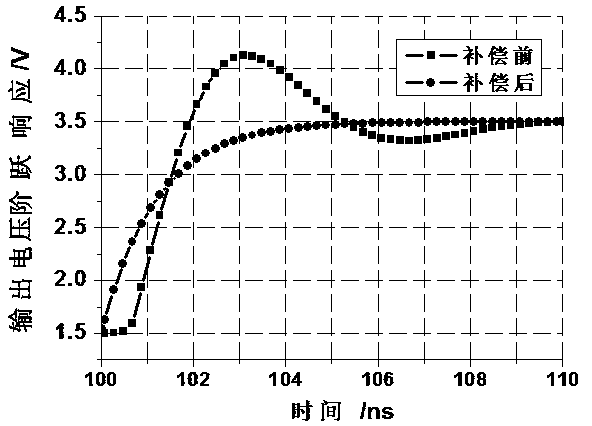

ActiveCN103825616ACrosstalk CancellationSampled value is constantAnalogue/digital conversionElectric signal transmission systemsCapacitanceEngineering

The invention provides a clock-feedthrough compensation method of a bootstrap clock sampling switch. New pseudo switches are added at sampling output nodes, the grid electrodes of the new pseudo switches are biased at the clock output end of a complementary grid voltage bootstrap circuit, error amount generated when the newly-added pseudo switches and the original pseudo switches are coupled onto Vout via Cgd can be mutually offset. The invention provides a clock-feedthrough compensation circuit of the bootstrap clock sampling switch which is designed by the above method. Preferably, a group of pseudo switches in a switching off state is introduced, in the sample and hold stage, the complementary input signals are coupled on Vout respectively via a parasitic Cds capacitor, and cross talk can be mutually offset as the input signals are complementary. The clock-feedthrough compensation circuit of the bootstrap clock sampling switch has the advantages of reducing the influences of the clock-feedthrough effect on signal sampling, improving linearity of a sampling field effect tube, reducing harmonic distortion of the sampling circuit, and improving the sampling speed and the sampling precision.

Owner:XIAMEN UX HIGH SPEED IC

Switched capacitor circuit capable of eliminating clock feedthrough for vco

InactiveCN1574640AEliminate punch-through effectAvoid frequencyComputing operations for integration/differentiationPulse automatic controlCapacitanceControl signal

Owner:MEDIATEK INC +1

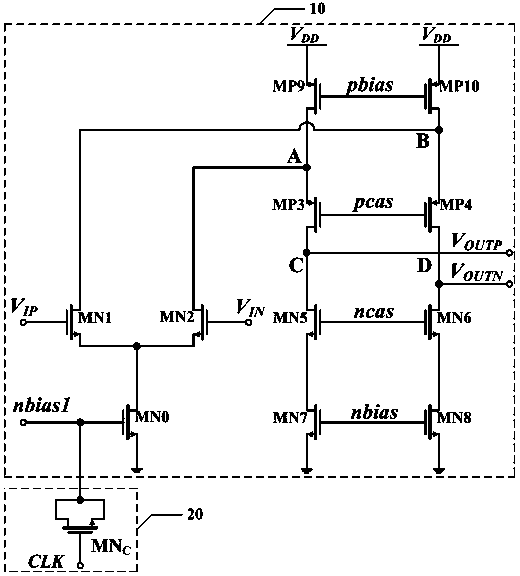

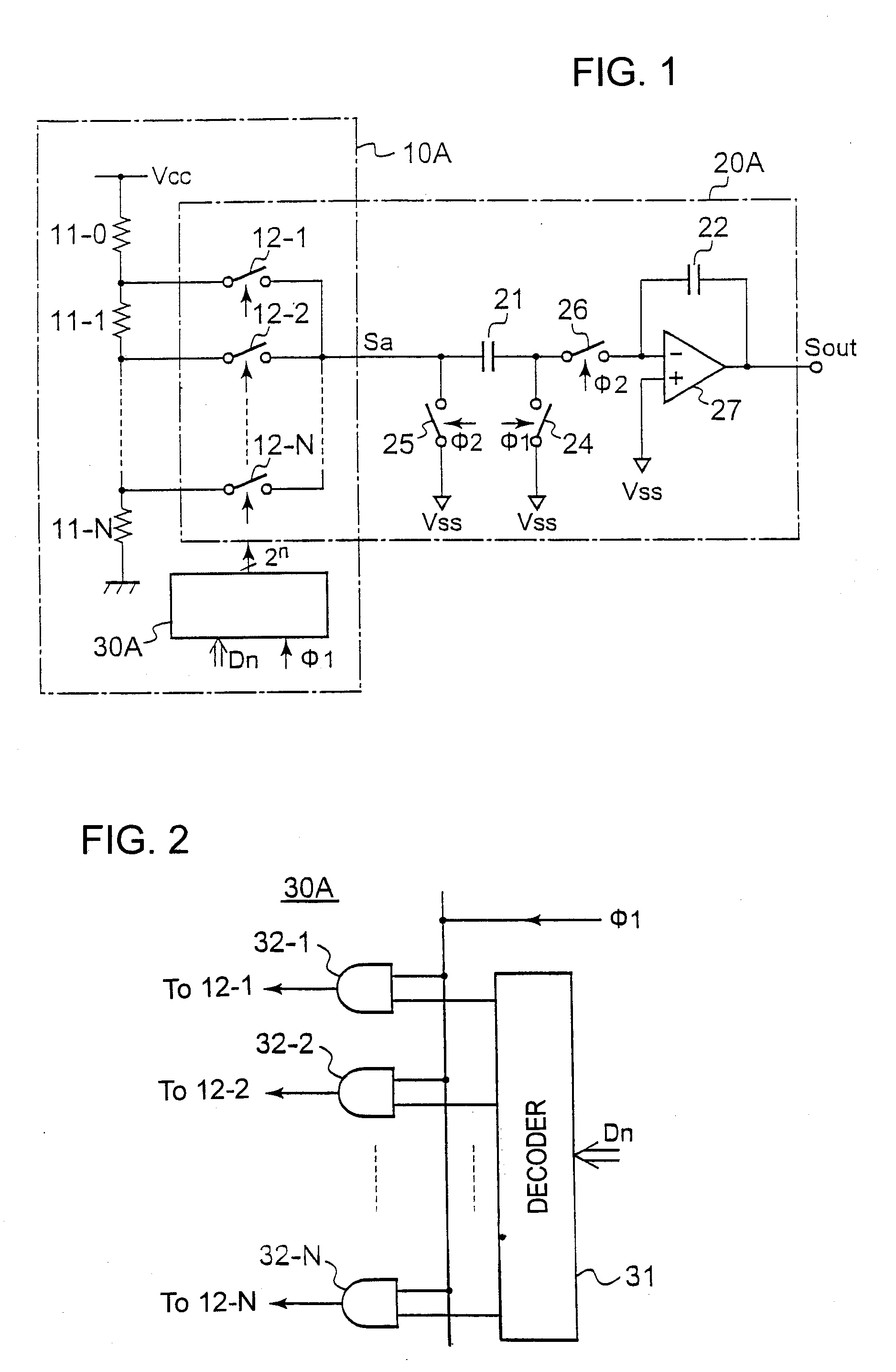

Fully differential operational amplifier modular circuit, analog-to-digital converter and readout integrated circuit

InactiveCN104253590AGood frequency compensationGood step responseAnalogue-digital convertersDifferential amplifiersCapacitanceConverters

An embodiment of the invention discloses a fully differential operational amplifier modular circuit which comprises a folded-cascade fully differential operational amplifier and a clock feed-through frequency compensation circuit. The clock feed-through frequency compensation circuit comprises a capacitive element. One end of the capacitive element is connected to a bias voltage input end of the folded-cascade fully differential operational amplifier, and the other end of the capacitive element is connected to clock signals CLK. The clock signals CLK are inputted to the bias voltage input end in a feed-through manner via the capacitive element, so that voltages at the bias voltage input end nbias1 can be changed. The fully differential operational amplifier modular circuit in the embodiment of the invention has the advantages that the fully differential operational amplifier modular circuit is additionally provided with the clock feed-through frequency compensation circuit with the capacitive element and control clock signals CLK and accordingly is good in step response and stable in setup time, and excellent frequency compensation effects can be realized for the fully differential operational amplifier.

Owner:UNIV OF ELECTRONICS SCI & TECH OF CHINA

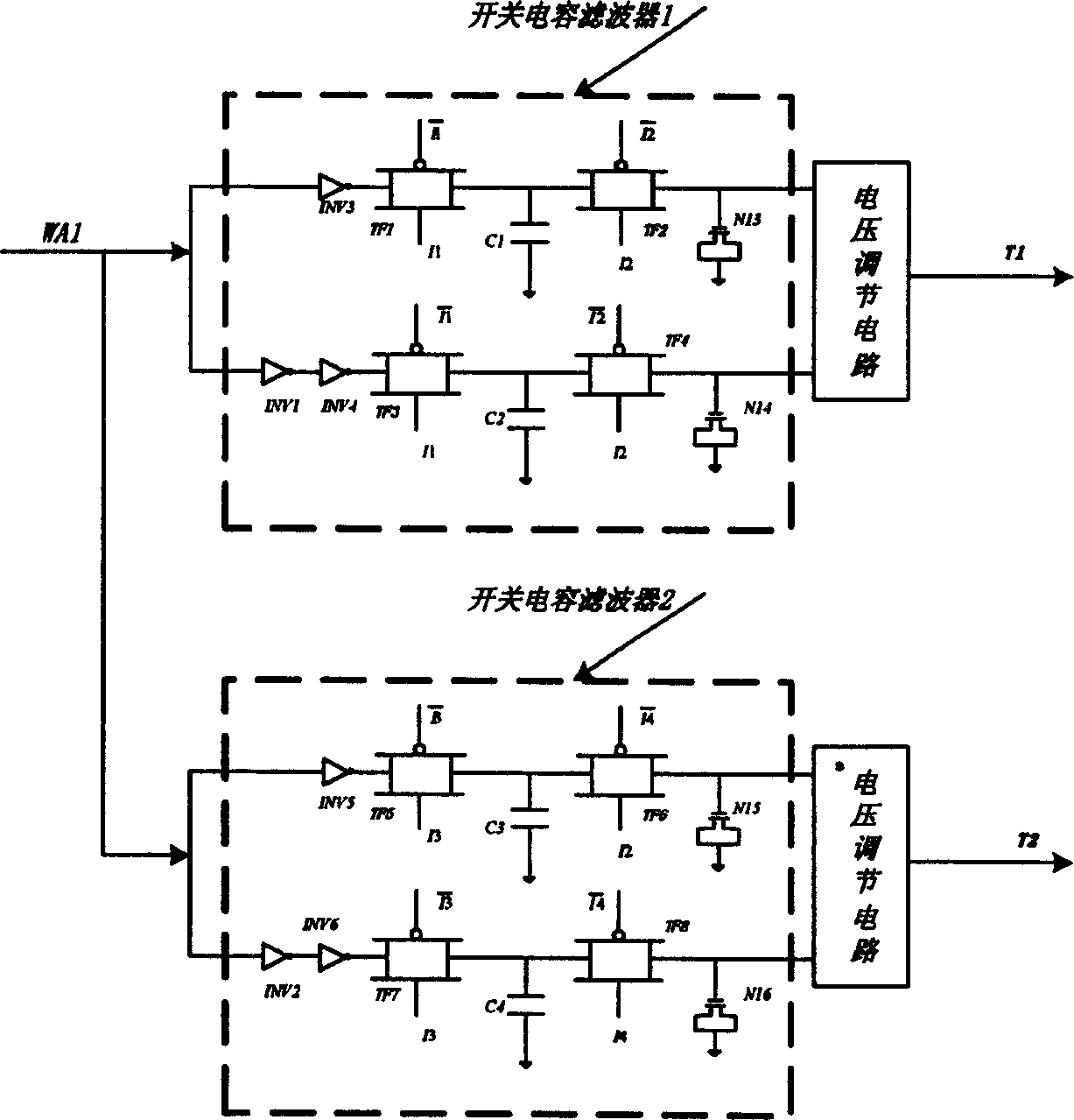

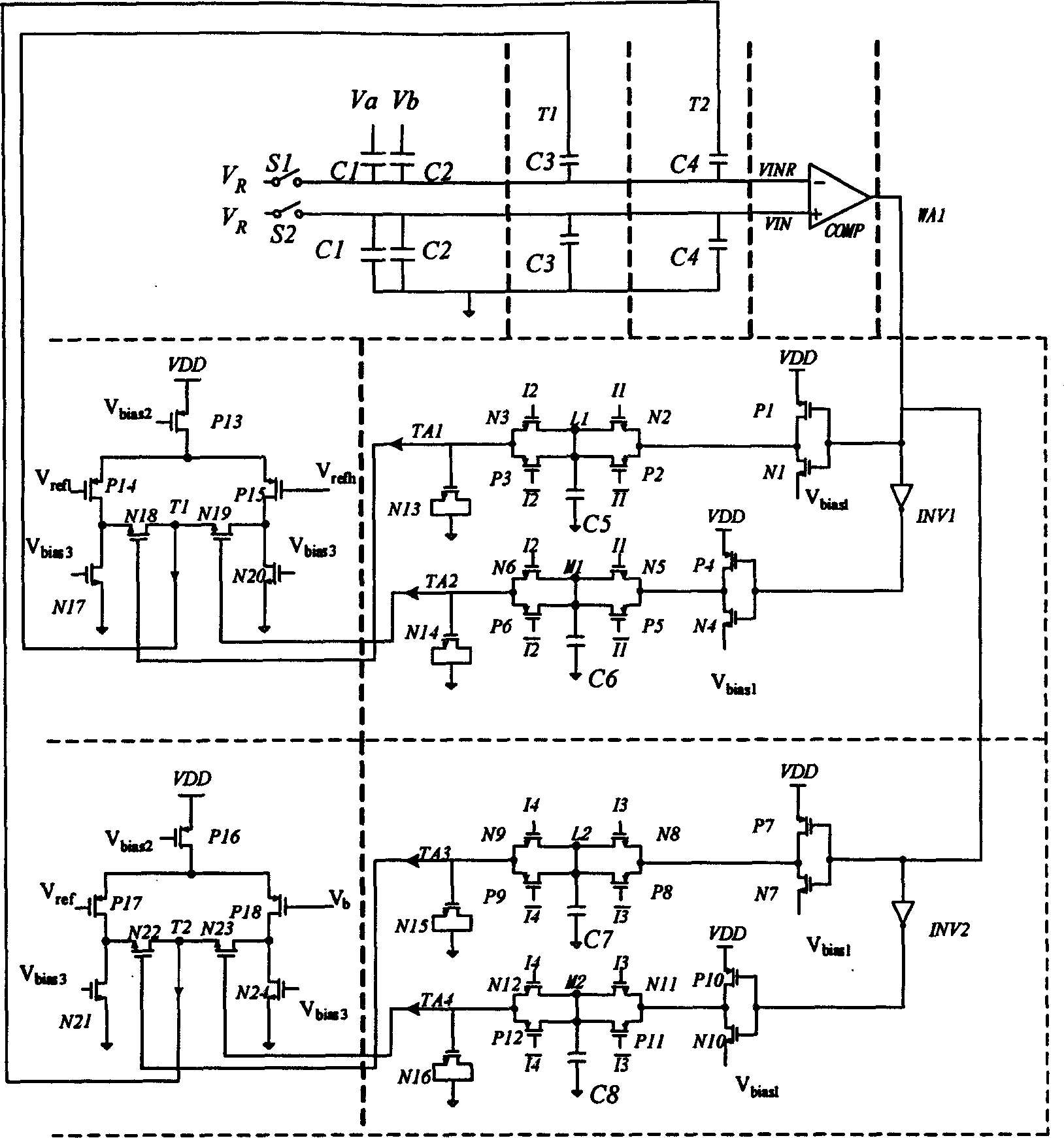

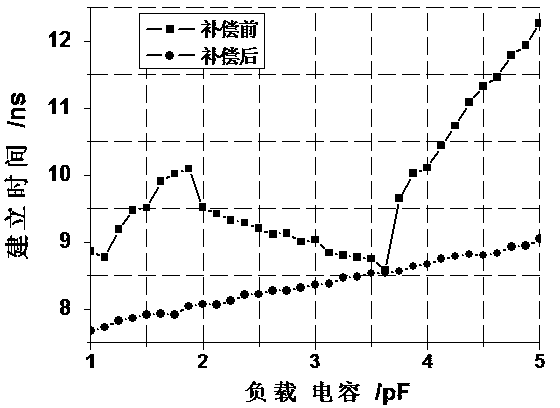

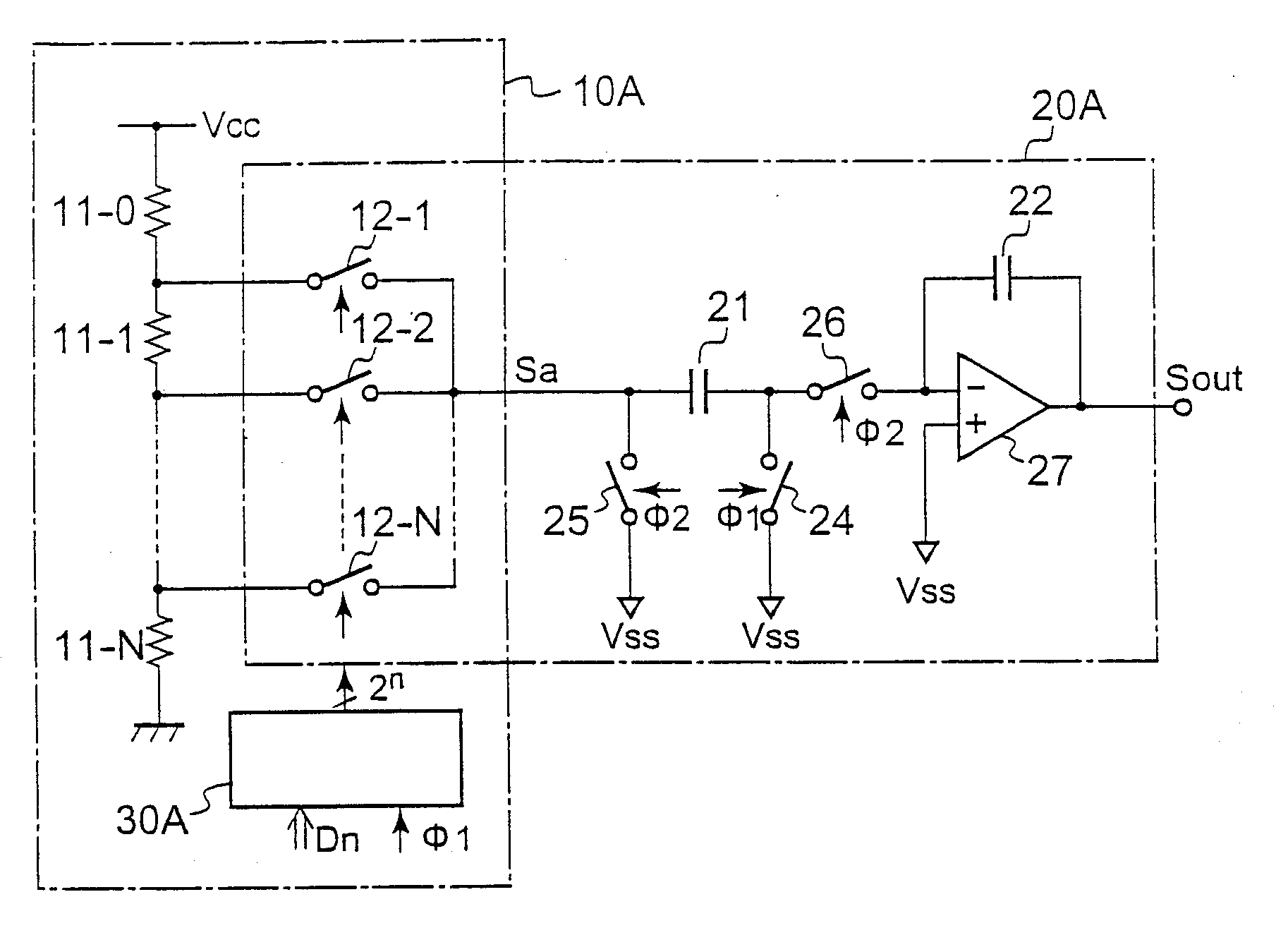

Electronic Circuit and Semiconductor Device Having Dac and Scf

InactiveUS20080316074A1Reduce in quantityReduce switchingElectric signal transmission systemsDelta modulationEngineeringLinearity error

An electronic circuit has a voltage selection and output circuit, e.g. digital-to-analog converter (DAC), and a switched capacitor filter (SCF), in which operational conditions of the input side switches of the SCF are incorporated in the selection conditions for selecting respective multiple selection switches of the voltage selection and output circuit. This arrangement permits the selection switches to serve as the input side switches, thereby reducing in number serial switches such as MOS transistors in the circuit, and hence reducing the on-resistances of the serial switches, while preventing the clock feed-through thereof from increasing and suppressing output errors due to the linearity error of the buffer amplifier involved.

Owner:ROHM CO LTD