Grid electrode driving circuit unit, a grid electrode driving circuit and a display device

A gate drive circuit and drive unit technology, applied in static indicators, static memory, instruments, etc., can solve the problems of large layout area, large circuit power consumption, poor stability, etc., to reduce complexity, improve stability, Effect of Power Consumption Reduction

- Summary

- Abstract

- Description

- Claims

- Application Information

AI Technical Summary

Problems solved by technology

Method used

Image

Examples

Embodiment 1

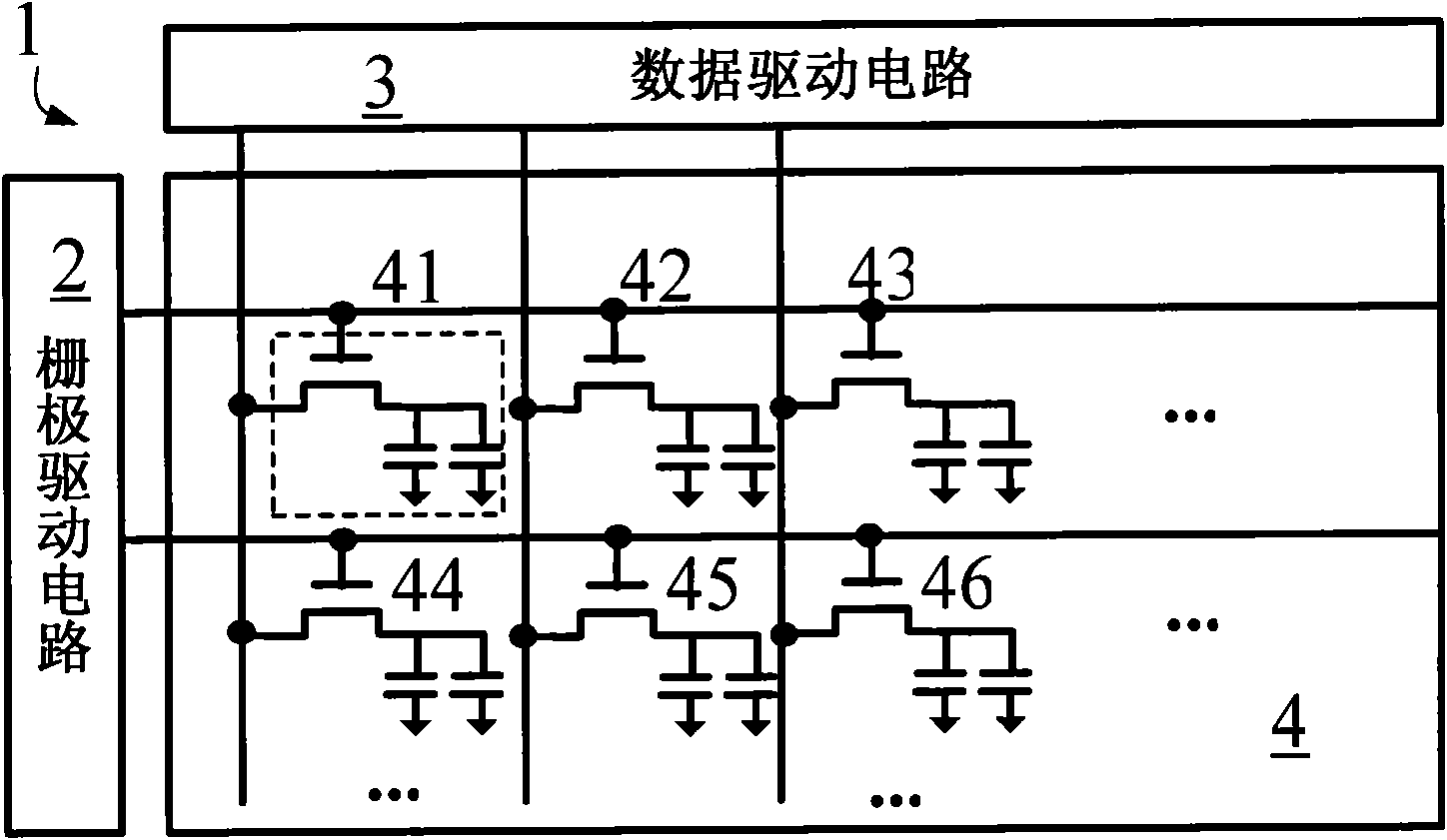

[0033] Such as figure 1 As shown, the display device 1 includes a panel 4 , a data driving circuit 3 and a gate driving circuit 2 . The panel 4 includes a two-dimensional pixel array composed of a plurality of pixels 41, 42, 43, 44, 46, 46, and a plurality of data lines in a first direction (for example, vertical direction) and a second data line connected to each pixel array. A plurality of gate scanning lines in a direction (for example, a horizontal direction). Usually, each gate scanning line corresponds to a row in the pixel array, and each data line corresponds to a column in the pixel array. The data driving circuit 3 is used to output image signals to the data lines; the gate driving circuit 2 is used to output driving signals to the gate scanning lines to complete the row scanning of the pixel array. The gate driving circuit can be connected to the panel by welding or the gate driving circuit can be integrated on the panel. The display device 1 may be a liquid crys...

Embodiment 2

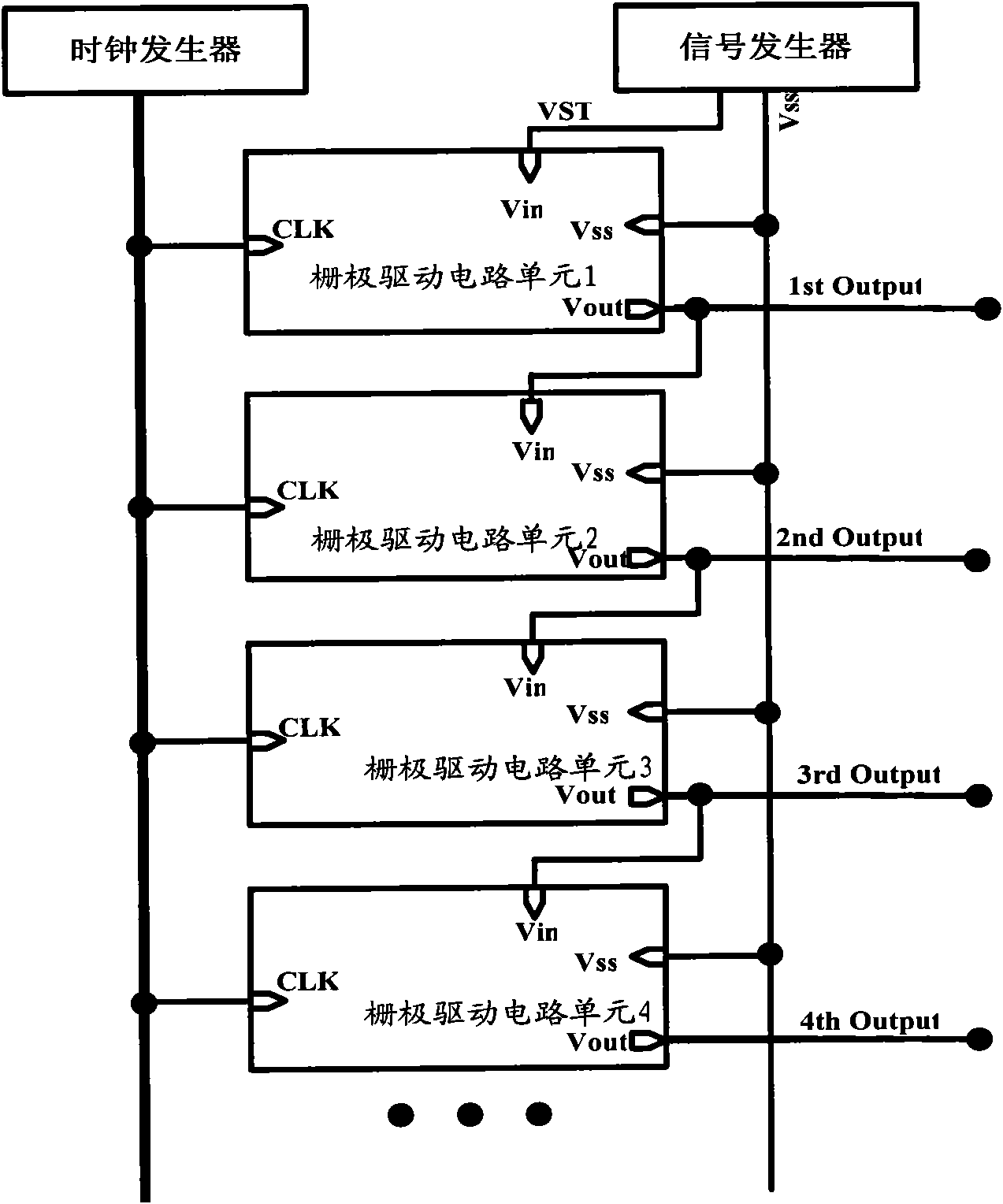

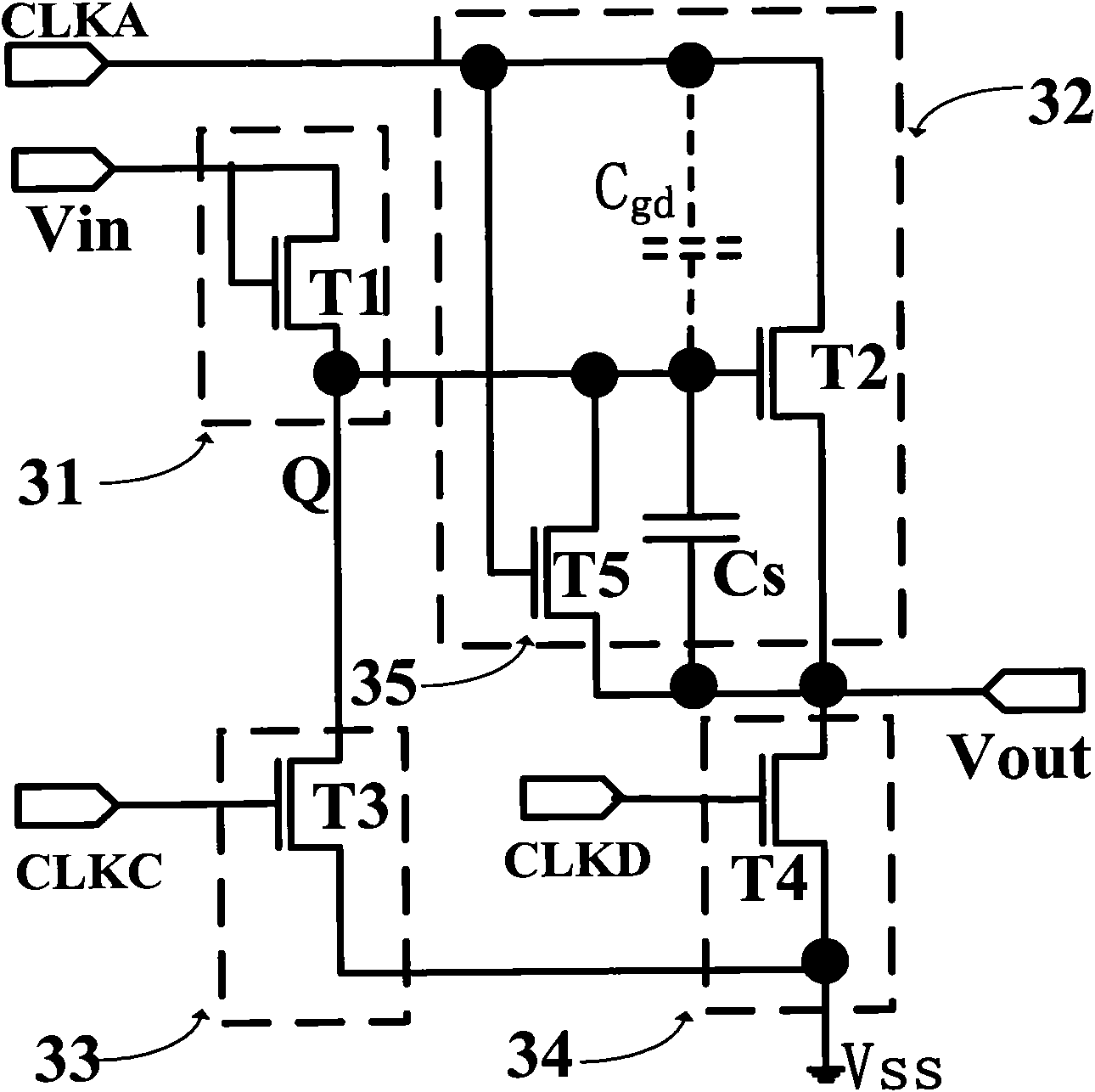

[0090] In another embodiment of the gate drive circuit unit, such as Figure 11 As shown, the gate drive circuit unit signal input interface, signal output interface, input signal control module, first clock signal control module, second clock signal control module, third clock signal control module and fourth clock signal control module. The signal input interface is used to receive the input pulse signal. If the gate drive circuit unit of this stage is the first stage, the input pulse signal is provided by the signal generator. If the gate drive circuit unit of the present stage is not the first stage, the input pulse signal Provided by the previous stage gate drive circuit unit. The signal output interface is used to output the driving signal to the corresponding scanning line and the signal input interface of the gate driving circuit unit of the next stage. The first clock signal control module includes a drive unit and a clock feedthrough suppression unit. The drive unit...

PUM

Login to View More

Login to View More Abstract

Description

Claims

Application Information

Login to View More

Login to View More