Clock-feedthrough compensation method of bootstrap clock sampling switch and circuit

A technology of clock feedthrough and clock sampling, applied in the field of circuits

- Summary

- Abstract

- Description

- Claims

- Application Information

AI Technical Summary

Problems solved by technology

Method used

Image

Examples

Embodiment Construction

[0042] The present invention will be further described below in conjunction with drawings and embodiments.

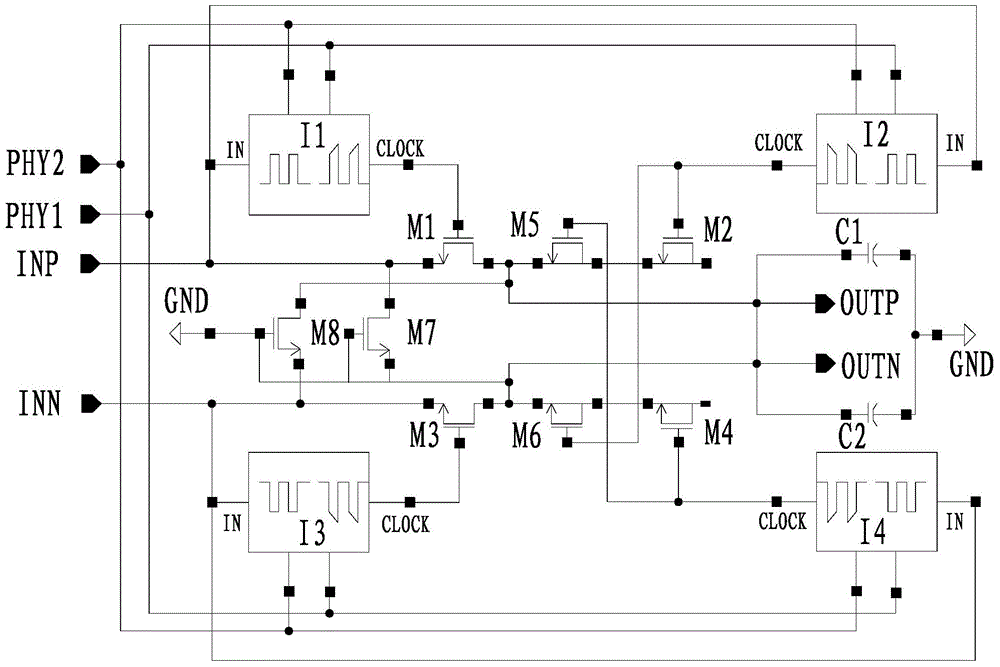

[0043] refer to figure 1 , a clock feedthrough compensation circuit for a bootstrap clock sampling switch, comprising:

[0044]The first sampling transistor M1, the gate of the first sampling transistor M1 is connected to the clock output terminal of the first gate voltage bootstrap circuit I1, the source of the first sampling transistor M1 is connected to the first differential complementary signal INP, The drain of the first sampling transistor M1 is connected to the first output terminal OUTP;

[0045] A first dummy switch transistor M2, the gate of the first dummy switch transistor M2 is connected to the clock output end of the second gate voltage bootstrap circuit I2;

[0046] A first storage capacitor C1, one end of the first storage capacitor C1 is connected to the first output terminal OUTP; the other end of the first storage capacitor C1 is connected to GND; ...

PUM

Login to View More

Login to View More Abstract

Description

Claims

Application Information

Login to View More

Login to View More