Capacity mismatch calibrating device

A capacitance mismatch and calibration device technology, applied in the direction of analog/digital conversion calibration/test, electrical components, electrical signal transmission system, etc., can solve the problems of reducing circuit speed, increasing cost, and unable to eliminate the impact, so as to achieve the goal of increasing speed Effect

- Summary

- Abstract

- Description

- Claims

- Application Information

AI Technical Summary

Problems solved by technology

Method used

Image

Examples

Embodiment Construction

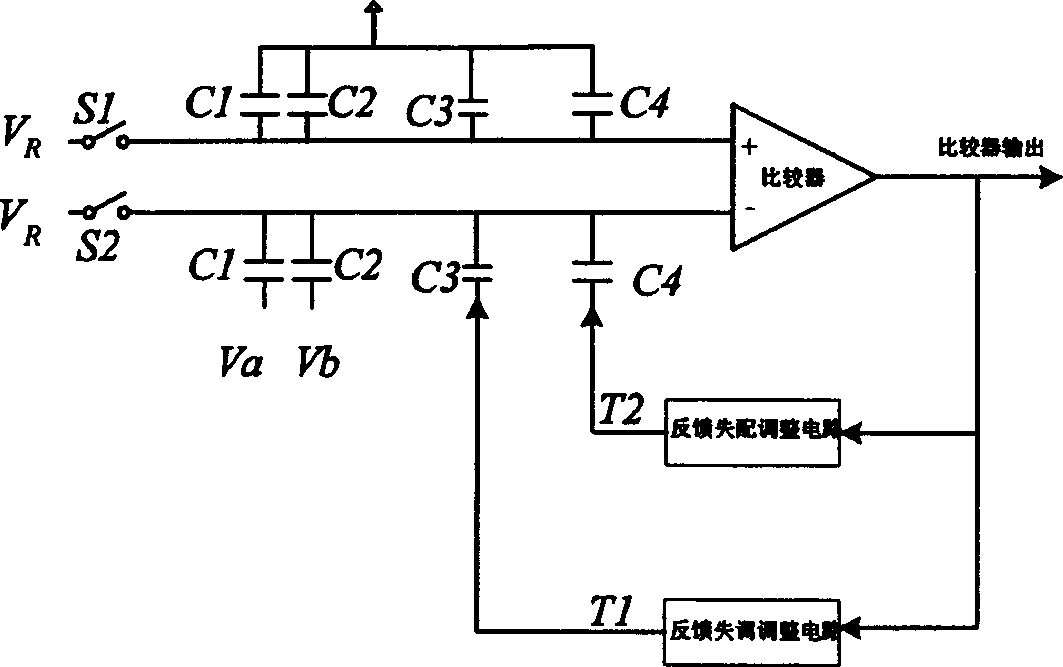

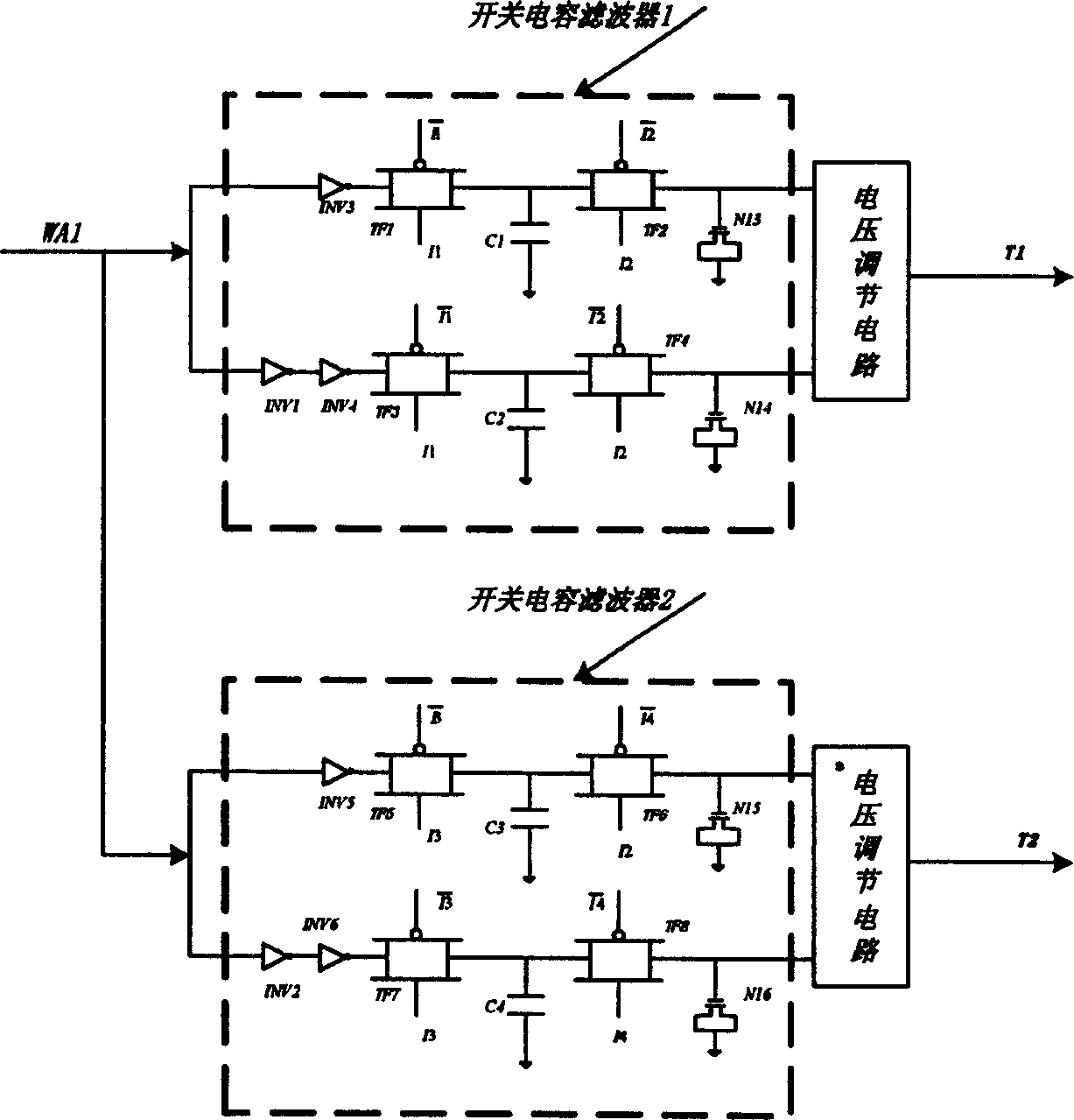

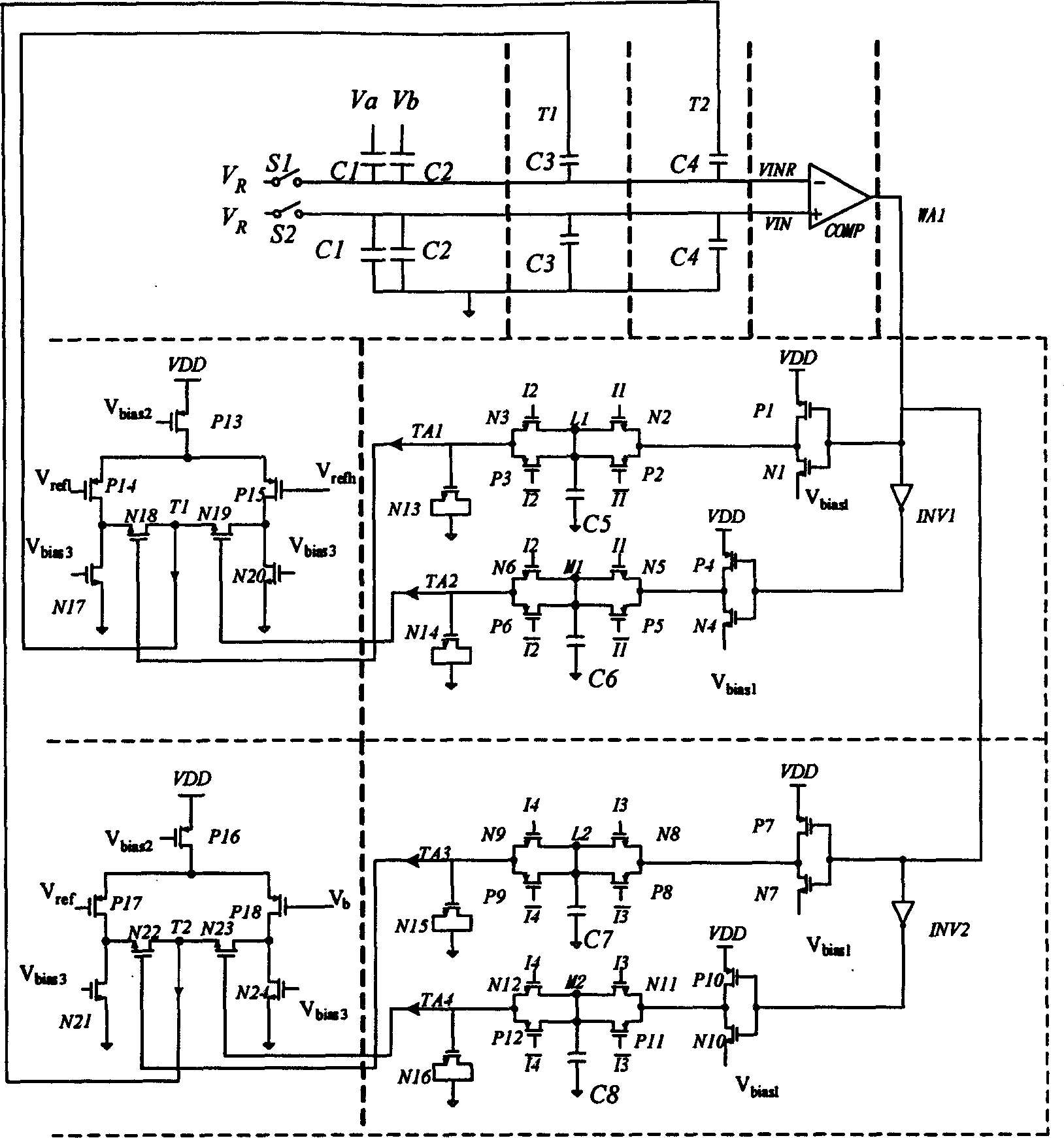

[0012] A capacitor mismatch calibration device capable of matching capacitors, consisting of calibrated capacitors C1 and C2, comparator offset calibration capacitor C3, calibration capacitor C4, and comparator COMP, calibrated capacitors C1 and C2, and comparator offset calibration capacitor C3 One end of the calibration capacitor C4 is connected to the inverting input of the comparator COMP, and the other ends of the calibrated capacitors C1 and C2 are respectively connected to the input voltage V a and V bOne end of the symmetrical capacitance C1' and C2' of the calibrated capacitance C1 and C2, the symmetrical capacitance C3' of the comparator offset calibration capacitance C3, and the symmetrical capacitance C4' of the calibration capacitance C4 are connected to the non-inverting input end of the comparator COMP, and the other One end is grounded, and it is characterized in that a feedback mismatch adjustment circuit and a feedback offset adjustment circuit are respective...

PUM

Login to View More

Login to View More Abstract

Description

Claims

Application Information

Login to View More

Login to View More