Accumulation circuit for floating-point numbers and realization method thereof

An accumulation circuit and floating-point number technology, applied in the field of digital computing, can solve the problem of low performance of floating-point number calculations, achieve the effect of reducing one-level addition operations, reducing one-level XOR operations, and shortening delays

- Summary

- Abstract

- Description

- Claims

- Application Information

AI Technical Summary

Problems solved by technology

Method used

Image

Examples

Embodiment 1

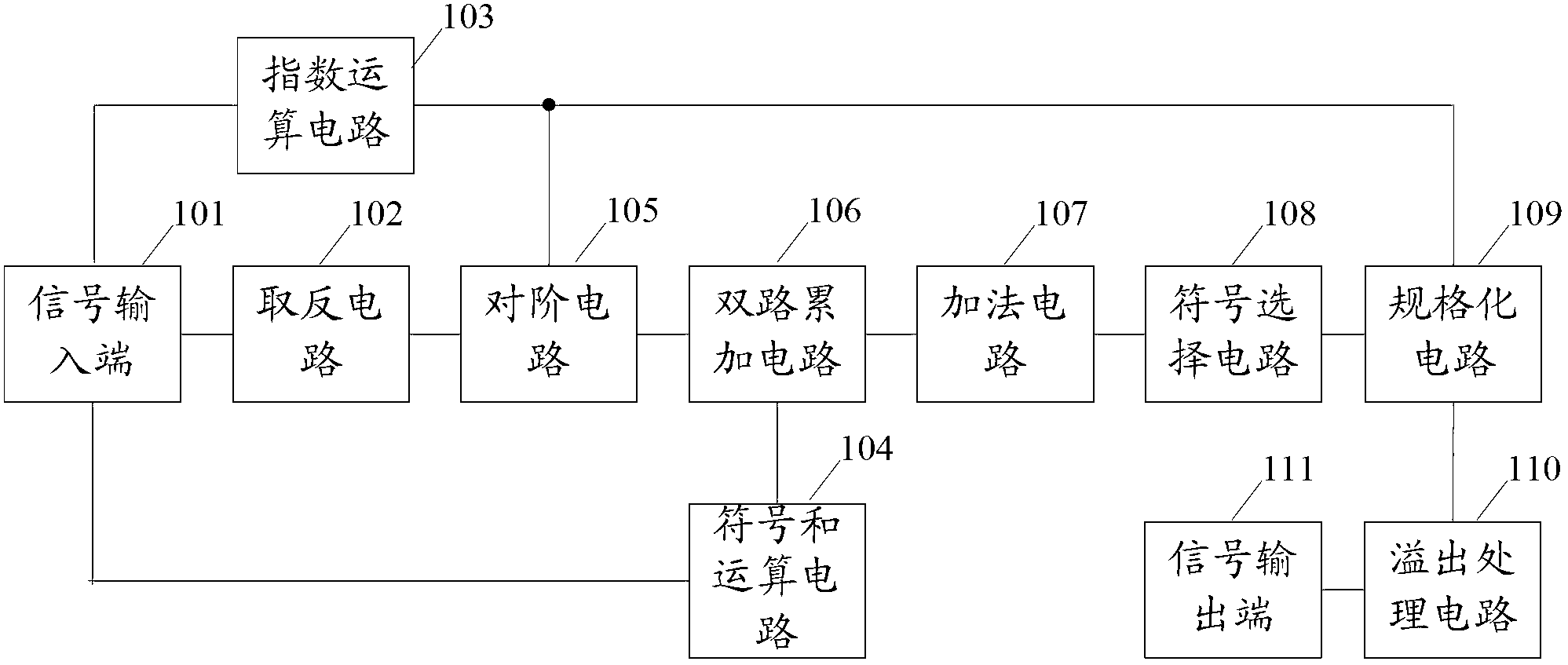

[0039] This embodiment provides a floating-point number accumulation circuit, such as figure 1 As shown, the circuit includes: a signal input terminal 101, an inversion circuit 102, an exponential operation circuit 103, a sign sum operation circuit 104, an order matching circuit 105, a two-way accumulation circuit 106, an addition circuit 107, a sign selection circuit 108, specifications circuit 109, overflow processing circuit 110 and signal output terminal 111, wherein,

[0040] The signal input terminal 101 is used to obtain a first floating-point number signal and a second floating-point number signal;

[0041] The inversion circuit 102 is used for inverting the first floating-point number signal and the second floating-point number signal;

[0042] The exponent operation circuit 103 is used to obtain a first power exponent according to the first floating-point number signal, obtain a second power exponent according to the second floating-point number signal, and obtain a...

Embodiment 2

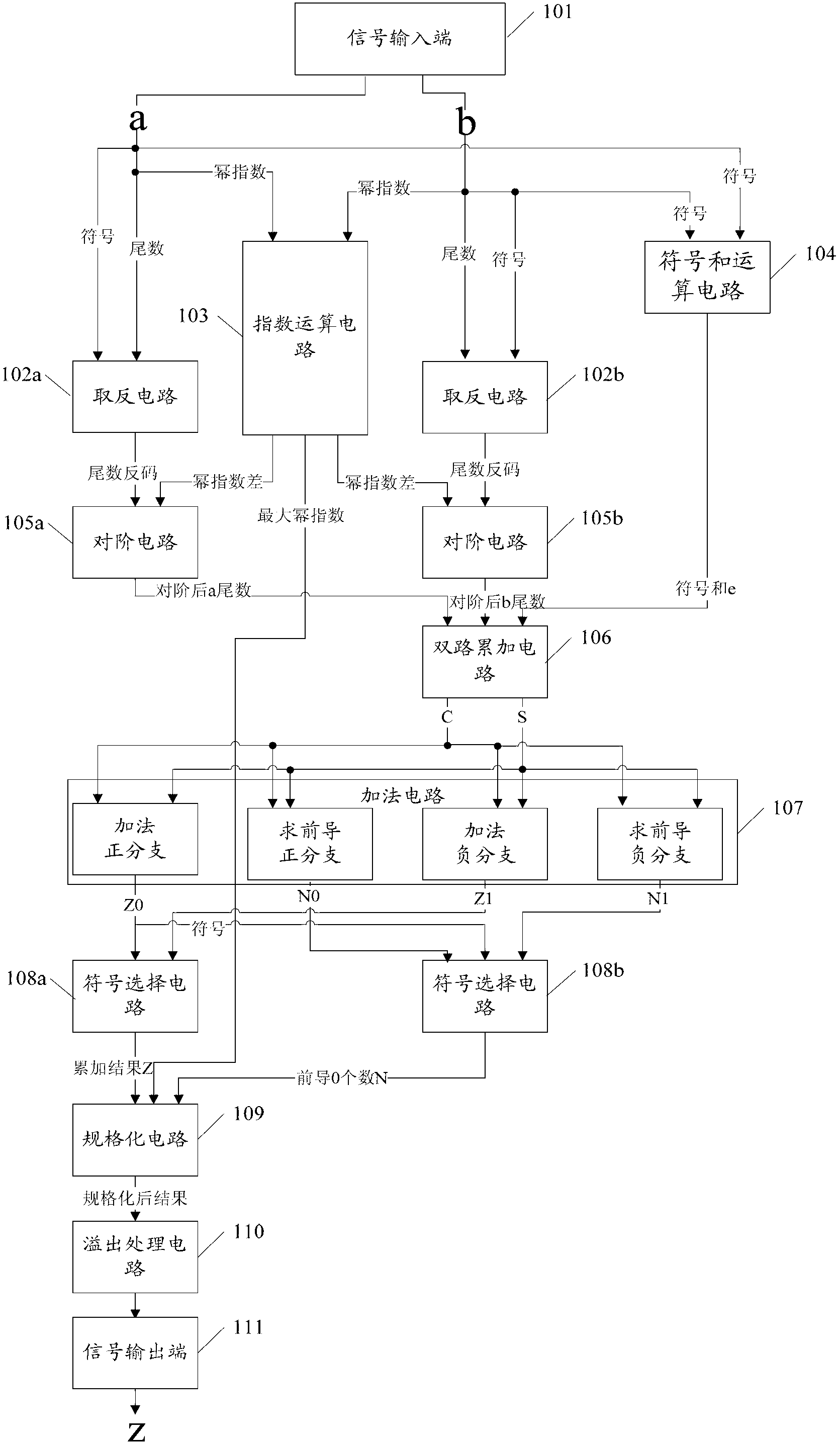

[0054] This embodiment provides a floating-point number accumulation circuit, which inputs a floating-point number signal a and a floating-point number signal b from a signal input terminal, and outputs an accumulation result z at a signal output terminal, where z=a+b, such as figure 2 As shown, the circuit includes: a signal input terminal 101, an inversion circuit 102a, an inversion circuit 102b, an exponent operation circuit 103, a sign sum operation circuit 104, an order-to-order circuit 105a, an order-to-order circuit 105b, a two-way accumulation circuit 106, Adding circuit 107, symbol selection circuit 108a, symbol selection circuit 108b, normalization circuit 109, overflow processing circuit 110 and signal output terminal 111, wherein,

[0055] The signal input terminal 101 is used to obtain two floating-point number signals a and b.

[0056] Wherein, the floating-point number signal a may be a floating-point number signal or a sum signal of at least two floating-point...

Embodiment 3

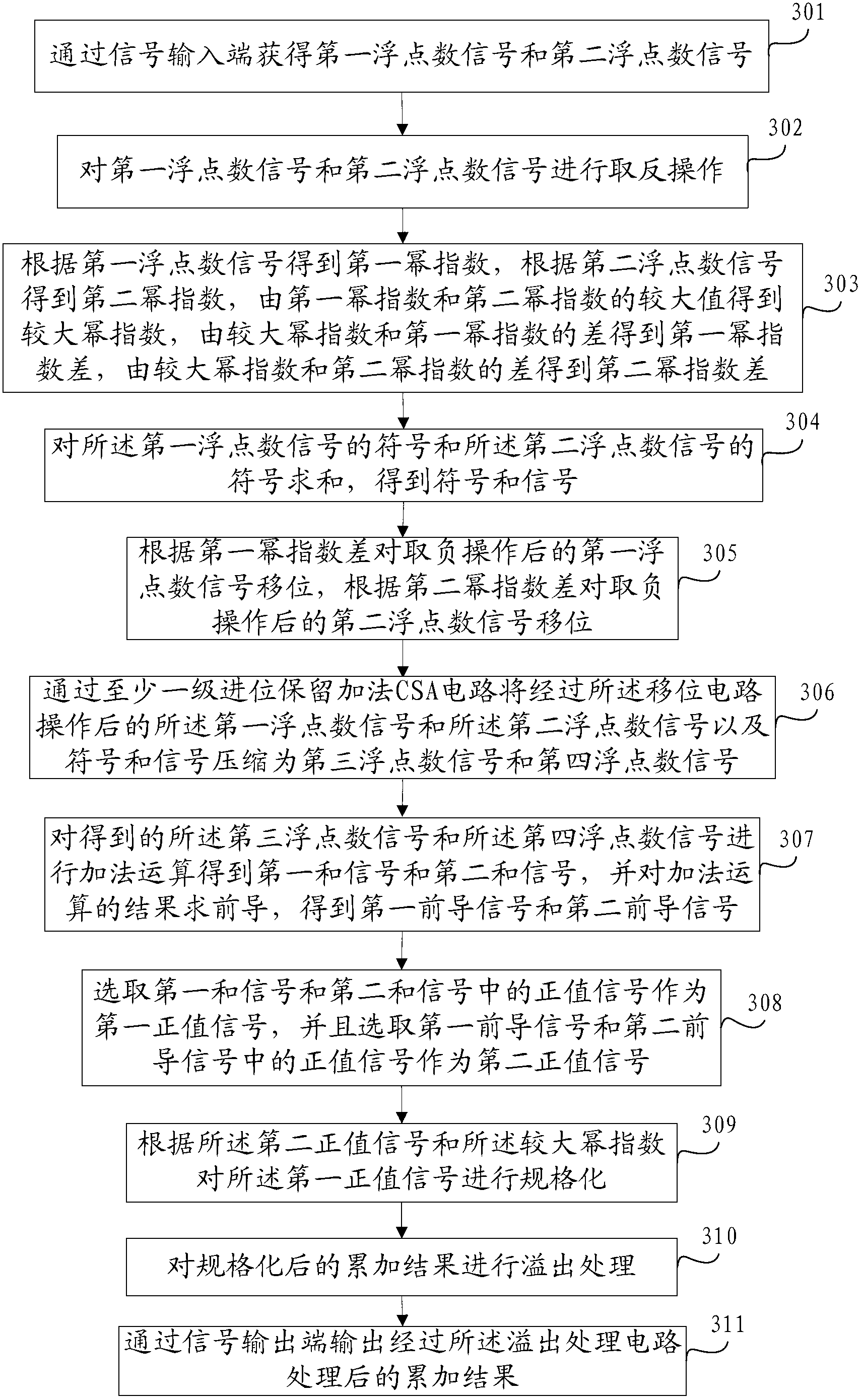

[0075] This embodiment provides a method for implementing a floating-point number accumulation circuit, such as image 3 As shown, the method includes:

[0076] 301. Obtain a first floating-point number signal and a second floating-point number signal through a signal input terminal.

[0077] For example, the obtained floating-point signal can be two floating-point signal a and floating-point signal b, the output accumulation result is Z, and the operation process can be: Z=a+b, where b can be the product of multiple floating-point signals Signals, such as b=c×d, a can be the sum signal of multiple floating-point number signals, and this addition form is extended to general floating-point number operations:

[0078] where a i 、c j and d j Both are floating point signals, b j =c j × d j , i=0, 1, ..., n-1, j = 0, 1, ..., m-1, as long as from a i and b j In any group or two groups, two or more floating-point number signals can be combined, that is, n≥0, m≥0, and n+m≥2. ...

PUM

Login to View More

Login to View More Abstract

Description

Claims

Application Information

Login to View More

Login to View More