Multilayer package substrate and package

A technology for packaging substrates and packages, which is applied to electrical components, electrical solid-state devices, semiconductor devices, etc., can solve the problems of reducing manufacturability, warping of packaging substrates, etc., and achieve the effect of improving electrical performance

- Summary

- Abstract

- Description

- Claims

- Application Information

AI Technical Summary

Problems solved by technology

Method used

Image

Examples

Embodiment Construction

[0024] In order to make the content of the present invention clearer and easier to understand, the content of the present invention will be described in detail below in conjunction with specific embodiments and accompanying drawings.

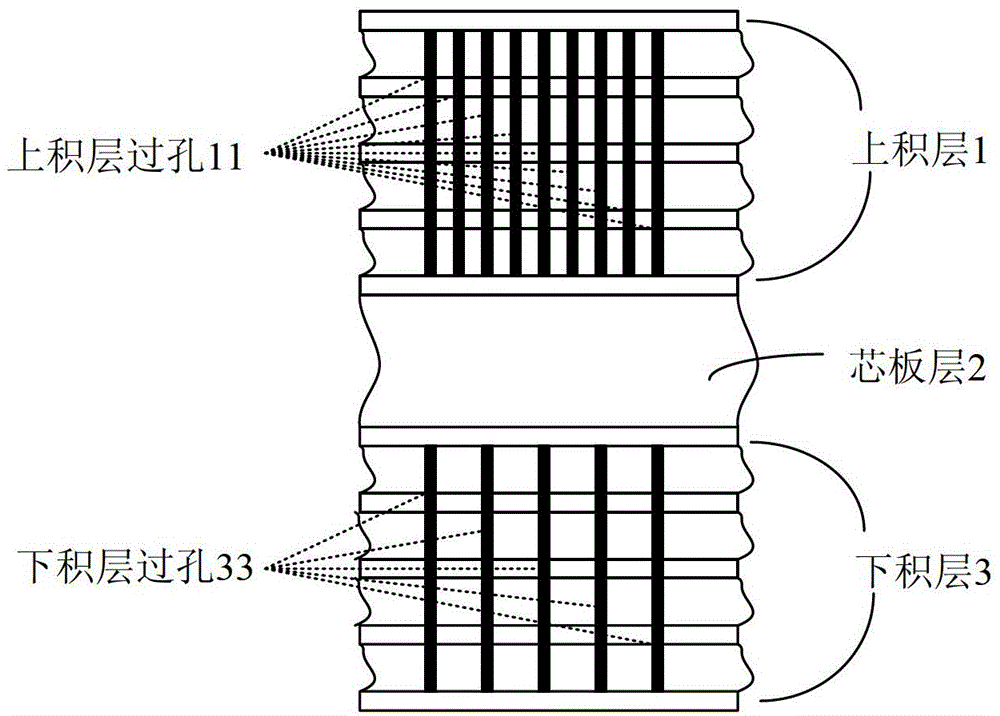

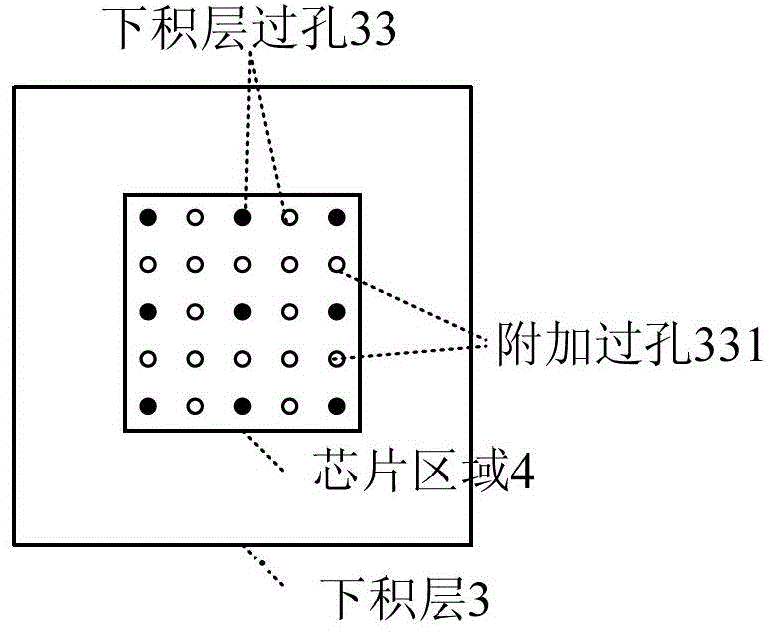

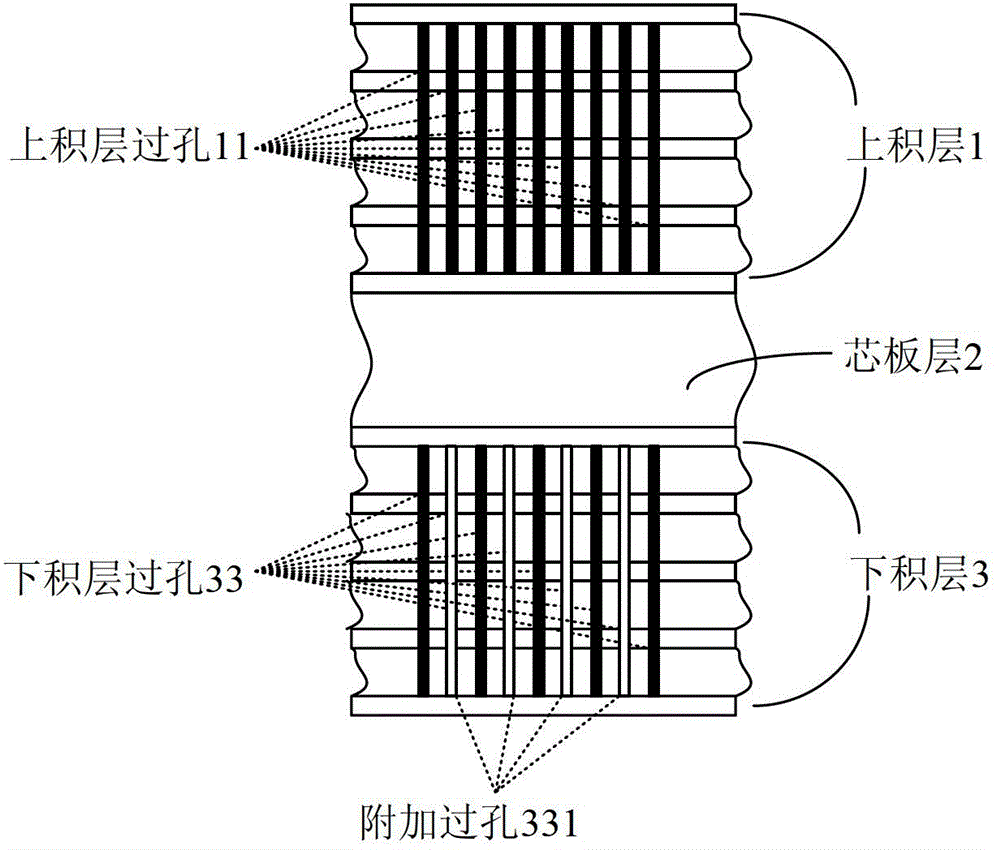

[0025] The pitch of the chip pins on the top layer of the multilayer packaging substrate is much smaller than that of the bottom layer of the packaging substrate, so the density of the via holes 11 in the upper buildup layer 1 of the multilayer packaging substrate is much greater than that of the lower buildup layer 3 . The density of the build-up vias 33 and the unbalanced via distribution between the upper build-up layer 1 and the lower build-up layer 3 easily lead to warping of the packaging substrate, thereby reducing the manufacturability of the high-density multilayer packaging substrate. Therefore, in the embodiment of the present invention, the chip area of the lower build-up layer 3 of the multi-layer packaging substrate can be effecti...

PUM

Login to View More

Login to View More Abstract

Description

Claims

Application Information

Login to View More

Login to View More