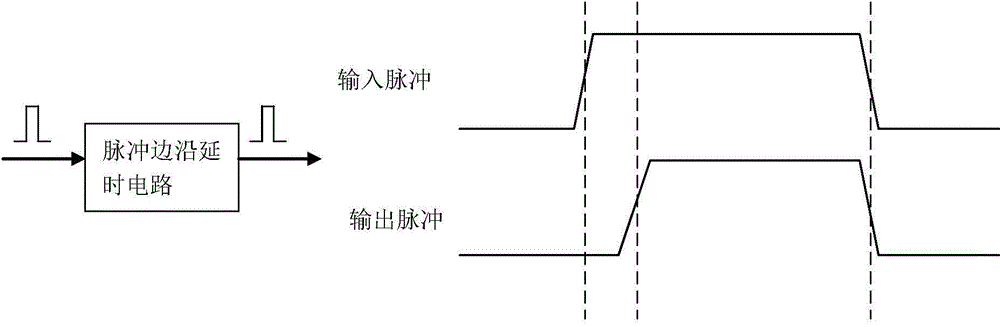

Pulse signal unilateral edge time delay circuit

A pulse signal, one-sided technology, applied in pulse processing, pulse technology, electrical components, etc., can solve problems such as poor digital signal integrity, achieve good digital integrity, reduce power output capability requirements, and realize pulse single-sided edge delay when the effect

- Summary

- Abstract

- Description

- Claims

- Application Information

AI Technical Summary

Problems solved by technology

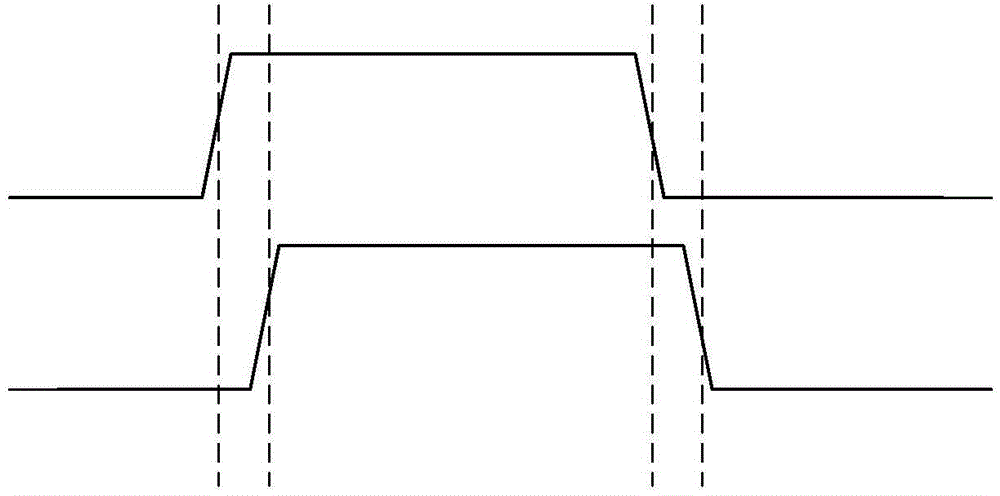

Method used

Image

Examples

Embodiment Construction

[0024] Preferred embodiments of the invention will now be described in more detail with reference to the accompanying drawings, in which preferred embodiments of the invention are shown. However, the present invention may be embodied in various forms and should not be construed as limited to the embodiments set forth herein. Rather, these embodiments are provided so that this disclosure will be thorough and complete, and will fully convey the scope of the invention to those skilled in the art.

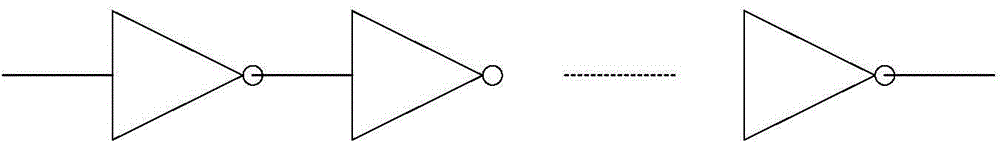

[0025] Image 6 The circuit schematic diagram of the existing constant current source pulse delay circuit is shown. according to Image 6 , the circuit includes: first stage inverter U2, second stage inverter U3, a pair of switches MP1 and MN1, constant current source I0, capacitor C0, third switch MN2, fourth switch MP0, voltage comparator U0 and inverter U1, where

[0026] After the input pulse IN passes through the first-stage inverter U2 to obtain the inversion signal inn, it t...

PUM

Login to View More

Login to View More Abstract

Description

Claims

Application Information

Login to View More

Login to View More