A Charge Compensation Circuit and Memory Structure for Reducing Read Operation Voltage Jitter

A charge compensation and voltage jitter technology, applied in the field of memory, can solve the problems of increasing the response speed and driving capacity of the charge pump, difficult to fully recover the VPP voltage, and increasing the VPP ripple, so as to reduce the output capacity requirements and reduce power consumption. , the effect of reducing the area

- Summary

- Abstract

- Description

- Claims

- Application Information

AI Technical Summary

Problems solved by technology

Method used

Image

Examples

Embodiment 1

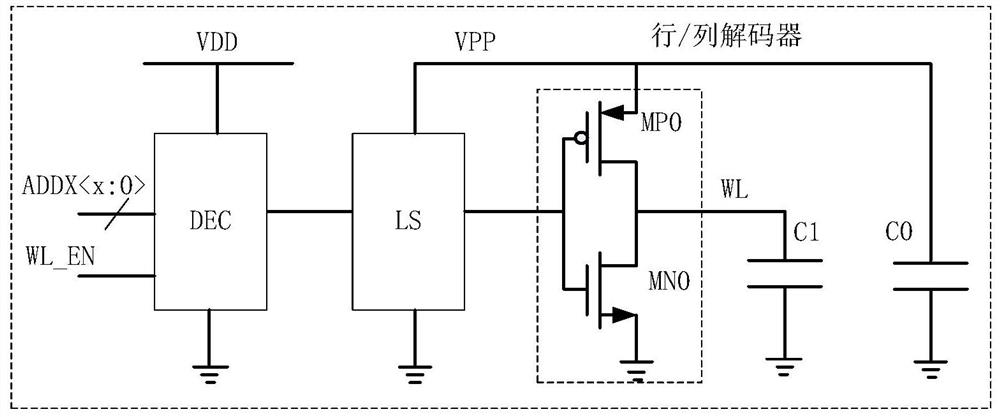

[0022] A charge compensation circuit that reduces voltage jitter in read operations, such as Figure 4 As shown, it is mainly driven by the compensation output of the front end connected to the WL_EN / BL_EN signal (MP1, MN1 is the equivalent drive of the compensation voltage) and the compensation capacitor CX / CY / CY connected to the compensation output drive at the front end and connected to the read voltage VPP at the rear end constitute.

[0023] The compensation output driver outputs a compensation voltage VX / VY, and charges the compensation capacitor CX / CY, thereby compensating the read voltage VPP; VDD provides a high voltage for the compensation output driver.

[0024] Take the row decoding enable signal as an example, when the WL_EN signal is switched from 0 to 1, WL is pulled from 0 to VPP, and the amount of charge extracted by C1 from VPP is C1*VPP; at the same time, CX is connected to the pole on the side of the compensation output drive The plate is pulled up from 0 ...

Embodiment 2

[0029] Considering that there is a certain ripple in VDD, in order to avoid the impact of VDD ripple on VPP during read operation, CX / CY can be disconnected from VDD after performing charge compensation on VPP.

[0030] Therefore, on the basis of Embodiment 1, the front end of the compensation output driver is connected with a gating control circuit, so that the compensation output driver only outputs compensation voltage when WL_EN / BL_EN=1 and SENSE=0.

[0031] The gating control circuit is composed of a gating control signal, a single-stage reverse circuit, and a NAND gate circuit, such as Figure 5 As shown, the gate control signal adopts but is not limited to the SENSE signal, the gate control signal is connected to the single-stage reverse circuit, the single-stage reverse circuit is connected to the NAND gate circuit, and the AND The NOT gate circuit is connected to one input terminal of the compensation output driver, and the WL_EN / BL_EN signal is connected to the other...

Embodiment 3

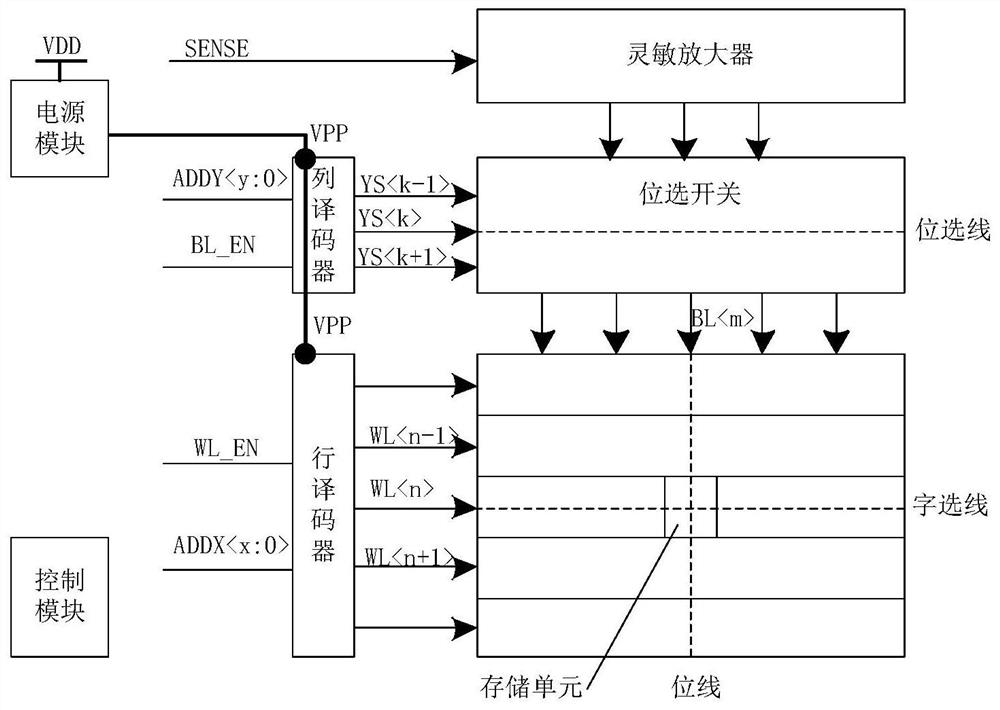

[0035] A memory structure that reduces voltage jitter for read operations, such as Figure 6 As shown, a first charge compensation circuit and a second charge compensation circuit are respectively connected to the row decoder and the column decoder of the original memory structure, and both the first charge compensation circuit and the second charge compensation circuit are implemented by using The charge compensation circuit described in example 1 or embodiment 2;

[0036] The WL_EN signal of the row decoder is connected to the first charge compensation circuit, and the output terminal of the first charge compensation circuit is connected to the read voltage VPP; the BL_EN signal of the column decoder is connected to the second charge compensation circuit. circuit, the output end of the second charge compensation circuit is connected to the read voltage VPP.

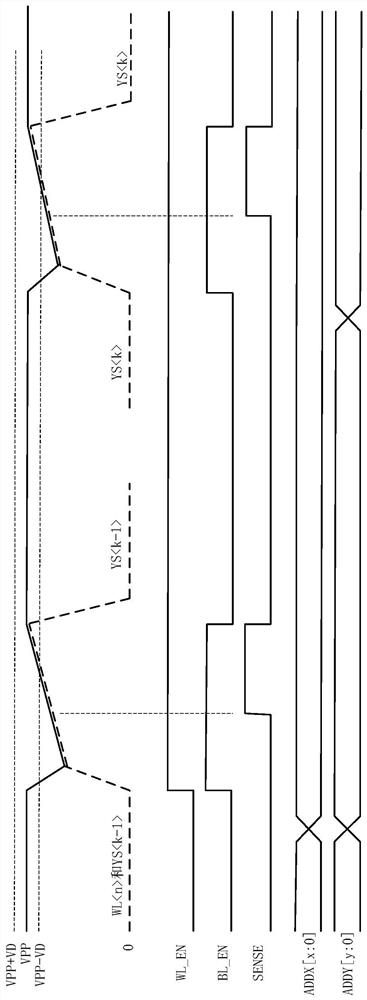

[0037] Figure 7 It is a waveform diagram of the signal voltage during the read operation of the memory provided wi...

PUM

Login to View More

Login to View More Abstract

Description

Claims

Application Information

Login to View More

Login to View More