Programmable keeper for semiconductor memories

A memory and semiconductor technology that is used in static memory, read-only memory, digital memory information, etc., and can solve problems such as high DC leakage current, increased power consumption, and limited VCCmin operation.

- Summary

- Abstract

- Description

- Claims

- Application Information

AI Technical Summary

Problems solved by technology

Method used

Image

Examples

Embodiment Construction

[0026] Preferably, the disclosed semiconductor memories and methods of designing and manufacturing semiconductor memories provide keeper circuits with dimensions optimized for the type of bitcell connected to a particular bitline, e.g., output logic during a read operation A bit cell of 1 or logic 0. A keeper circuit optimized for the type of bit cell connected to the bit line can reduce the power consumption of the semiconductor memory while improving the operating speed and low power, VCCmin operation of the semiconductor memory.

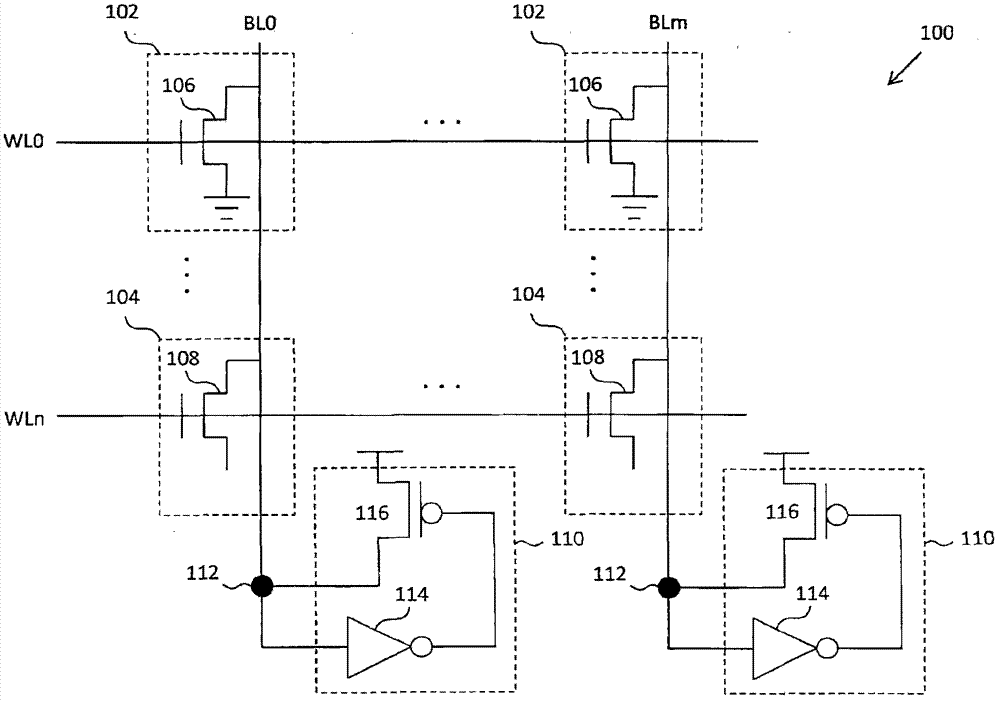

[0027] figure 1 An example of a modified read-only memory ("ROM") array 100 is shown that includes a plurality of programmed 0 bit cells 102 (i.e., bit cells configured to output logic 0) and a number of programmed 1-bit cells 104 (ie, the bit line is configured to output a logic 1 when read). Bit cells 102 and 104 are arranged in number of rows (n) and columns (m). Each bit cell 102, 104 located in a row is connected to a word line ("WL"), and...

PUM

Login to View More

Login to View More Abstract

Description

Claims

Application Information

Login to View More

Login to View More - R&D

- Intellectual Property

- Life Sciences

- Materials

- Tech Scout

- Unparalleled Data Quality

- Higher Quality Content

- 60% Fewer Hallucinations

Browse by: Latest US Patents, China's latest patents, Technical Efficacy Thesaurus, Application Domain, Technology Topic, Popular Technical Reports.

© 2025 PatSnap. All rights reserved.Legal|Privacy policy|Modern Slavery Act Transparency Statement|Sitemap|About US| Contact US: help@patsnap.com